我们如何来修复setup violation?

描述

对于setup violation,大家一定都非常熟悉,网上也有很多相关的资料。今天我们来介绍下对于项目后期ECO阶段,我们如何来修复setup violation.

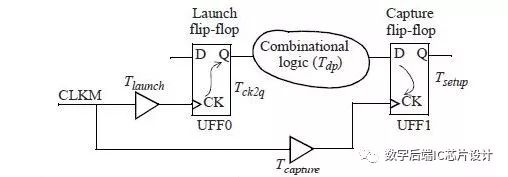

首先我们来回顾一下setup的定义,简单来说,setup检查是为了检查数据传输不能太慢,否则,在目的寄存器的capture edge不能正确的锁存数据。如下图所示:

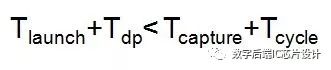

用公式简单表示为:

Tlaunch为launch clock path delay

Tcapture为capture clock path delay

Tdp为data path delay

Tcycle为时钟周期

详细公式可以查看下列文章

【时序分析基本概念介绍

上述公式成立就代表setup没有violation,因此我们可以知道修复setup的主要方法有以下三种:

1. 减小data path的delay

这是我们经常使用的修复setup的方法,但实际上,setup不好修的原因也是在于我们需要在data path上做减法,和hold相反,一般来说,把path变短总是要比把path变长困难许多,这边列举了一些经常使用到一些减小path delay的方法。

1) Vt Swap

通常是指选用Vt更小或者channel length, 一般的,同一种cell会分为HVT, RVT, LVT, SLVT。他们的速度大小按快到慢依次排列为SLVT, LVT, RVT, HVT。 功耗大小正好相反。每种VT cell又会分为不同的channel length,比如C20, C24, C28,C32。 数值越高,速度越慢。因此,在项目功耗允许的前提下,我们可以采用Low Vt的cell来替换High Vt的cell,或者选用小的channel length的cell。 这是修复setup最简单也最常用的方法。

2)插入BUF

Setup violation其实绝大部分原因是由于drv造成的,我们知道,cell的delay其实是根据它的input transition,以及output load查表计算得来。因此,我们解决了cap和slew的问题,timing其实自然也得到了解决。那drv的问题,很多一部分我们可以通过插入buf来修复,比如net连接得太长导致驱动变弱,可以插入buf打断net,来提高驱动;fanout太大,也可以通过插入buf来减少fanout数目。

3)Size up cell

这其实也是一种修复drv的手段,如果某个cell的驱动能力太弱,比较容易产生比较大的delay,因此我们可以通过size up这个cell来提高驱动能力,比如X1的BUF换成X4, X8的等。

但是我们在size up cell前也需要注意该cell的输入/输出transition的变化情况,因为驱动能力强的cell,它本身的load会比较大,可能会造成前一级cell驱动不了它的情况,所以实际的data path情况会比较复杂,不一定换大驱动的cell,delay就会变小。

一般情况下,如果我们看到某个cell的output transition比input transition大很多,那说明这个cell的驱动不够,我们可以尝试size up一下。如下图所示:第一个X1的INV input transition是18.051,而输出transition是66.328。明显地时X1的INV推不动下面的14个fanout,可以考虑提高将X1的INV换成驱动更强的cell。

4)Layer assignment

这也是经常使用的一种手段,通常来说,高层金属电阻较小,net delay也较小。这种现象在先进工艺中更常出现。我们可以将绕在低层的net,删除wire后,设置绕线属性,让它绕在高层。

2. 增加capture clock path delay

这也是经常使用的一种修复setup的方法,也就是我们经常说的手动useful skew的方法。如果我们发现在data path上没有可以明显减小delay的地方时,我们可以采用在capture clock前垫clock buf的手段来增加capture clock path delay,从而起到修复setup violation的目的。

但是,由于这样会动到clock path,所以我们垫buf前还是需要很谨慎的。首先我们得确保从capture clock出发的下一级path是不是有setup slack margin,同时,检查一下到当前该级register的input pin上的有没有hold margin。

3. 减小launch clock path delay

这也是动clock path来修复setup violation的一种方法,不同的我们需要减小launch clock path delay。 这类方法在平时是很少使用到的,原因也是因为减小path delay是很困难的,更何况clock path上用得一般都是最快的cell。理论上我们可以减小clock path的级数来实现,但实际操作起来还是要分析清楚clock的结构。

上述就是一些修复setup violation的理论手段,在实际的ECO过程中,我们考虑得更多的是,如何提高修timing的效率? 毕竟如果timing path fail较多的话,手动修复是极其费力费时的一件事情。

一般signoff工具或者第三方的ECO工具都会自带timing eco的功能,可以先做几轮。 到工具修不动时,可以分析下timing报告,同时应该要通过脚本处理自动产生一个Vt Swap的ECO脚本。因为,Vt Swap动的东西最少,甚至不需要重新eco route和抽spef,直接在signoff工具可以重新报timing看修复结果。

至于剩余的需要手修的path,照着timing report修复时,需要注意以下几点:

1)检查timing path的hold margin。 需要注意的是,一般setup的violation在SS corner下,而hold则出现在FF的corner下面,两者之间有3倍左右的timing variation。所以,检查margin时需要考虑不同的corner影响。如果设计频率过高的话,可能会出现setup和hold相互打架的情况,这时可以考虑提高net delay占的比重,修出margin。

2)尽量动靠近endpoint的cell。因为越往path后面的cell,影响的path数目越少。但有时还是需要考虑path分叉情况再决定修复的方法。

3)修完所有path后,需要在PR工具中对动过的cell重新摆放以及route。

相比hold来说,setup要难修很多,大家在掌握修复方法以后,应该进一步考虑如何通过脚本来提高工作的效率。

-

基于DWC2的USB驱动开发-抽丝剥茧再论SETUP完成标志DOEPINTn.SetUp2023-07-24 4112

-

积分如何来的啊2014-02-05 2999

-

如何使用良好的RTL设计实践进行修复2019-02-14 1839

-

FPGA编译在place步骤显示“unusual high hold time violation detected”2020-10-26 2970

-

MATLAB如何来设计滤波器2021-08-17 1652

-

什么是Setup 和Holdup时间?2007-09-11 11230

-

如何解决“access violation at address”错误2016-09-14 38396

-

如何来手动修复max transition和max capacitance2018-11-02 25044

-

Setup软件安装可执行程序工具免费下载2018-11-13 1971

-

如何修复ECO阶段的Noise Violation2019-01-14 8258

-

图形界面介绍:GUI上的按键是Violation Browser2020-05-19 3589

-

通过解剖一个边沿触发器简要说明setup和hold产生原因2023-07-04 3470

-

什么是Setup和Hold时间?2023-11-17 3902

-

"Access violation" 错误,复位位置,重新打印2025-11-08 732

全部0条评论

快来发表一下你的评论吧 !