fpga 有符号数、无符号数

描述

在设计中,所有的算数运算符都是按照无符号数进行的。如果要完成有符号数计算,对于加、减操作通过补码处理即可用无符号加法完成。对于乘法操作,无符号数直接采用“*”运算符,有符号数运算可通过定义输出为 signed 来处理。

通过“*”运算符完成有符号数的乘法运算。

module ceshi (out, clk, a, b);

output [15:0] out;

input clk;

//通过 signed 关键字定义输入端口的数据类型为有符号数

input signed [7:0] a;

input signed [7:0] b;

//通过 signed 关键字定义寄存器的数据类型为有符号数

reg signed [7:0] a_reg;

reg signed [7:0] b_reg;

reg signed [15:0] out;

wire signed [15:0] mult_out;

//调用*运算符完成有符号数乘法

assign mult_out = a_reg * b_reg;

always@(posedge clk)

begin

a_reg <= a;

b_reg <= b;

out <= mult_out;

end

endmodule

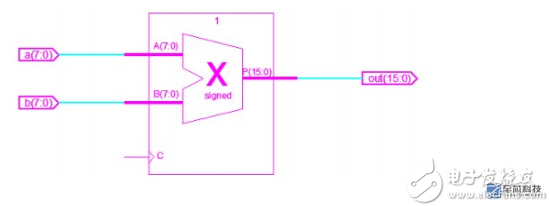

上述程序在 ISE 中的综合结果如下图所示,从其 RTL 结构图可以看到乘法器标注为“signed” ,为有符号数乘法器。

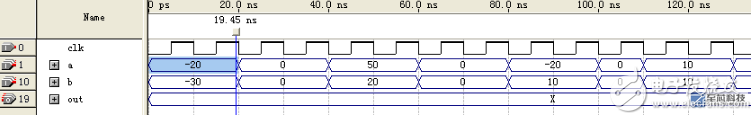

仿真结果图

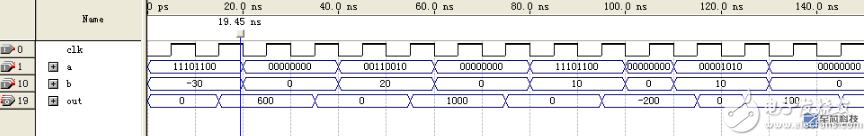

二进制显示的结果

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- FPGA

-

请问AFE5801 AD转换后数字信号是用有符号数还是无符号数表示的?2025-02-11 422

-

采集的数据转换成有符号数的问题2012-05-02 6430

-

原码、补码、反码、有符号数、无符号数概念.pdf2012-11-15 5439

-

有符号数,无符号数,浮点数探讨2015-04-29 6063

-

关于无符号数和有符号数的困惑2013-11-02 6699

-

请问AFE5801 AD转换后数字信号是用有符号数还是无符号数表示?2019-05-24 3583

-

双状态无符号/有符号数据类型2021-01-18 2194

-

AD采样后数据如何在FPGA中转化为有符号数2019-08-11 4150

-

FPGA有符号数乘法操作指南2020-03-08 7498

-

关于verilog中的无符号数和有符号数2020-11-18 18627

-

详细分析Verilog编写程序测试无符号数和有符号数的乘法2021-05-02 8735

-

C语言中无符号数和有符号数的左移和右移2022-01-13 1395

-

FPGA中的有符号数乘法说明2022-02-16 6157

-

verilog中有符号数和无符号数的本质探究2023-12-04 2428

-

verilog中数据的符号属性(有符号数和无符号数)探究根源2023-12-10 3273

全部0条评论

快来发表一下你的评论吧 !