如何利用射频采样ADC来破解宽带难题?

描述

现代电子战(EW)系统开发人员面临着众多挑战,其中包括日益增加的频谱拥堵以及以更高的探测灵敏度对更宽的带宽进行监视等难题。此外,系统开发人员还面临巨大压力,要缩短开发时间,众多现有开发模型难以应对,因而需要各类定制型硬件和固件设计,以便在尺寸、重量和功率三重限制下提升性能水平。

新型每秒千兆采样(GSPS)高速转换器、高性能FPGA和FPGAIP内核已经开始改变现状,为设计师带来了现成的解决方案和可配置的构建模块,助其从容面对新一代挑战。一种采用ADI GSPS ADC并且搭载Altera® FPGA和通道化IP的参考设计将向我们展示,设计师如何在缩短上市时间的条件下,打造出最先进的电子情报和数字RF存储器系统解决方案。

电子战概述

电子战系统可以识别和反击监视与跟踪雷达等电子威胁。电子战系统通常分为电子支援(ES)、电子攻击(EA)和电子保护(EP)三类。

电子支援系统用于拦截和测量信号参数,以识别信号源并进行威胁分析。电子攻击系统会产生干扰信号,以压制真实脉冲。数字射频存储器(DRFM)是一种用于欺骗雷达的欺骗技术。电子保护系统主要用于处理和存储输入信号以构建信号数据库。该数据库是一个持续更新的查询表,用于识别未来雷达系统。传统上,这些系统是在模拟平台上开发的。现代系统的数字化水平更高,可以利用可编程逻辑器件强大的信号处理能力。

在这些系统中,不明目标威胁的探测需要一个可以工作于较宽频段的接收器,以识别威胁并发动对抗措施。典型的电子战系统的工作频率范围是直流至20 GHz。在宽带宽要求以外,实战电子战系统还要求高动态范围、高灵敏度和精确的脉冲特性描述性能,新系统也要以更快的速度、更高的灵敏度监视目标带宽。电子战系统接收到的输入信号可能来自众多不同来源,并且需要识别和区分每一个来源,此时,情况变得更加复杂。在敌方有意为之的干扰以外,不断增加的频谱拥堵,特别是通信基础设施的快速扩张导致的频谱拥堵问题进一步增加了有效探测的难度。

尺寸更小、重量更轻、功率更低的复杂系统使开发周期变得越来越长。然而,新一代现成解决方案和可编程构建模块可为这些挑战提供解决方案。对任何电子战系统来说,两个关键构建模块是模数转换器和实时通道化IP,我们将进一步考察这两个关键构建模块,展示如何应对这些挑战。

电子战系统的ADC瓶颈问题

在许多情况下,高速ADC从模拟域向数字域的过渡是电子支援系统、电子攻击系统和电子保护系统的限制因素,在此,系统架构师往往面临一个难题。成本和系统尺寸最小化通常是重中之重,但系统设计师还必须在提高瞬时监视带宽以最大程度地增加拦截概率的需求,与如何将带内高功率信号降低系统灵敏度的影响最小化之间找到最佳平衡。这些要求在转换器设计和将信号内容耦合到转换器的前端设计方面带来了挑战。即使转换器本身拥有出色的性能,前端也必须能维持信号质量,结果促使设计师不断超越高速ADC的极限,以提高性能、降低成本。

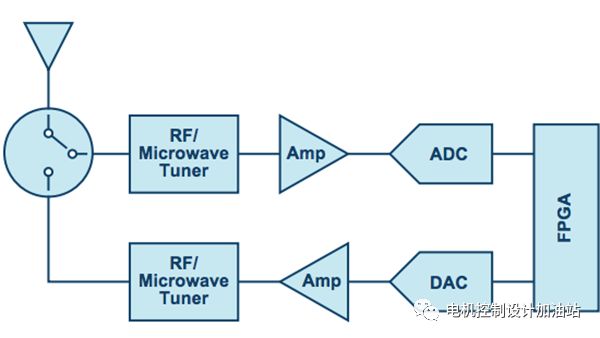

图1所示为一个简单的电子战系统。该系统的主要特性为一个射频接收器(用于下变频和选择要监视的目标频带)、用于转换模数域数据的ADC以及数字信号处理引擎,该引擎通常是一个FPGA,配置为探测、确定、分析和管理目标信号的存储。DRFM和电子攻击系统也包括一个采用高速DAC的相应发射链。

图1. 典型电子战架构信号链

从历史上来看,在增加瞬时带宽的同时维持需要的线性度需要使用多个重叠接收器或一种交错式架构。重叠的接收器各自数字化所需带宽的一部分,并用数字信号处理技术把来自各个通道的数据和可观测频谱重新组合起来。对于交错式架构,一般要搭配校准使用,以便最大限度地减小转换器之间的相差、失调差和增益差。两种方案的实现成本都比较高,但数字信号处理往往会根据实现需求进行定制。

ADI的新型RF采样ADC (如AD9625)为新一代系统提供了解决方案,不但可以提供更大的瞬时带宽,同时还具有更高的线性度,能够维持所需要的灵敏度水平。AD9625是一款2.5 GSPS、12位ADC,可增进高带宽交流性能,在1 GHz输入下,其典型宽带SNR/SFDR分别达到前所未有的57 dB/80 dB。另外,这款ADC还支持确定到达角往往需要的多转换器同步,集成了数字下变频器(DDC)以便抽取和观测输出频谱的较小部分。

AD9625能支持超过3 GHz的小信号模拟带宽,可为系统设计师提供很大的IF定位灵活性。凭借第一和第二奈奎斯特采样选项和超过1 GHz的可用带宽,设计师可以最大化前端接收器架构的性能,实现滤波和系统复杂性的最佳平衡。

ADI推出了支持并行接口和串行接口(包括JESD204B标准)的器件。这对于众多电子战系统的高数据速率和低延迟要求是极其重要的。

为了便于快速制作原型和系统开发,AD9625以VITA 42/FPGA夹层卡(FMC)平台的形式提供(见图2)。该平台提供了一些参考设计,可借以了解如何优化ADC前方的信号调理以实现性能优化;同时,平台还可确保ADC与处理单元之间的数据处理接口拥有充足的带宽,以便在仍然使用CoT架构的条件下,支持来自转换器的实时全速率数据传输需求。结果打造出一款高效的架构,集成2.5 GSPS ADC COTS解决方案,以最小尺寸提供高速导管。

图2. AD9625 (2500 MSPS、12位FMC板,带同步支持)。(PN:AD-FMCADC2-EBZ)

通道选择器概述

尽管电子攻击系统、电子支援系统和电子保护系统中的信号都各有特点,但它们都有一个共同的组件,即数字通道化接收器,也称通道选择器。通道选择器把一个宽带宽拆分成小带宽,以便把目标信号与噪声和干扰信号分开,从而在单个子通道中可靠地检测到低SNR和时间敏感信号。多数数字通道化接收器都由一个滤波器组和快速傅里叶变换(FFT)组成。

作为设计工程师,这里面临的一个挑战是,每次设计或升级新的电子战系统时,通常都要求开发更加复杂的通道选择器。这是因为新设计通常会导致必要的硬件升级,以支持速率更高的转换器和更高的处理性能,以应对不断变化的全球威胁。为了加快通道选择器的开发步伐,降低内部研发(IRAD)成本,Altera开发了一款超高采样速率的FFT IP和FIR滤波器IP内核,能够处理多-GSPS转换器输入。这些IP内核可根据多种输入参数,优化您的解决方案,如图3所示。

图3. Altera超高采样速率FFT配置

图4. 一般电子战系统框图

图4通过一般电子战系统框图描述了通道选择器的作用,在该图中,先对数字化输入射频(RF)宽带信号进行下变频和数字化处理,然后馈入通道化接收器之中。对各通道的输出进行信号检测和估算,以便把威胁信号与中立方和友方信号分辨开来。一旦发现威胁且有数据作为支撑,某些电子战系统就会通过干扰对抗威胁。在此过程中,接收器可能会产生各种干扰信号。

在敌方发射机中,这些干扰信号可能表现为陷波白噪声或再生虚假反射信号(即DRFM)。干扰信号通过反相通道选择器,后者的作用是重构宽带反射信号。反射信号在上变频回敌方发射机之后再发射。

硬件演示

项目展示的是ADC接口和通道选择器功能。一个信号发生器产生一个正弦信号音,作为AD9625的输入。AD9625 ADC输出端通过行业标准FMC接口连接至Arria-V SoC开发套件。JESD204B标准定义了各种通道配置条件下逻辑器件的数据速率。在本演示中,JESD204B接口配置为使用8通道收发器模式,如图5A和图5B所示。

通过JESD204B接口接收的样本馈入通道选择器IP中,后者配置为用16条输入线并行接收16个样本(图4中的参数M)。根据FFT点的数量,把一个全FFT帧分为多个时隙。例如,一个1024点FFT需要1024/16 = 64个时隙。滤波器组系数和FFT处理级会根据时隙自动切换。

通道选择器IP是用DSP高级版生成器(DSPBA)开发的,这是来自Altera的一款基于模型的设计流工具。借助该工具,信号处理工程师可以在MATLAB/Simulink环境中设计、评估和验证其算法。

当算法为最优时,DSPBA会生成可以部署在Altera FPGA上的代码。通道选择器输出存储在片内存储器中,并通过Altera系统在环(SIL)工具进行验证。SIL用一个MATLAB API来触发片内寄存器,开始记录,以用于数据可视化。一旦触发,则会对FFT处理执行一次迭代,并把产生的数据存储到片内SRAM中。MATLAB API通过Altera Avalon存储器图把数据从SRAM提取到MATLAB主机中。上传到MATLAB之后,则会在屏幕上绘制样本图。

IP的集成是在Qsys中完成的。Qsys是Altera推出的一款集成工具,通过提供集成框架,可以大幅缩短开发流程。运用图形用户界面即可实现层级式IP重用和互联基础设施。

图5A. AD9625通过JESD204B接口连接Altera Arria V

图5B. 面向Altera系统在环的通道选择器JESD204B输入和Avalon存储器图

创建一个Qsys项目,以集成通道选择器IP和JESD204B IP。除了通道选择器IP集成以外,项目还集成了控制功能,以支持连接ADC的SPI配置接口。

通道选择器可以通过MATLAB设置脚本轻松切换为不同的FFT大小。这种灵活性为将来的升级路径提供了保障,同时还有可能在不同系统配置之间实现设计的重复利用。例如,图6展示了来自SIL的4096点FFT输出。

图6. 4k-FFT通道选择器通过SIL的输出图示例

结论

通过新一代高速转换器打造的解决方案可以提供更高的瞬时带宽而不牺牲系统灵敏度,同时还能在频率规划方面提供更大的灵活性,或者消除前端RF带上的下混频级的必要性。然而,在1 GHz范围内实现带宽数据分析可能对高性能系统的设计造成挑战。

为了解决这个问题,可以利用通道选择器来分析这些宽带宽同时维持高性能。这些新型GSPS RF ADC加上新型可配置通道选择器IP内核为新一代系统设计师提供了一种更快的解决方案,可以很好地适应不断变化的电子战环境。

-

基于射频采样ADC破解宽带难题2018-10-25 3281

-

射频采样ADC输入保护:这不是魔法2018-11-01 3231

-

用于实现12.8GSPS采样率的交错射频采样模数转换器的实用示例2022-09-15 1284

-

如何完善您的射频采样解决方案2016-12-26 2875

-

如何保护射频采样ADC的输入?2017-11-22 1462

-

如何使用射频采样ADC破解宽带难题2020-10-14 543

-

如何保护射频采样ADC的输入2020-09-29 857

-

射频接收系统:中频采样和IQ采样的比较和转换2020-12-02 11836

-

利用FPGA控制ADC0809采样电压2021-09-28 1493

-

中频采样和IQ采样的比较分析2022-07-28 5047

-

AN2668_通过过采样来提高STM32的ADC精度2022-11-21 991

-

利用RF采样ADC解决宽带难题2023-01-09 2140

-

AFE7444IABJ四通道宽带射频采样模拟前端 (AFE)的中文资料2021-12-16 2705

-

ADC12DJ5200-EP射频采样千兆采样模数转换器(ADC)数据表2024-07-15 423

-

ADC08DJ5200RF射频采样千兆采样模数转换器(ADC)数据表2024-07-19 399

全部0条评论

快来发表一下你的评论吧 !