FPGA 实现 高斯滤波

描述

1、高斯滤波器的实现方式

方法1:与高斯核直接进行卷积实现,这样使用的资源和乘法器 加法器都会很多。例如3*3窗口的滤波核进行卷积运算,一共需要进行9次乘法和8次加法。

方法2:采用两个一维的高斯滤波进行两次滤波,即先对行进行一维滤波,然后再对列进行一维滤波,这样计算简单,降低了复杂度。

比较两种方法,采用第二种实现方法。

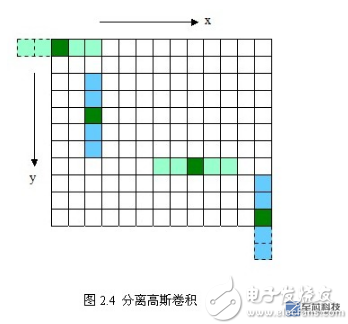

2、行列分离计算方法

采用下图的计算方法,其中对边界的处理填0处理。

3、实现结果

always

begin

#10 clk = ~clk; //100Mhz

end

时间:5201520000ps=5.2ms

always

begin

#5 clk = ~clk; //200Mhz

end

时间:2600780000ps=2.6ms

4、与仿真比较

如下图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- FPGA

-

基于Matlab与FPGA的双边滤波算法实现2025-07-10 4805

-

图像高斯滤波的原理及FPGA实现思路2024-12-07 3082

-

高斯滤波的基本原理有哪些2024-09-29 2871

-

基于FPGA图像处理的高斯模糊实现2023-10-26 1766

-

高斯响应滤波器设计2023-05-11 3502

-

高斯滤波器的工作原理及实现方法2022-04-27 8442

-

FPGA中高斯滤波算法的实现2021-10-29 6427

-

简谈FPGA实现高斯滤波2021-07-21 3908

-

高斯滤波器的原理和实现2019-09-01 9329

-

高斯滤波简介,高斯滤波性质及应用2018-04-09 26674

-

基于FPGA灰度图像高斯滤波算法的实现2018-02-20 8095

-

高斯滤波器在实时系统中的快速实现2009-12-08 1269

全部0条评论

快来发表一下你的评论吧 !