通过LPM_ROM模块和VHDL语言为核心设计多功能信号发生器

电子说

描述

以FPGA芯片为载体, 通过QuartusII 的LPM_ROM 模块和VHDL 语言为核心设计一个多功能信号发生器,根据输入信号的选择可以输出递增锯齿波、递减锯齿波、三角波、阶梯波和方波等5 种信号,通过QuartusII 软件进行波形仿真、定时分析,仿真正确后,利用实验板提供的资源,下载到芯片中实现预定功能。

信号发生器又称为波形发生器, 是一种常用的信号源,广泛应用于电子电路、通信、控制和教学实验等领域。它是科研及工程实践中最重要的仪器之一, 以往多用硬件组成,系统结构比较复杂,可维护性和可操作性不佳。随着计算机技术的发展,信号发生器的设计制作越来越多的是用计算机技术,种类繁多,价格、性能差异很大。用FPGA 或CPLD 来实现,它的优点是可以进行功能仿真,而且FPGA 和CPLD 的片内资源丰富,设计的流程简单。用FPGA 所构成的系统来产生波形信号,这个系统既能和主机系统相连,用相应的上层软件展示波形信号, 又方便程序的编写, 而且还有A/D0809接口可以产生模拟信号的输出和外面的示波器相连。

1 正弦信号发生器的LPM 定制

正弦信号发生器由计数器或地址发生器(6 位)、正弦信号数据ROM (6 位地址线,8 位数据线, 含有64 个8 位数据, 一个周期)、原理图顶层设计和8 位D/A ( 实验中用DAC0832 代替)。

其框图如图1 所示。其中信号产生模块将产生所需的各种信号,这些信号的产生可以有多种方式,如用计数器直接产生信号输出,或者用计数器产生存储器的地址,在存储器中存放信号输出的数据。信号发生器的控制模块可以用数据选择器实现, 用8 选1 数据选择器实现对5 种信号的选择。

图1 信号发生器结构框图

最后将波形数据送入D/A 转换器,将数字信号转换为模拟信号输出。用示波器测试D/A 转换器的输出,可以观测到5 种信号的输出。

1.1 定制初始化数据文件

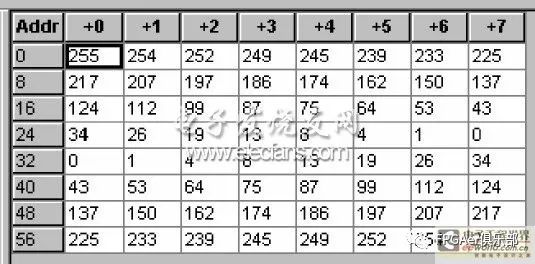

QuartusII 能接受的LPM_ROM 模块中的初始化数据文件的格式有两种:。mif 格式文件和。hex 格式文件。实际应用中只要使用其中一种格式的文件即可。下面采用。mif 格式文件,调出产生ROM 数据文件大小的选择窗。根据64 点8 位正弦数据的情况,可选ROM 的数据数Number 为64,数据宽Word size 取8 位。单击OK 按钮,将出现图2 所示的空的。mif数据表格,表格中的数据格式可通过鼠标右键单击窗口边缘的地址数据弹出的窗口选择。

图2 .mif 数据表格

将波形数据填入mif 文件表中也可以使用QuartusII 以外的编辑器设计MIF 文件,其格式如下:

#include

#include "math.h"

main()

{int i;float s;

for (i=0;i<1024; i++)

{ s = sin(atan(1)*8*i/1024);

printf("%d : %d;\n",i,(int)((s+1)*1023/2)); }}

把上述程序编译成程序后, 可在DOS 命令行下执行命令:

romgen > sin_ rom. mif;

1.2 定制LPM 元件

打开Mega Wizard Plug_In Manager 初始对话框, 选择Create a new custom… 项。单击Next 按钮后,选择Storage 项下的LPM_ROM, 再选择ACEX1K 器件和VHDL 语言方式;最后输入ROM 文件存放的路径和文件名:F:\sing_gnt\data_rom (定制的ROM 元件文件名),单击Next 按钮,选择ROM 控制线、地址线和数据线。这里选择地址线位宽和ROM 中数据数分别为6 和64; 选择地址锁存控制信号inclock。

对于地址信号发生器的设计。方法一:用VHDL 语言设计6 位计数器,产生其元件符号;方法二:仍采用LPM 定制的方法。

1.3 完成顶层设计

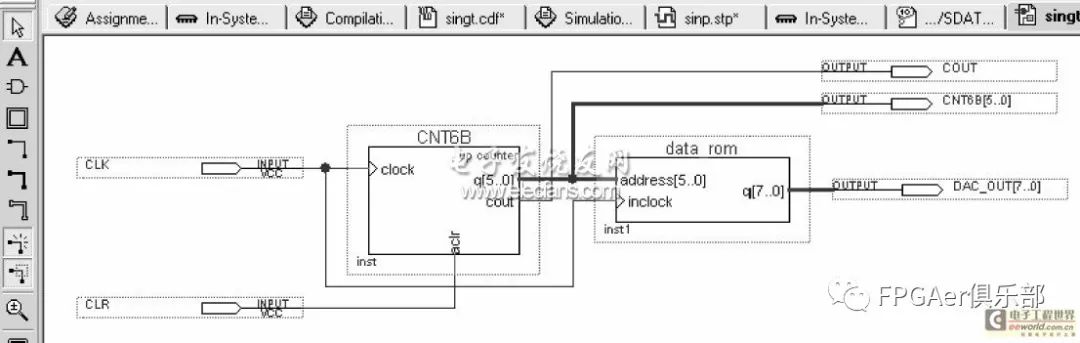

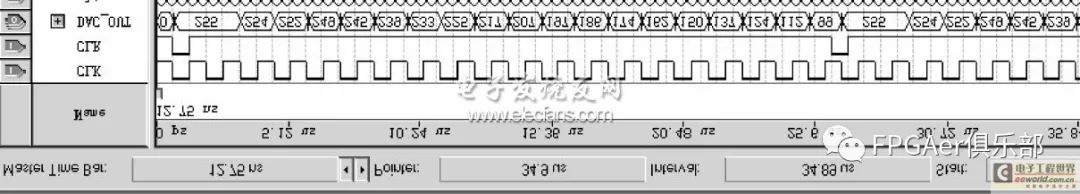

按图3 画出顶层原理图,然后进行编译,波形仿真如图4所示。

图3 简易正弦信号发生器顶层电路设计

图4 当前工程仿真波形输出

对当前设计通过执行Quartus II 的命令Create ∠ Update/ Create Symbol Files for Current File,可以为设计电路建立一个元件符号,以便被顶层设计多功能信号发生器所调用。

2 其他信号部分原程序

其他各信号发生器可参照正弦信号发生器的设计方法设计或直接采用VHDL 硬件描述语言进行设计。

LIBRARY IEEE;--递增锯齿波的设计

USE IEEE.STD LOGIC 1164.ALL;

USE IEEE.STD LOGIC UNSIGNED.ALL;

ENTITY signal2 IS --递增锯齿波signal1

PORT(clk,reset:IN std_logic;--复位信号reset, 时钟信号clk

q:OUT std_logic_vector (7 DOWNTO 0));--输出信号q

END signal2;

ARCHITECTURE b OF signal2 IS

BEGIN

PROCESS(clk,reset)

VARIABLE tmp:std_logic_vector(7 DOWNTO 0);

BEGIN

IF reset='0' THEN

tmp:="00000000";

ELSIT rising_ege(clk)THEN

IF tmp="11111111"THEN

tmp:="00000000";

ELSE

tmp:=tmp+1; --递增信号的变化

END IF;

END IF;

q<=tmp:

END PROCESS;

END b;

LIBRARY IEEE;--方波的设计

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity signal5 is --方波signal5

PORT(clk,reset:in std_logic; --复位信号reset,时钟信号clk

q:out std_logic_vector (7 DOWNTO 0)); --输出信号q,8 位数字信号

END signal5;

ARCHITEECTURE a OF signal5 IS

SIGNAL; a:std_logic;

BEGIN

PROCESS(clk,reset)

YARIABLE tmp:std_logic_vector(7 downto 0);

BEQIN

IF reset='0' then

a<='0';

elsif rising_edge(clk)THEN

IF tmp="11111111" THEN

tmp:="00000000";

ELSE

tmp:=tmp+1;

END IF;

if tmp<="10000000" then

a<='1';

else

a<='0';

END IF;

END IF;

END PROCESS;

PROCESS(clk,a)

BEGIN

IF rising_edge(clk)THEN

IF a='1' THEN

q<="11111111";

ELSE

q<="00000000";

END IF;

END IF;

END PROCESS;

END a;

3 顶层电路的设计

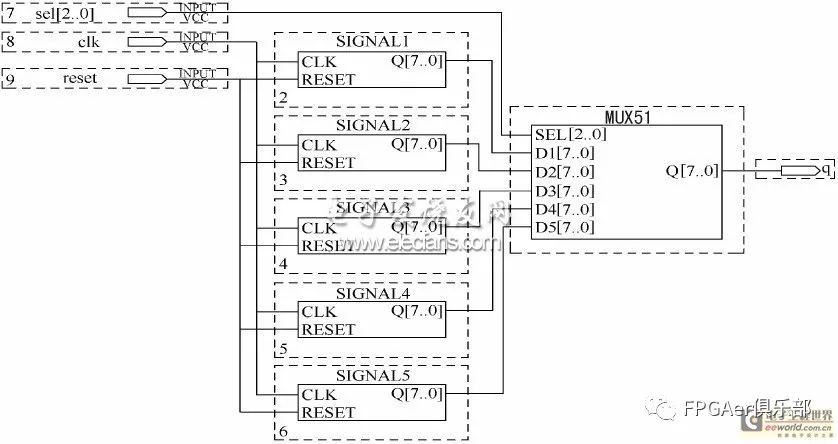

将上述6 个模块生成符号,供顶层电路调用。这些模块分别是:递减锯齿波信号产生模块signall、递增锯齿波信号产生模块signal2、三角波信号产生模块signal3、阶梯波信号产生模块signal4、方波信号产生模块signal5 和数据选择器mux51。顶层电路的连接如图5 所示。

图5 信号发生器顶层电路

4 D/A 转换器的连接

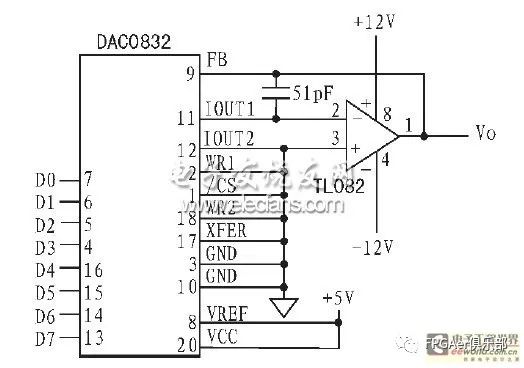

选择一个D/A 转换器,将数据选择器的输出与D/A 转换器的输入端连接。D/A 转换器的可选范围很宽,这里以常用的DAC0832 为例。DAC0832 的连接电路如图6 所示。

图6 DAC0832 的连接电路

5 实现与测试

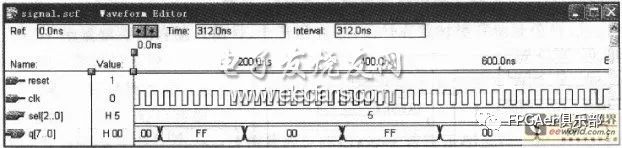

信号发生器顶层电路的仿真波形如图7 所示,这里只就输入选择信号等于5 时的情况进行仿真,此时输出波形是方波,输出的数字信号为周期性的全0 或全1。

图7 信号发生器顶层电路的仿真波形

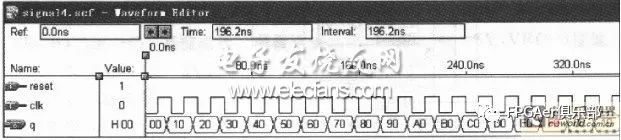

信号发生器的底层电路模块也可以分别进行仿真,例如对阶梯波信号产生模块signal4 进行仿真,仿真波形如图8 所示,输出的数字信号为阶梯状变化。

图8 阶梯波信号产生模块signal4 的仿真波形

6 结束语

硬件电路设计主要是设计相关模块的设计思想的可视化,是相关模块的电路图的汇总和其相关仿真波形的集锦,该部分条理清晰,思路明确,从中我们可以清晰地看到该设计方案的具体模块和整个设计的原理结构实图;程序设计这一部分主要阐述该设计的设计方法与设计思想,进一步从软件设计上揭示设计构思,主要包含了整个设计所用到的模块的硬件描述语言的设计, 本文设计思路清晰,通过QuartusII 软件进行波形仿真成功,特别是正弦信号发生器的LPM 定制对于编程不是特别强的人员提供另一种途径来实现,加深理解EDA 的层次设计思想,很好的把握住了教学的改革方向,更好的锻炼了学生理论联系实践的能力。

-

多功能信号发生器2019-08-06 4278

-

基于CPLD和单片机的多功能信号发生器2016-08-25 2202

-

CPLD LPM_ROM or LPM_RAM 的使用2017-05-18 4901

-

正弦波信号发生器VHDL源代码2008-01-02 2181

-

Instantiating LPM in VHDL2009-09-13 495

-

多功能波形发生器VHDL程序与仿真2008-06-27 3091

-

微型DDS信号发生器2011-05-05 887

-

基于FPGA LPM多功能信号发生器设计2011-08-15 993

-

基于FPGA的信号发生器设计2011-09-26 9278

-

使用FPGA实现LPM ROM创建的教程说明2020-11-02 1651

-

多功能波形发生器的VHDL程序与仿真资料免费下载2021-01-20 971

-

FPGA中LPM_ROM设计快速实现2021-08-04 848

-

DG4000系列多功能信号发生器介绍2023-03-02 2000

-

如何设计并实现一个基于FPGA的多功能信号发生器?2023-08-25 3634

-

信号发生器如何输出直流信号?2024-05-20 4955

全部0条评论

快来发表一下你的评论吧 !