LUT如何构成逻辑函数

电子说

描述

初识FPGA CLB之LUT实现逻辑函数

一.概述

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习LUT如何构成组合逻辑。

二.LUT实现原理

LUT,中文名字叫做查找表,其原理其实也就是一个一个查找表,根据输入去找到相应位置的信号,然后做输出。说白了就好像一个小容量的ROM,把输入当作地址信号,对LUT里面预存的内容进行寻址。

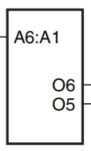

7系列的FPGA的LUT有6个输入端口(A1-6),然后有两个输出端口(O5,O6)。下图是SLICEL里面的LUT。

其可以实现6输入的布尔组合逻辑函数,输入信号为A1,A2,A3,A4,A5,A6,输出端口为O6。如下

O6=f(A1,A2,A3,A4,A5,A6)

其实现方式就是将输入(A1,A2...A6)对应的输出在LUT里面预存好(这一步在我们用bit文件配置FPGA时实现),然后把输入信号当作地址信号去把对应的输出信号调出来。

同样其还可以构成两个5输入的布尔组合逻辑函数,其中这两个函数共用5个输入信号(A1,A2,A3,A4,A5),A6被拉高,O5,O6分别是两个布尔逻辑的输出。

O5=f(A1,A2,A3,A4,A5)

O6=f(A1,A2,A3,A4,A5)

故这也相当于实现的是一个5输入2输出的逻辑函数。

[O5,O6]=f(A1,A2,A3,A4,A5)

三.总结与提升

总结一下,就好比单个LUT里面可以预存 2^6=64个结果。那么单个LUT可以实现

(1)输入信号最多为6bit,输出信号为1bit的的布尔逻辑函数;

(2)输入信号最多为5bit,输出信号为2bit的逻辑。

一个SLICE里面有四个LUT故最多可以预存的输出信号个数为 2^6*4=2^8。

因此在一个SLICE里面,借助选择器将多个LUT进行互连,可以实现输入数,输出数最多为如下所示的逻辑。

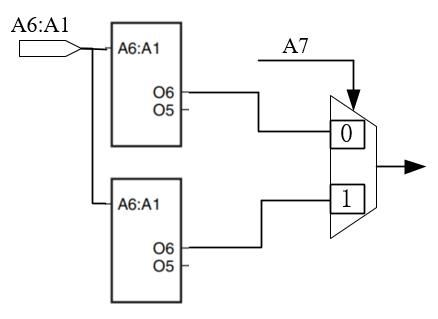

(1)2个LUT通过互连可以构成7bit输入,单bit输出的逻辑。实现方式为两个LUT的输入信号A1,A2,A3,A4,A5,A6接到一起,输出信号经过选择器选择输出,选择器的选择信号也是逻辑函数的一个输入信号。

(2)4个LUT通过互连可以构成8bit输入,单bit输出的逻辑。实现方式大家可以根据上面的实现方式自行推理。

(3)2个LUT通过互连可以构成6bit输入,2bit输出的逻辑。实现方式自行推理。

(4)4个LUT通过互连可以构成7bit输入,2bit输出的逻辑。实现方式自行推理。

超过8输入的布尔逻辑就需要多个SLICE来实现。

-

LUT是什么构成的?FPGA里的LUT有什么作用?2023-06-28 5114

-

关于FPGA四输入、六输入基本逻辑单元LUT的一点理解2023-05-25 4695

-

请问一下FPGA的LUT到底是如何实现逻辑功能的?2023-04-23 3208

-

初识FPGA CLB之LUT实现逻辑函数2023-03-13 4868

-

物理可级联的LUT的优势在哪?2021-03-27 4438

-

FPGA架构的学习教程之深入理解LUT2020-12-29 2139

-

请问如何将Memory LUT用作逻辑LUT?2020-08-05 2270

-

逻辑NOT函数功能介绍2019-06-23 10350

-

如何在LUT和逻辑元件之间以及逻辑元件和逻辑单元之间进行交换2019-01-08 2661

-

解析逻辑函数式的处理2012-09-12 1148

-

标准形式逻辑函数2010-09-19 3200

-

逻辑代数和函数化简2010-05-26 817

-

逻辑代数与逻辑函数2009-09-01 1235

-

逻辑函数与逻辑问题的描述2009-04-06 1785

全部0条评论

快来发表一下你的评论吧 !