UG1292使用之初始设计检查使用说明

电子说

描述

前言

最近有网友对小编说:xilinx时序收敛完全不会用,不知道工具在干啥,一直都在瞎点,报告一直是瞎看。

好消息是,Xilinx发布了一篇新文档ug1292。这个文档把ug949中时序收敛的相关内容单独提取出来,用最简练的语言介绍了时序收敛的方法。ug1292是时序收敛的一个快速参考手册,也就是看完之后你可以快速知道怎么用工具实现时序收敛。

UG1292百度云链接:

链接:https://pan.baidu.com/s/1FOZCRzDogrGeuIMDXkaeaA

提取码:gku9

ug1292 总体了解

这个手册只有十页内容,一天就可以看完,每一页都有流程图或表格都可以指导使用者更好的操作。该手册每一页都是一个章节,哪个地方不懂直接翻到该页仔细看,建议看英文原版,目录翻译如下:

手册目录

第1页——初始设计检查流程

第2页——时序基线流程

第3页——分析建立时间违规流程

第4页——保持时间违规解决

第5页——减少逻辑延时流程

第6,7页——减少网络延时流程

第8页——改善时钟偏斜流程

第9页——改善时钟不确定性流程

第10页——FAILFAST报告概览

从目录和内容其实可以看出来,xilinx的理念是——一切问题尽量在设计初期干预。越是在设计初期考虑的全面,后期的工作会越顺利,也就是时序是设计出来的,不是测试出来的!所以前期多花时间设计好时序,可能最开始进度慢一些,但是后期会避免很多不必要的问题。如果前期设计的不周全导致后期项目不停打补丁而导致维护成本增加得不偿失。所以各位老司机设计前期请慎重,后期各种问题堆起来可能根本就解决不了,就算能解决,后面接手维护的人内心也只能呐喊:臣妾做不到啊!!

设计期初可以从以下角度去考虑时序方面的问题:

初始设计检查

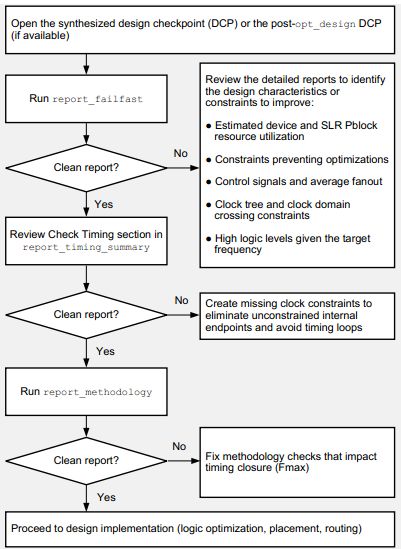

UG1292第一页是针对综合后或者opt_design阶段的使用说明。vivado的基本流程有5步(其实不同策略可以更多,具体使用方法和好处以后讲),分别是synth_design, opt_design, place_design, route_design, write_bitstream,除了最后生成bit外每一步都可以生成一个时序报告,帮助分析定位问题或者优化设计做出指导。而UG1292第一页是讲opt_design阶段如何去利用vivado提供的工具和报告分析和定位问题的。

UG1292初始设计检查流程图

简单地说只需要下面几步。

初始设计检查步骤

1. opt_design阶段生成的dcp(design check point)

2. 用report_failfast生成failfast报告

3. 用report_timing_summary生成时序报告

4. 用report_methodology可以生成UFDM报告

failfast报告作用

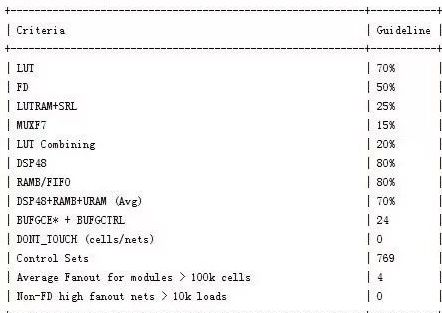

failfast作用是给出各类资源利用率的推荐上限和实际上限比值,根据这两个比值的对比可以知道哪里是时序的瓶颈,需要自己去检查的。下面是K7某个芯片各个资源的推荐利用率:

如果某项实际使用指标超过了指导指标,在status一栏(Guideline旁边一栏没有截图出来)里面会有REVIEW的字样,表示这里你要检查下,这里会对时序有一定影响需要你人为去评估,但是不以为着一定要改。比如DONT_TOUCH约束推荐是一条都不要用,然而有的特殊情况处理,人是有把握比机器更好的,所以为了不让编译器去修改,就加这条约束,但是编译器不确定你是否有能力把握,或者是否注意到这一点,所以会提示你,如果你的设计需要必须这样,并且有把握那么可以不做任何修改的。

时序报告作用

这里生成的时序报告看路径延迟之类的是没有任何意义的,因为还没有布局布线。这里主要检查以下几点。

check_timing下面有没有未约束路径,loop有没有,已经约束的是否合理,比如本来是125M时钟实际约束是120M。

异步时钟域路径约束是否合理。

UFDM报告

UFDM(UltraFast Design Methodology)报告主要作用是报告RTL级代码检查,IP使用分析等方面的报告,主要关注报告里面Bad Practice 的项目即可。

-

UltraFast设计方法时序收敛快捷参考指南(UG1292)2023-09-15 455

-

DC1292A DC1292A评估板2021-09-03 121

-

PCA9685使用说明2021-08-11 3550

-

常用的API及使用说明2021-03-30 3165

-

深度解析ug1292:降低布线延迟2018-10-30 5233

-

ug1292深度解析2018-10-12 4076

-

ug1292时序收敛快速参考手册2018-10-09 3904

-

iccavr使用说明2012-04-06 7628

-

LX3照相机使用说明书2010-08-29 922

-

三星53V MP3使用说明书(用户手册)2010-01-12 554

-

如何安装ug5.0以及ug5.0怎么安装2009-02-06 3548

-

ImageCraft ICCAVR 的中文使用说明2008-10-27 5716

-

PCBNavigator的使用说明2008-05-11 9246

全部0条评论

快来发表一下你的评论吧 !