FPGA时序的基本概念,RTL项目的设计探索

电子说

描述

对于FPGA而言,时序收敛是一个很重要的概念。在我看来,时序约束是必要的,但不是在最重要的,我们应该在设计初始就考虑到时序问题,而不是完全的靠约束来获得一个好的结果。

在军事和航空领域,工程师面临的挑战越来越严峻,例如延迟要求、带宽要求、在极端气温下使应用达标,以及紧迫的工程进度。在更高的抽象层级上工作,设计会更加清晰简洁,报错和纠错也会更少。但是,这个方法一般会以牺牲性能为代价。要想在 FPGA 设计中实现高性能,需要手动优化 RTL 代码。而在 C 到 RTL 开发环境中直接生成的RTL代码,往往是不达标的.

1. FPGA时序的基本概念

FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是FPGA外部的芯片,可能是FPGA内部的硬核。

对于FPGA design来说,必须要关注在指定要求下,它能否正常工作。这个正常工作包括同步时序电路的工作频率,以及输入输出设备的时序要求。在FPGA design内部,都是同步时序电路,各处的延时等都能够估计出来,但是FPGA内部并不知道外部的设备的时序关系。所以,Timing constraints包括:

输入路径(Input paths )

寄存器-寄存器路径(Register-to-register paths )

输出路径(Output paths )

例外(Path specific exceptions )

这正好对应了上图中三个部分,Path specific exceptions 暂时不提。

Input paths对应的是OFFSET IN约束,即输入数据和时钟之间的相位关系。针对不同的数据输入方式(系统同步和源同步,SDR和DDR)有不同的分析结果。

Register-to-register paths 对应的是整个FPGA design的工作时钟。如果只有一个时钟,那么只需要指定输入的频率即可。如果有多个时钟,这些时钟是通过DCM,MMCM,PLL生成的,那么显然ISE知道这些时钟之间的频率、相位关系,所以也不需要我们指定。如果这些不同的时钟是通过不同的引脚输入的,ISE不知道其相位关系,所以指定其中一个为主时钟,需要指定其间的相位关系。

Output paths对应的是OFFSET OUT 约束,和OFFSET IN约束很类似,不过方向相反。

2. 找到合适的 FPGA 工具设置

尽管工程师们很清楚已有 FPGA 工具的参数设置,但是很多时候并没有完全把这些设置的功能发挥出来。一般而言,这些设置只有在设计无法达到时序要求的时候才会用到。而且,对于已经达到性能目标的设计来说,如果好好利用这些设置,性能再提升10%-50%也是完全有可能的。难点在于,各种 FPGA 工具一般会有30-70个综合和布局布线的设置选项,从这些选项中选择合适的那一组设置组合如同大海捞针。幸好,目前已经有些工具可以控制并运行设计探索,而且整套流程是自动化的,也十分严谨。

最后的一个难题,是计算资源的匮乏。传统的嵌入式应用都是在单一电脑上设计的,但是运行多个编译需要更多的计算能力,这样就会牺牲更多的时间。如果可以并行运行编译的话,那么周转时间就会短很多。

3. 优化高层次设计

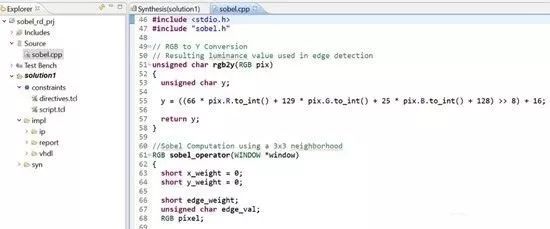

市面上已经有工具可以将设计性能提升50%并且不改变 RTL 代码了。如下图所展示的是设计探索非常好的一个例子:在视频处理的设计中,进行 Sobel Filter Implementation。该设计的目标器件为一个 FPGA 搭载双核 Arm® Cortex®-A9 MPCore™。

该设计的时钟周期为5.00ns或者200MHz。根据时序预估,它的时序还差506ps,也就是据目标速率还差10%或181MHz,如下图

Intime在不改变 C++代码的情况下,工程师把设计输出为 RTL 代码。通过使用一种探索工具,工程师打开项目(xpr),然后并行运行不同 FPGA 工具参数的编译来优化设计。

在两轮优化,15次编译之后,该设计达到了性能目标,200MHz,而且没有修改源代码。如下图:

这个案例并不是说这种优化只能在高层次设计中进行。其实,只要是RTL代码都有可能提升性能。

4. RTL 项目的设计探索

软件无线电 (SDR) 是另一个可以从时序收敛工具中获益的应用。在这个案例中,参考设计直接用 RTL 代码创建。这是一个高性能,高集成度的射频 (RF) 捷变收发器 (Agile Transceiver),为3G和4G基站的应用而设计。该设备把一个拥有灵活混合信号基带单元的射频前端 (RF Front End),和集成频率合成器 (integrated frequency synthesizers)相结合,再把处理器加上一个可配置的数字界面。

开始的时钟周期是4ns 或250MHz,并且参考设计默认时序达标。为了让这个设计时序失败,工程师把时钟周期设置成激进的2ns,新的目标速率为500MHz。在这种情况下,设计时序离达标就会差246ps,并以445MHz 运行。

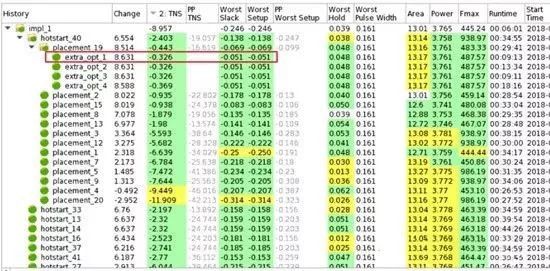

在同样的情况下,不改变RTL,该设计可以通过探索多种 FPGA 工具参数来优化。优化过程为三轮,60次编译。

结果显示,最终 WNS 从-246ps 提升到-0.051ps,提升了79.2%,相当于时钟周期为487MHz 以及9.4%的最大频率提升。如下图:

5. 让性能更进一步

随着科学技术的发展,电子器件会变得越来越复杂,要求也越来越高,这是大势所趋。新的 FPGA 软件科技和方法会帮助我们提升质量、效率,满足我们的需求。尽管 FPGA 设计的潜能尚未完全被了解,但工具参数的探索可以减少高层次设计的性能牺牲,从而保证项目完成地又快又好。工程师们会在使用工具探索 FPGA 设计参数选项上,越来越熟练。这些工具也会在设计中大放异彩。

有需要试用intime软件者,请加群提交申请即可。

-

Fpga Cpld的基本概念2012-08-20 0

-

FPGA功耗的基本概念,如何降低FPGA功耗?2021-04-30 0

-

FPGA高级班前言基本原理基本概念2010-02-09 450

-

时序分析中的一些基本概念2017-02-11 4256

-

时序分析基本概念介绍——时序库Lib,除了这些你还想知道什么?2017-12-15 12004

-

详细介绍时序基本概念Timing arc2018-01-02 24371

-

时序分析和时序约束的基本概念详细说明2021-01-08 1380

-

时序设计基本概念之collection2021-11-26 3754

-

FPGA设计中时序分析的基本概念2022-03-18 2656

-

静态时序分析的基本概念和方法2023-06-28 1469

-

介绍时序分析的基本概念lookup table2023-07-03 1456

-

介绍时序分析基本概念MMMC2023-07-04 2508

-

时序分析Slew/Transition基本概念介绍2023-07-05 3066

-

时序分析基本概念介绍—Timing Arc2023-07-06 3346

全部0条评论

快来发表一下你的评论吧 !