三个命令生成的报告中均可显示Clock Skew的具体数值

电子说

描述

过大的Clock Skew也可能导致时序违例,尤其是其数值超过0.5ns时。如下三个命令生成的报告中均可显示Clock Skew的具体数值。

report_design_analysis

report_timing_summary

report_timing

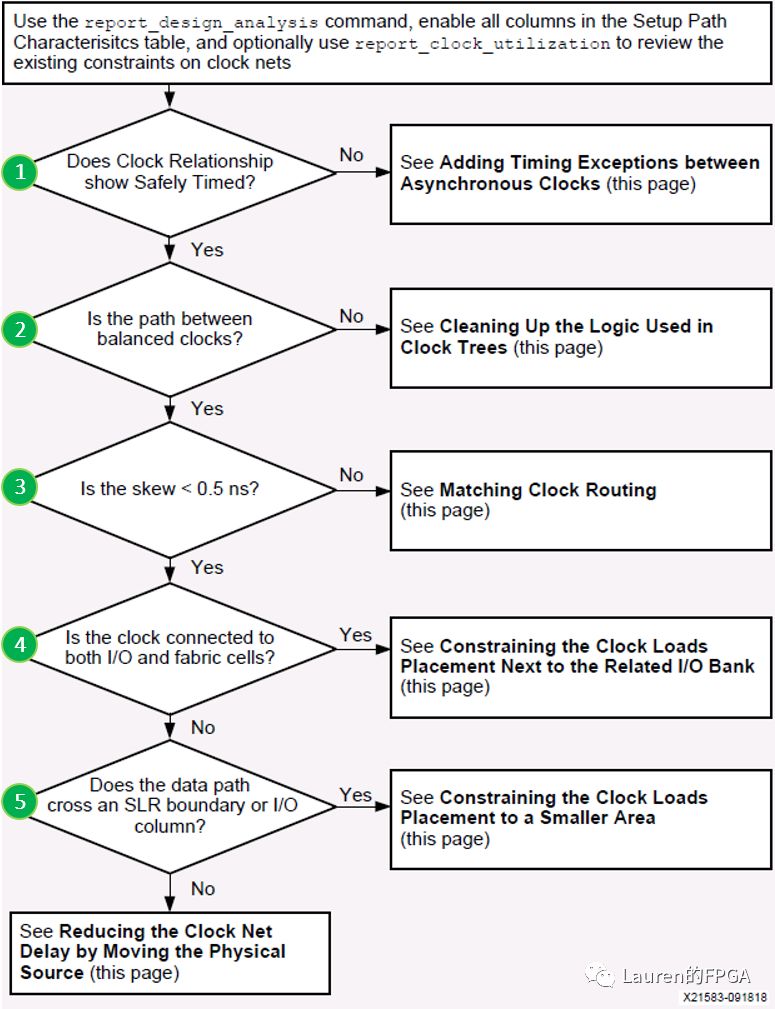

降低Clock Skew可采用如下流程操作。

图片来源: page 8, ug1292

1

异步跨时钟域路径是否被安全合理地约束

时钟关系有两种:同步时钟和异步时钟。如果发送时钟和接收时钟是同源的,例如来自于同一个MMCM,则认为二者是同步时钟,否则就按异步时钟处理。对于异步跨时钟域路径,可采用如下三者之一进行约束:

set_clock_groups

set_false_path

set_max_delay -datapath_only

2

发送时钟和接收时钟的时钟树结构是否平衡

时钟树结构其实就是时钟的拓扑结构。从发送时钟和接收时钟的角度看,平衡的时钟树结构是指二者“走过相同或等效的路径”。如下图所示,发送时钟和接收时钟来自级联的BUFG的不同位置上,这就是典型的不平衡时钟树。在设计中要避免这种情形。通过Tcl命令report_methodology可检查出设计中级联的BUFG。

<不推荐>

同时,还要利用好BUFG_GT和BUFGCE_DIV,两者均可实现简单地分频。如下图所示,利用BUFG_GT实现二分频,从而节省了MMCM。

此外,还要保持时钟路径“干净”,即不能在时钟路径上存在组合逻辑。在时序报告中,点击如下图标记的按钮,按下F4,在显示时序路径的同时也会显示该路径的时钟拓扑结构。

3

检查Clock Skew是否小于0.5ns

CLOCK_DELAY_GROUP可有效改善同步跨时钟域路径的Clock Skew,因此,Xilinx建议对于关键的同步跨时钟域路径,可通过设置该属性降低Clock Skew,即使发送时钟和接收时钟具有相同的CLOCK_ROOT值。CLOCK_DELAY_GROUP的具体使用方法如下图所示,其中clk1_net和clk2_net是Clock Buffer的输出端连接的net。但是,避免过多使用该属性,否则会适得其反。

4

时钟是否同时驱动I/O和Slice中的逻辑资源

如果时钟同时驱动I/O和Slice中的逻辑资源,且负载小于2000时,可通过CLOCK_LOW_FANOUT属性对相应的时钟net进行设置,最终可使工具将该时钟驱动的所有负载放置在同一个时钟域内。通过命令report_clock_utilization生成的报告可查看每个时钟的负载,如下图所示。

CLOCK_LOW_FANOUT的具体使用方法如下图所示。

5

检查数据路径是否穿越SLR或I/O Column如果时钟负载较小且穿越SLR或I/O Column时,可通过Pblock实施位置约束,将负载限定在一定区域内,例如在一个SLR内,以避免穿越一些特殊列,例如I/O Column。相反地,如果数据路径并未穿越SLR或I/O Column,可尝试对相应的MMCM或PLL做位置约束,使其位于这些负载的中央。

- 相关推荐

- 热点推荐

- 时钟

- CLOCK SKEW

-

哪些因此会导致时钟skew过大呢?FPGA中降低时钟skew的几种方法2024-03-13 2963

-

使用DDS生成三个信号并在Vivado中实现低通滤波器2025-03-01 2556

-

如何减小clock skew?2016-01-14 6837

-

时钟向导中是否有一个功能可以指导两个PLL生成没有偏斜的时钟?2018-10-11 2027

-

Labview中DBL数值常量控件出现了三个框2019-05-28 2718

-

非常高效三个linux shell命令分享2021-12-23 769

-

Skew Correction Using Delay Li2009-04-22 1514

-

使用NoKia手机的三个技巧2010-02-06 1581

-

电脑木马识别的三个小命令(不可不知)2010-02-23 1371

-

DSP硬件课程的三个实验报告资料合集免费下载2019-06-26 1121

-

同步电路设计中CLOCK SKEW的分析说明2021-01-14 1315

-

Qt中的三个exec之间有什么联系2023-03-06 3531

-

range里面三个参数的含义2023-11-21 12772

-

linux关机的三个命令2023-11-26 5759

-

Linux系统中最重要的三个命令2025-03-03 864

全部0条评论

快来发表一下你的评论吧 !