STM32调试DEBUG时需要了解那些知识相关资料概述

电子说

描述

学习STM32开发,肯定少不了DEBUG调试这一步骤。那么,本文带你了解一下这个调试相关的知识。

本文以STM32F1、Cortex-M3为例,其它系列芯片或内核,原理相同或类似。

1概况

在STM32中,有很多调试组件。使用它们可以执行各种调试功能,包括断点、数据观察点、 闪存地址重载以及各种跟踪。

STM32F1使用Cortex-M3内核,该内核内含硬件调试模块,支持复杂的调试操作。

硬件调试模块允许内核在取指(指令断点)或访问数据(数据断点)时停止。内核停止时,内核的内部状态和系统的外部状态都是可以查询的。完成查询后,内核和外设可以被复原,程序将继续执行。

当STM32F10x微控制器连接到调试器并开始调试时,调试器将使用内核的硬件调试模块进行调试操作。

2

调试框图

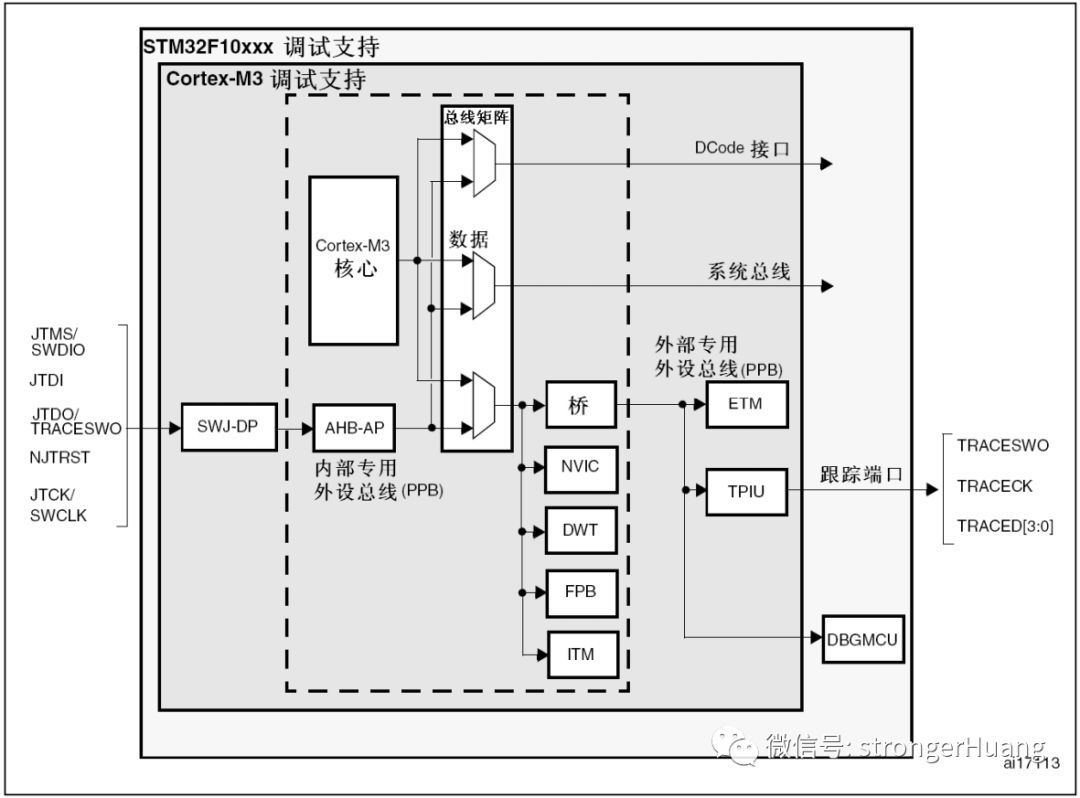

STM32F1和Cortex-M3的调试框图:

提示:Cortex-M3内核内含的硬件调试模块是ARM CoreSight开发工具集的子集。

ARM Cortex-M3内核提供集成的片上调试功能。它由以下部分组成:

SWJ-DP:串行/JTAG调试端口

AHP-AP: AHB访问端口

ITM:执行跟踪单元

FPB:闪存指令断点

DWT:数据触发

TPUI:跟踪单元接口(仅较大封装的芯片支持)

ETM:嵌入式跟踪微单元(在较大的封装上才有支持此功能的引脚),专用于STM32F1的调试特性

灵活的调试引脚分配

MCU调试盒(支持低电源模式,控制外设时钟等)

3

调试接口

STM32支持两种调试接口:

串行接口

JTAG调试接口

STM32的5个普通I/O口可用作SWJ-DP(串行/JTAG调试)接口引脚:

4

SWJ调试端口(serial wire and JTAG)

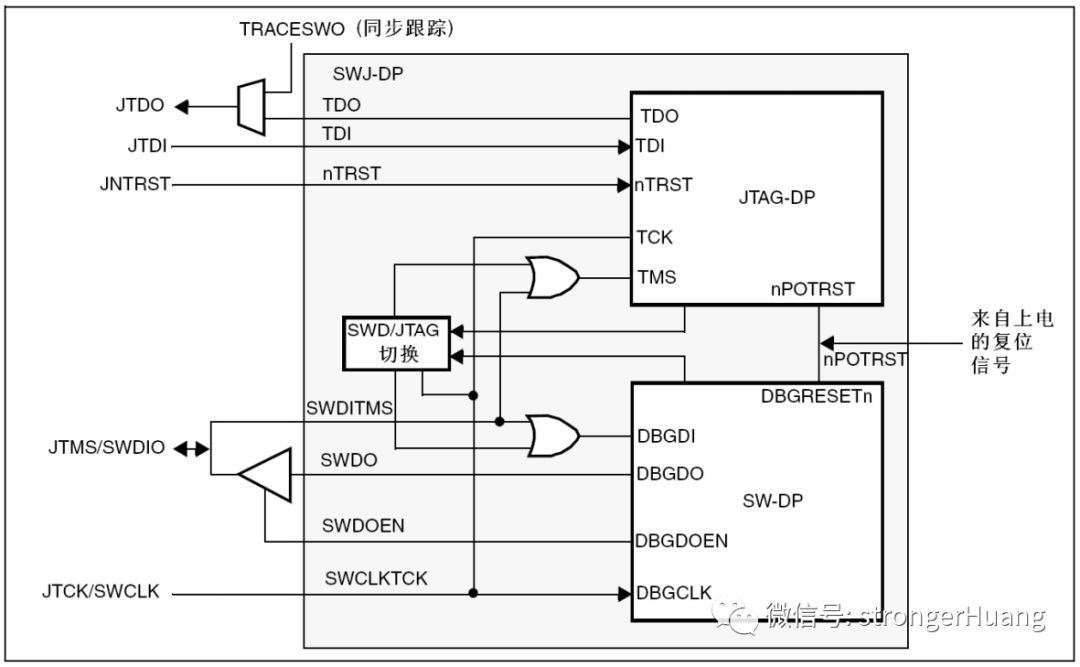

STM32内核集成了串行/JTAG调试接口(SWJ-DP)。这是标准的ARM CoreSight调试接口,包括JTAG-DP接口(5个引脚)和SW-DP接口(2个引脚)。

1.JTAG调试接口(JTAG-DP)为AHP-AP模块提供5针标准JTAG接口。

2. 串行调试接口(SW-DP)为AHP-AP模块提供2针(时钟+数据)接口。

在SWJ-DP接口中, SW-DP接口的2个引脚和JTAG接口的5个引脚中的一些是复用的。

SWJ调试端口:

上面的图显示异步跟踪输出脚(TRACESWO)和TDO是复用的。因此异步跟踪功能只能在SWDP调试接口上实现,不能在JTAG-DP调试接口上实现。

JTAG-DP和SW-DP切换的机制

JTAG调试接口是默认的调试接口。如果调试器想要切换到SW-DP,必须在TMS/TCK上输出一指定的JTAG序列(分别映射到SWDIO和SWCLK),该序列禁止JTAG-DP,并激活SW-DP。该方法可以只通过SWCLK和SWDIO两个引脚来激活SW-DP接口。

指定的序列是:

1. 输出超过50个TCK周期的TMS(SWDIO)= 1信号

2. 输出16个TMS(SWDIO)信号 0111100111100111 (MSB)

3. 输出超过50个TCK周期的TMS(SWDIO)= 1信号

5

JTAG脚上的内部上拉和下拉

保证JTAG的输入引脚不是悬空的非常必要,因为他们直接连接到D触发器控制着调试模式。必须特别注意SWCLK/TCK引脚,因为他们直接连接到一些D触发器的时钟端。

为了避免任何未受控制的I/O电平, STM32在JTAG输入脚上嵌入了内部上拉和下拉。

JINTRST:内部上拉

JTDI:内部上拉

JTMS/SWDIO:内部上拉

TCK/SWCLK:内部下拉

一旦JTAG I/O被用户代码释放, GPIO控制器再次取得控制。这些I/O口的状态将恢复到复位时的状态。

JNTRST:带上拉的输入

JTDI:带上拉的输入

JTMS/SWDIO:带上拉的输入

JICK/SWCLK:带下拉的输入

JTDO:浮动输入

软件可以把这些I/O口作为普通的I/O口使用。

6

利用串行接口并释放不用的调试脚作为普通I/O口

为了利用串行调试接口来释放一些普通I/O口,用户软件必须在复位后设置SWJ_CFG=010,从而释放PA15, PB3和PB4用做普通I/O口。

在调试时,调试器进行以下操作:

在系统复位时,所有SWJ引脚被分配为专用引脚(JTAG-DP + SW-DP)。

在系统复位状态下,调试器发送指定JTAG序列,从JTAG-DP切换到SW-DP。

仍然在系统复位状态下,调试器在复位地址处设置断点

释放复位信号,内核停止在复位地址处。

从这里开始,所有的调试通信将使用SW-DP接口,其他JTAG引脚可以由用户代码改配为普通I/O口。

提示:这个地方就是需要大家配置相关的引脚。

-

想要了解下大模型知识2024-08-20 840

-

STM32WB55开发(4)----配置串口打印Debug调试信息2023-12-01 2727

-

替换滚珠螺杆需要了解哪些参数?2023-09-08 1687

-

射频工程师需要了解的知识2023-02-17 1232

-

STM32(Cortex-M)内核DEBUG调试接口知识2022-02-08 1007

-

配置VScode编译、调试STM32(二)Cortex-Debug插件2021-12-01 1796

-

为什么要了解时钟树2021-08-12 1246

-

概述学习stm32需要掌握的前提知识2021-08-10 1521

-

了解一下Markdown的基本语法知识2021-08-04 942

-

STM32调试DEBUG需要注意的事项2020-05-11 2719

-

浅谈STM32调试DEBUG相关知识2020-03-06 5352

-

STM32F1系列DEBUG调试功能需要配置吗?2020-03-01 4560

-

Linux内核模块编程必须了解哪些知识?2018-08-24 1334

-

深入了解电路噪声的那些事2016-09-27 1078

全部0条评论

快来发表一下你的评论吧 !