FPGA之时序电路的理解

可编程逻辑

描述

一。 概述

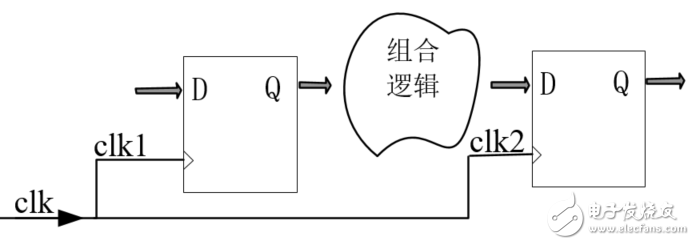

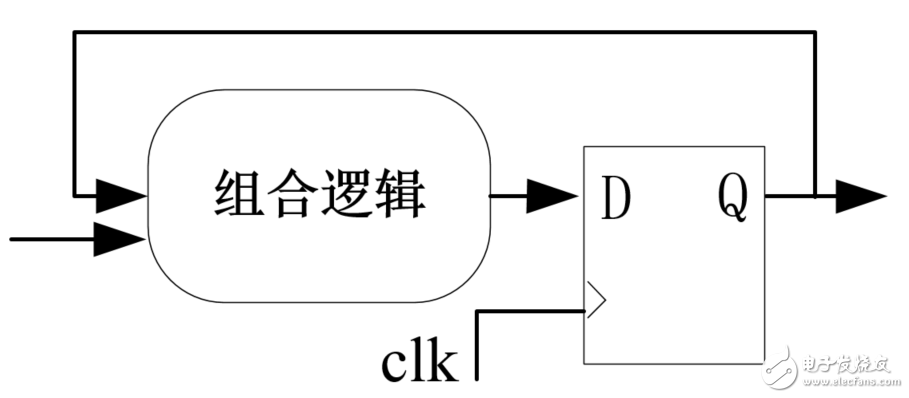

时序逻辑示意图,如下图所示。数据从一个寄存器出来,经过组合逻辑到达下一个寄存器。

在学习数字电路的过程中,我们都知道时序逻辑,但是大家对时序逻辑真的了解吗?

(1)纯组合逻辑电路的缺点在哪?

(3)纯组合逻辑电路完成不了什么功能?

(2)为什么需要时钟和寄存器呢?

带着这三个疑问我们来认识一下时序逻辑电路。

二。 同步时序逻辑电路的作用

1. 时序逻辑电路对于组合逻辑的毛刺具有容忍度,从而改善电路的时序特性。同时电路的更新由时钟控制。

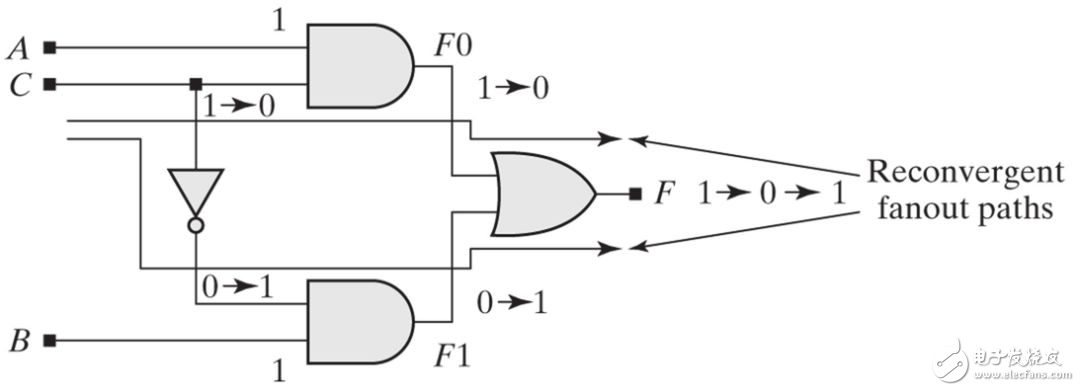

比如,在组合逻辑中当各路信号的路径长度不一样时那么组合逻辑的输出就会出现毛刺。如下图所示。F0和F1到达最后一个或门的路径长度不一样,那么在F端就会出现毛刺。

图片来自书籍《Verilog HDL高级数字设计》

毛刺信号如下图影印部分所示,由于C经过一个非门才到达下面的与门,故F1相对于F0有延迟,那么在F端就会造成毛刺,这个毛刺就是有短暂的时间输出为0。

图片来自书籍《Verilog HDL高级数字设计》

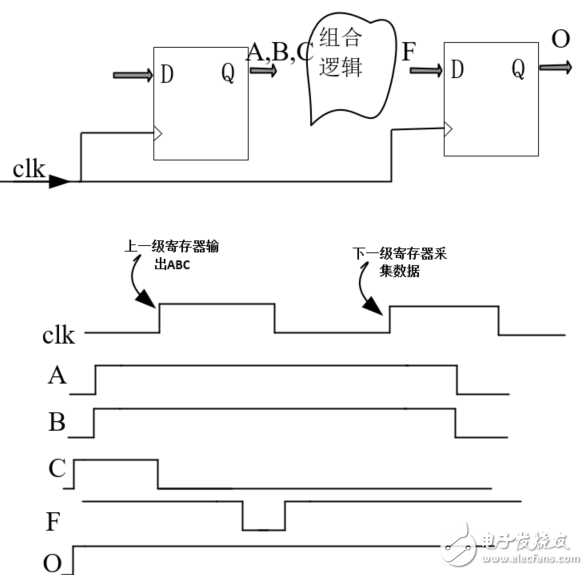

但是利用时序电路,数据A,B,C的触发是在时钟沿,输出信号F也是在时钟沿去采,而这个时钟沿到来的时间是在F输出稳定之后,故对电路的毛刺具有容忍度。如下图,可以看到最后寄存器的输出O就不存在毛刺。

这个特性使得在时序逻辑电路里面,电路的输出被采集到寄存器里面,并送往下一级电路的时候都是确定的而且是准确的,从而整体电路都是随着时钟沿在更新。

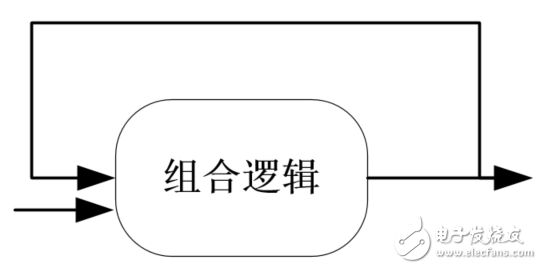

2. 纯组合逻辑只能由当前输入决定当前输出,而不能实现带反馈的逻辑,如下图所示,这样的话,你的电路就会陷入死循环而无法使用。

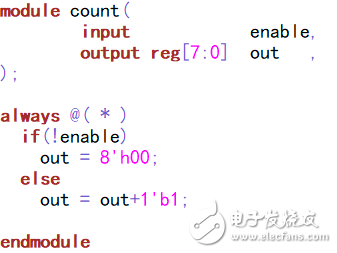

比如做一个计数器,如果我们用如下的组合逻辑的方式描述就会出问题。

而这种带反馈的逻辑,必须要通过寄存器把输出暂存起来,再由时钟沿去控制数据的反馈更新,这样电路才有意义。

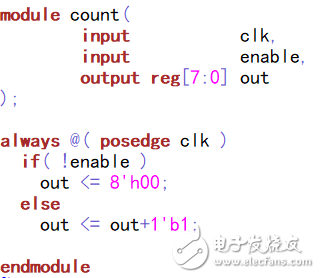

故计数器的正确描述方式如下。

-

时序电路包括两种类型 时序电路必然存在状态循环对不对2024-02-06 2762

-

什么是同步时序电路和异步时序电路,同步和异步电路的区别?2023-03-25 29090

-

时序电路基本介绍2022-09-12 10580

-

什么是时序电路?2021-03-04 1800

-

时序电路基本组件及时序逻辑电路应用实例2020-09-08 7741

-

组合电路和时序电路的讲解2018-09-25 25915

-

FPGA的设计主要是以时序电路为主吗?2018-07-21 5115

-

基于FPGA技术的RS232接口时序电路设计方案2017-01-26 1247

-

数字电路之时序电路2016-08-01 19566

-

FPGA重要设计思想及工程应用之时序及同步设计2016-05-10 465

-

什么是时序电路2010-01-12 8892

全部0条评论

快来发表一下你的评论吧 !