与时钟相关的PCB的设计考虑主要分为两部分

EDA/IC设计

描述

今天我们讲一下与时钟(clock)相关的PCB的设计考虑,主要分两部分:原理图设计 - 针对时钟电路应该放置哪些器件?以及PCB布局和走线 - 如何摆放与时钟相关的元器件并正确连线达到理想的性能。

我们先从原理图的设计看看跟时钟相关的电路:

时钟电路部分的供电电源要干净:

PCB板上会有很多高速的数字电路有可能给时钟电路部分的电源带来噪声,比如通信的信号、高手的数据传输、主电源的开关噪声、附近器件的输出开关等。时钟电路的电源上的噪声会导致产生的时钟有抖动(jitter),多路时钟输出的情况下每路时钟会有时序偏差,从而对时钟的正常工作带来严重影响。

因此需要“去耦” - 将其它部分的噪声跟时钟电路部分的供电进行“去耦和”,我在前面连载的去耦电容部分的文章讲述了去耦电容的作用以及如何选用,现在在时钟电路上就用上了。

大家也知道了如何为时钟电路的电源管脚选装去耦电容,比如:

一个0.01uf/0402封装的陶瓷电容,能有效旁路掉50-200MHz的高频噪声

一个0.1uF/0603封装的陶瓷电容,能有效旁路掉10MHz的噪声

一个4.7uF的钽电容能有效抑制几十KHz ~几MHz的低频段噪声

左侧:未加去耦电容的时钟波形; 右:加了去耦电容以后的时钟波形

为了降低其它电路的高频噪声通过电源影响到时钟的性能,除了去耦电容以外,在电源上串联一个磁柱能起到很好的抑制噪声的作用。关于磁珠的工作原理以及使用方法我会在后面的文章中专门讲解。简单来讲磁珠在DC和低频的时候表现的是电感特性,能够通直流而阻挡交流,在非常高频率的时候(几十MHz以上)表现出电阻特性,能够将高频的噪声变成热量消耗掉。因此配合去耦电容会达到更好的噪声隔离效果,如下面图的效果对比。

有噪声的时钟信号(左)在电源上加上磁珠以后的效果

磁珠选用我会在后面的文章中再进行介绍。下面是一个典型的磁珠+去耦电容配合的电源去噪声的电路示例。

传输阻抗匹配 - 将时钟脉冲信号最有效地传递出去

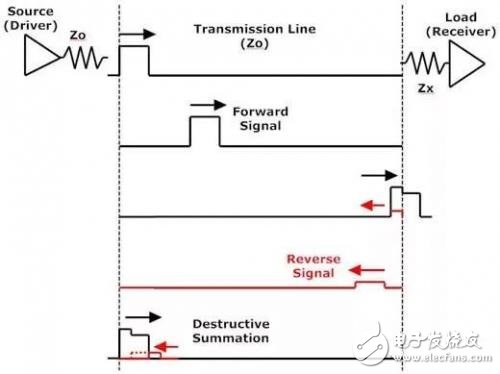

在上一篇文章中我们讲过,时钟电路产生的时钟信号要传输到使用该时钟信号的接收端,如果PCB上的传输线阻抗和发送端的输出阻抗不匹配、接收端的输入阻抗和时钟传输线的阻抗不匹配,都有可能导致时钟信号的反射而造成接收端得到的时钟信号边沿产生过冲等。

阻抗不匹配会造成反射从而破坏时钟信号的波形

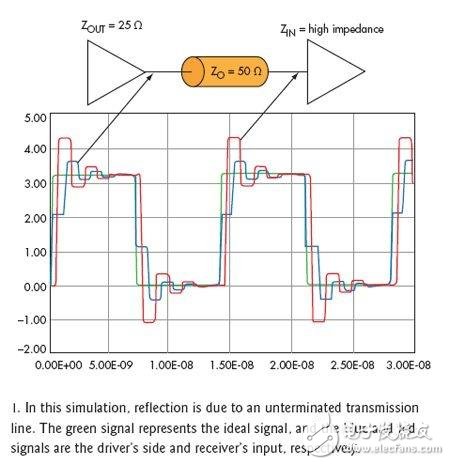

反射就会形成如下图一样的波形,绿色的信号为理想的时钟信号,蓝色信号为发送端测量到的信号,红色为接收端测量到的信号。

-

把转换后的电压信号AGC放大,这两部分电路采用什么芯片好?2024-09-20 323

-

Socket由哪两部分构成2024-08-16 1615

-

电磁继电器工作电路分为哪两部分2024-06-21 1991

-

位移传感器分为哪两部分 位移传感器的种类有哪些2024-02-14 5458

-

基于模型的 GaN PA 设计基础知识:I-V 曲线中有什么?(第二部分,共两部分)2022-12-26 2524

-

COMS电路中功耗分为两部分2021-11-11 2075

-

为何开关电源分为两种2021-10-29 2091

-

构成微机系统CPU的两部分是什么2021-09-10 1774

-

计算机系统由哪两部分组成?2021-07-22 1484

-

JSI项目分两部分框架内核2021-04-07 604

-

分两部分介绍锁相环2019-06-21 2401

-

PCB板材主要分为哪些类型2019-06-03 10235

-

ov7670和wifi模块拍照后自动上传的项目两部分接线冲突严重2019-01-15 1388

-

proteus 中分两部分的元件仿真错误2013-08-07 1989

全部0条评论

快来发表一下你的评论吧 !