浅谈自动驾驶等级定义及面临的挑战

描述

自动驾驶无疑是现今汽车领域最热门的话题之一,无论是历史悠久的汽车制造商或产业新星,皆在研发具有自动驾驶功能的汽车。拜摩尔定律(Moore’s Law)之赐,这些自动驾驶功能的开发者不仅大幅提升处理能力及改善传感器技术,还降低了成本。

「自动驾驶」这个词语涵盖众多功能的复杂技术领域,其中包含从「全自动驾驶」到「与驾驶共享控制权」。为利于分辨不同的自动驾驶能力,美国汽车工程师协会(Society of Automotive Engineers;SAE)便制订如表1的自动驾驶分级标准。

表1 SAE 自动驾驶等级定义

随着自动驾驶等级的提高,车辆也需要更妥善地掌握周围环境并能安全行驶,为达到此需求,车辆需要采用包含超声波传感器、全球定位系统(GPS)、雷达(RADAR)、摄像头和激光雷达(LiDAR)等多种类型的传感器,以及具备相关的处理能力。

每种类型的传感器都能提供汽车整体环境的相关信息,而自动驾驶汽车则需将这些元素融合在一起,才能构成一幅完整的影像。根据执行的自动驾驶等级,将改变传感器的部署和类型,例如,摄像头将用于车道维持辅助、盲点检测和交通号志辨识等应用;而频率调变连续波(FMCW)雷达则用于确定与目标物体间的距离。对于2级以上的自动驾驶等级而言,充分理解汽车所处的环境十分重要,这样,汽车才能辨识自身位置和周围障碍物,进而落实安全行驶,其可透过摄像头、雷达、激光雷达,以及GPS信息来完成对所处环境的掌握。但只参考GPS信息并不可靠,因为其精准度会改变,且讯号易受建筑物和基础设施阻隔影响。

能够掌握所在环境并采取行动,是达到自动驾驶功能的关键条件,因此不论是SAE 6个等级中的哪一级,只要出现意外的运作或行动,生命与环境皆会受到威胁。所以自动驾驶功能的开发必须限定在一个框架内,以确保设计和所有要素的安全性,严格遵守ISO 26262标准是开发自动驾驶汽车的必要条件,若能实施该标准提供的框架,将有助于确保安全性,及定义多个车辆安全完整性等级(ASIL)与容许范围内的失误率。部署自动驾驶解决方案后,也将受到来自世界各市场的严苛环境考验,为了确保系统在这些环境中能够正常运行,汽车级元件需通过被广泛认可的 AEC-Q100 或更高等级的资格认证。

架构执行自动驾驶功能的关键核心是中央处理模组。为了成功执行自驾功能,中央处理模组必须包含以下功能:- 信息整合、预处理和分配(DAPD):能连接不同类型传感器,并在处理单元内的各个处理单元与加速器之间,执行基本的信息处理、路由和交换。- 高效能连续处理:高效能处理单元用于执行信息萃取和传感器融合,并根据其输入的资讯进行高阶决策制定。在某些应用中,神经网络会在高效能连续处理中运行。

- 安全处理:依据「DAPD元件预处理的环境信息」与「来自神经网络加速与高效能连续处理单元的结果」进行即时处理与车辆控制。

创建中央处理模组时,设计人员会面对接口、扩展性、合规性和效能等多方面的挑战,若部署于功耗和散热受限的环境中,还要解决传统的尺寸、重量,以及功耗成本(Size, Weight and Power-Cost,SWaP-C)的难题,而在设计DAPD和安全处理器时,SWaP-C的难题尤为明显。

解决挑战使用单个元件是解决这些挑战的方案之一,此方法不仅能在同一个芯片中提供DAPD的接口、预处理和路由功能,还具备安全处理甚至是神经网络加速功能。这种高度整合的方法,打造了非常有利于解决SWaP-C的紧密整合解决方案。赛灵思(Xilinx)车规级Zynq UltraScale+ MPSoC异质单芯片系统,可用来运作这类高度整合解决方案,该元件提供四个高效能Arm Cortex-A53核心的可编程逻辑,来构成紧密整合的处理单元。此外,针对即时控制,异质单芯片系统还提供包含锁步(Lockstep)双Arm Cortex-5处理器的即时处理单元(RPU),不仅可执行高达ASIL C等级的安全功能,还可用于安全关键型应用。为了提供必要的功能安全性,RPU经过精心设计,具有减少、检测和缓解单个随机故障(包括由硬件和单个事件触发)的能力,这些元件能有效地在处理器系统资源与可编程逻辑之间进行功能区分。

DAPD带来的主要挑战在于如何在采用不同接口标准的众多类型传感器间建立连接。典型的解决方案是连接采用高速接口的多种传感器,如MIPI、JESD204B、LVDS和GigE,来达到摄像头、雷达和激光雷达这样的高频宽接口。但除此之外,DAPD还需要连接较慢的接口,如CAN、SPI、I2C和UART。若使用异质单芯片系统的处理系统(PS)和可编程逻辑(PL),便可支持多种业界标准接口,包括SPI、I2C、UART和GigE;同时,PL IO的高灵活性能让MIPI、LVDS和十亿位元串列连结直接连接,允许在PL中(通常使用IP核心)运作更高阶的协定。

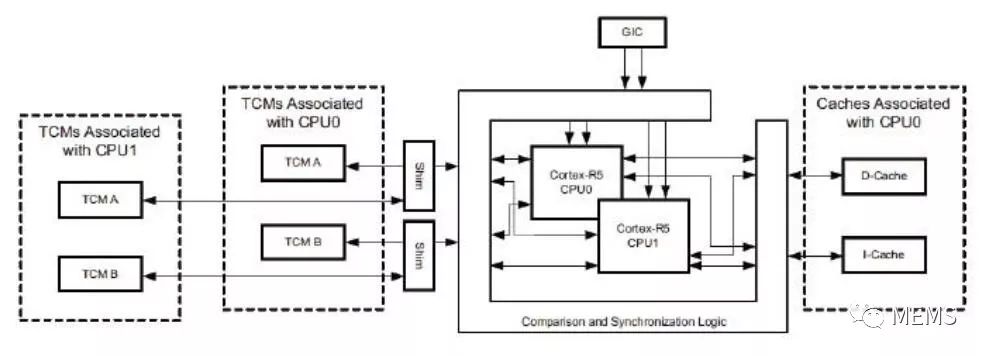

此外,在 PL中执行协定还能带来其他优势,例如轻松引入标准修订,以及能灵活设定解决方案所支持的具体传感器接口数量。而且,只要硬件设计提供正确的PHY,PL便可运作任意接口,真正落实任意到任意的接口功能。车规级Zynq UltraScale+ MPSoC的PL还能加速神经网络。由于PL具有平行特性,因此相较于传统采用CPU/GPU的方法,神经网络的执行更具回应性和确定性,因其消除了不同等级之间传统的外部存储器瓶颈。透过使用C、C++和OpenCL等这类高级语言,能在系统最佳化编译器SDSoC中运作这些神经网络,进而将功能从处理器系统无缝迁移到可编程逻辑内。另一大挑战是如何运作安全处理器,其必须依照从DAPD和高效能连续处理所接收到的命令进行操作,这些命令能确保车辆在所处环境中安全行驶,因此,安全处理器需要与汽车控制系统(如转向、加速和刹车)直接进行互动,这是自动驾驶功能的一大关键层面,因为任何错误将会导致生命的丧失和环境的破坏。异质单芯片系统在RPU中包含锁步双Arm Cortex-R5核心,可用于运作安全处理。

图2 即时处理单元架构

RPU 核心不仅具有锁步功能,还能执行多个附加的缓解功能。其中包括用于将 RPU 与存储器和快取存储器紧密耦合的纠错码(Error Correction Code),以及用于保护DDR存储器的双错误检测单个错误校正代码。在快取存储器和存储器中加入ECC功能,可确保执行自动驾驶汽车控制所需的应用程序和信息的完整性。此外,为了确保运作前底层硬件没有故障,还有提供启动时的内建自检测(BIST)功能,也可在运作过程中按照使用者的需求执行附加的BIST操作。此外,异质单芯片系统的架构还能在元件中隔离存储器和周边的功能。异质单芯片系统导入的这些功能,让同一芯片中能够落实安全处理、DAPD、甚至神经网络加速。为了确保拥有业界领先的元件品质,赛灵思收集了产业需求并将其融入到名为Beyond-AEC-Q100的内部品质控制计划中。此外,这款异质单芯片框架中,将大部分的测试要求加倍,以确保达到汽车级元件的安全限度,不仅如此,更高整合度还能降低最终解决方案所需的PCB设计和互连的复杂性,同时达到更低功耗。

总结

提供自动驾驶功能需要运作中央处理模组,该模组面临SWaP-C的挑战,因此采用针对DAPD、神经网络加速器和安全处理器的车规级高整合度解决方案,能够落实更小巧、更轻便、更低功耗的解决方案。

-

【话题】特斯拉首起自动驾驶致命车祸,自动驾驶的冬天来了?2016-07-05 13707

-

自动驾驶真的会来吗?2016-07-21 14079

-

细说关于自动驾驶那些事儿2017-05-15 7014

-

自动驾驶的到来2017-06-08 7301

-

如何让自动驾驶更加安全?2019-05-13 3621

-

自动驾驶汽车的处理能力怎么样?2019-08-07 2785

-

为何自动驾驶需要5G?2020-06-08 4161

-

自动驾驶车的人车交互接口设计方案2020-07-30 2864

-

自动驾驶车辆中AI面临的挑战2021-02-22 2547

-

自动驾驶OS市场的现状及未来 精选资料推荐2021-07-27 2420

-

自动驾驶系统设计及应用的相关资料分享2021-08-30 2299

-

自动驾驶技术的实现2021-09-03 3072

-

芯文芯事丨自动驾驶汽车设计将面临的五大挑战2019-07-02 2795

-

自动驾驶的必要技术和等级2023-06-21 936

-

不同等级的自动驾驶技术要求上有何不同?2025-10-18 2482

全部0条评论

快来发表一下你的评论吧 !