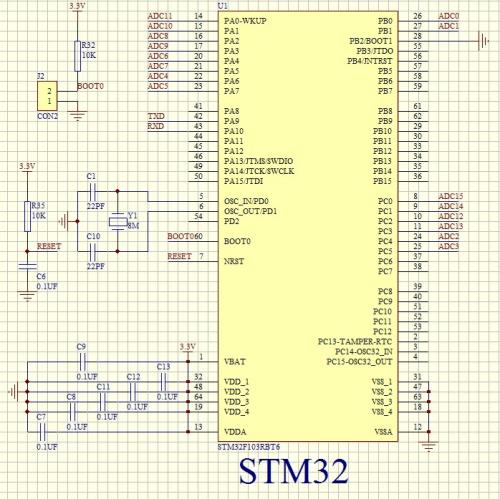

STM32单片机GPIO寄存器的功能解析

控制/MCU

描述

1、GPIO的寄存器按照功能可以分为以下几类:

A、配置寄存器

B、数据寄存器

C、位寄存器

D、锁定寄存器

2、对于GPIO端口,每个端口有16个引脚,每个引脚的模式由寄存器的四个位控制,每四位又分为两位控制引脚配置(CNFy[1:0]),两位控制引脚的模式及最高速度(MODEy[1:0]),其中y表示第y个引脚。配置GPIO引脚模式的一共有两个寄存器,CRH是高寄存器,用来配置高8位引脚,还有CRL配置低八位引脚。

3、端口位设置\清除寄存器(GPIOx_BSRR)

一个引脚y的输出数据由GPIOx_BSRR寄存器位的2个位来控制分别为BRy (Bit Reset y)和BSy (Bit Set y),BRy位用于写1清零,使引脚输出低电平,BSy位用来写1置1,使引脚输出高电平。而对这两个位进行写零都是无效的。

4、Cortex-M3有32根地址线,所以它的

寻址空间大小为2^32 bit=4GB。ARM公司设计时,预先把这4GB的寻址空间大致地分配好了。它把地址从0x4000 0000至0x5FFF FFFF( 512MB )的地址分配给片上外设。

5、stm32f10x.h这个文件中重要的内容就是把STM32的所有寄存器进行地址映射。如同51单片机的头文件一样,stm32f10x.h像一个大表格,我们在使用的时候就是通过宏定义进行类似查表的操作。

6、STM32总线有AHB总线、APB2总线、APB1总线

7、时钟系统。

A、从时钟频率来说分为告诉时钟和低速时钟,高速时钟是提供给芯片主体时钟,而低速时钟只是提供给芯片中的RTC及独立看门狗使用。

B、从芯片角度来说,时钟源分为内部时钟与外部时钟源,内部时钟是在芯片内部RC振荡器产生的,起振较快,所以时钟在芯片刚上电的时候,默认使用

内部高速时钟。而外部时钟信号是由外部的晶振输入的,在精度和稳定性上都有很大优势,所以上电之后我们再通过软件配置,转而采用外部时钟信号。

8、stm32f10x.h相当于STC12C616AD.H其作用就是定义了寄存器与外设之间的关系,类似于一个大的查找表。

9、STM32从3.0库开始引入了CMSIS,CMSIS是Cortex微控制器软件接口标准(Cortex MicroController Software Interface Standard)的缩写,这个是ARM定制的一个用于Cortex-M系列的一个标准,主要是为了提供通用api接口来访问内核和一些片上外设,提高代码的可移植性。

CMSIS有三个层:核内外设访问层Core Peripheral Access Layer(CPAL),中间件访问层Middleware Access Layer(MWAL),设备访问层(Device Peripheral Access Layer)。

CPAL用于访问内核的寄存器和组件,如NVIC,调试系统等。该层是由ARM实现的。

MWAL用于对中间件的访问,现在该层还未实现。(也不知道所谓的中间件是什么东西)。

DPAL用于定义一些硬件寄存器的地址和一些外设访问函数,由芯片制造商实现。

CPAL层的实现就是Core_cm3.c文件,DPAL层的实现就是system_stm32f10x.c文件(似乎还应该加上外设的函数库)。

10、在CoreSupport中的是位于CMSIS标准的核内设备函数层的M3核通用

的源文件core_cm3.c和头文件core_cm3.h,它们的作用是为那些采用

Cortex-M3核设计SOC的芯片商设计的芯片外设提供一个进入M3内核的接

口。这两个文件在其它公司的M3系列芯片也是相同的。

11、system_stm32f10x.c,是由ST公司提供的,遵守CMSIS标准。该文件

的功能是设置系统时钟和总线时钟

12、startup_stm32f10x_hd.s启动文件是任何处理器在上点复位之后最先运行的一段汇编程序。在我们编写的c语言代码运行之前,需要由汇编为c语言的运行建立一个合适的环境,接下来才能运行我们的程序。

-

STM32单片机的GPIO寄存器有哪些2022-01-05 1288

-

单片机教程七:单片机的特殊功能寄存器2009-05-15 2707

-

51单片机汇编语言教程_单片机的特殊功能寄存器2016-01-19 765

-

STM32 GPIO寄存器ODR BSRR BRR2017-07-29 1394

-

基于stm32的GPIO寄存器学习解析2018-01-11 13914

-

51单片机寄存器功能一览表2018-05-22 54014

-

51单片机经常使用的寄存器功能总结2019-08-29 1232

-

STM32单片机GPIO口的工作模式解析2019-08-20 2344

-

STM32单片机不完全手册之寄存器版本2021-07-31 1109

-

msp4306989单片机的寄存器 第五章2021-11-19 594

-

深入浅出谈STM32F4系列单片机GPIO相关配置——寄存器版2021-12-14 1007

-

STM32单片机GPIO口简介2021-12-28 1328

-

STM32单片机寄存器的功能解析2022-04-12 6289

-

单片机寄存器有哪些 单片机寄存器怎么理解 寄存器和单片机的关系2023-04-01 7433

-

单片机工作寄存器作用 单片机常用专用寄存器2023-04-08 9070

全部0条评论

快来发表一下你的评论吧 !