Xilinx A7芯片内部独立于逻辑单元的专用存储器

可编程逻辑

描述

上一篇中提到了SLICEL和SLICEM都可用作ROM,后者还可以作为分布式RAM(Distribute RAM,DRAM)。本篇主要总结的是块状Memory(Block Memory),实际上就是FPGA内部独立于逻辑单元的专用存储器,更像是一种硬核。

1. 基本结构

如下图所示,一个Block Memory的大小为36KB(RAMB36E1),由两个独立的18KB BRAM(Block RAM,RAMB18E1)组成。因此一个36K的Block Memory可配置成4中情形:

全部用于配置成36KB的BRAM;

全部用于配置成36KB的FIFO;

配置成18KB的BRAM和18KB的BRAM;

配置成18KB的BRAM和18KB的FIFO;

为什么不能配置成两个18KB的FIFO呢?因为一个Block Momery中间有一个叫FIFO Logic的结构,它用于生成FIFO控制信号,包括读/写地址等,由于它只有1个且不能共享,所以最多只能配置一个FIFO。

2. BRAM与DRAM的比较

简单的来说,BRAM就是一块固定存储功能的硬核,而DRAM是由一堆SLICE拼接成,实现存储功能的单元。

尽管BRAM可支持更多功能,但并不表明BRAM在任何场合都具有优势。两者的使用总结如下:

1. BRAM一定需要时钟;DRAM可以是纯组合逻辑,即给地址马上出数据(当然上篇说了,为了提高性能,在读出的时候加上触发器更好);

2. BRAM有着较大的存储空间;而DRAM实现大的存储空间会消耗很多LUT资源;

较大的存储应用,建议用BRAM;零星的小RAM,一般就用DRAM。但这只是个一般原则,具体的使用得看整个设计中资源的冗余度和性能要求。

3. BRAM的特点

当Block Memory配置成RAM时,有三种工作模式:

读优先

写优先

保持模式

三种模式体现了当对RAM中同一地址同时进行读操作和写操作时的不同。简单的说,当同时对RAM中的同一地址进行读写时,读优先模式将读出该地址内原有的数据,写优先模式将读出当前写入该地址的数据(注意断句,意思是最终会读出的数据是先写入的数据),保持模式则保持之前读出的数据不变。

4. Block Memory的使用

4.1 配置为RAM或ROM

在Vivado的“IP catalog”中搜索“RAM”,会出现如下结果,可以看到想要生成RAM或ROM,可以选择Distributed Memory或Block Memory,即上面提到的分布式和块状存储单元。

选择“Block Memory Generator”,可以看到块存储单元可以用作RAM或ROM,具体配置就不详细展开了。

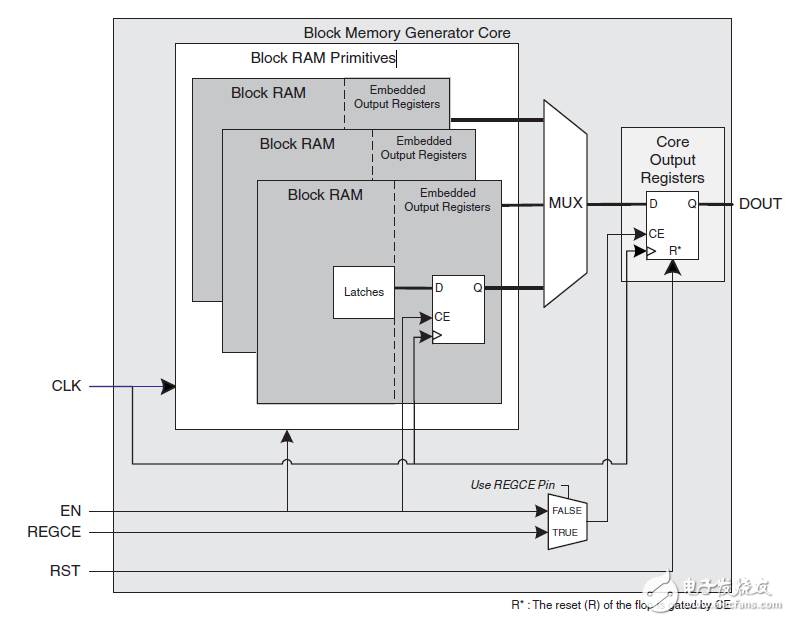

值得一提的是,在“Port A Options”选项卡中,有个Output Registers栏,可以选择Primitive Output Register和Core Output Register。其中前者位于BRAM内部,后者为CLB中的触发器。值得注意的是,在这里这两个触发器只支持同步高有效复位。这两个触发器可大大降低时钟到输出的延迟,在高速设计中,这两个触发器都使用,使用之后读操作的latency会增大为3个时钟周期。

4.2. 配置为FIFO

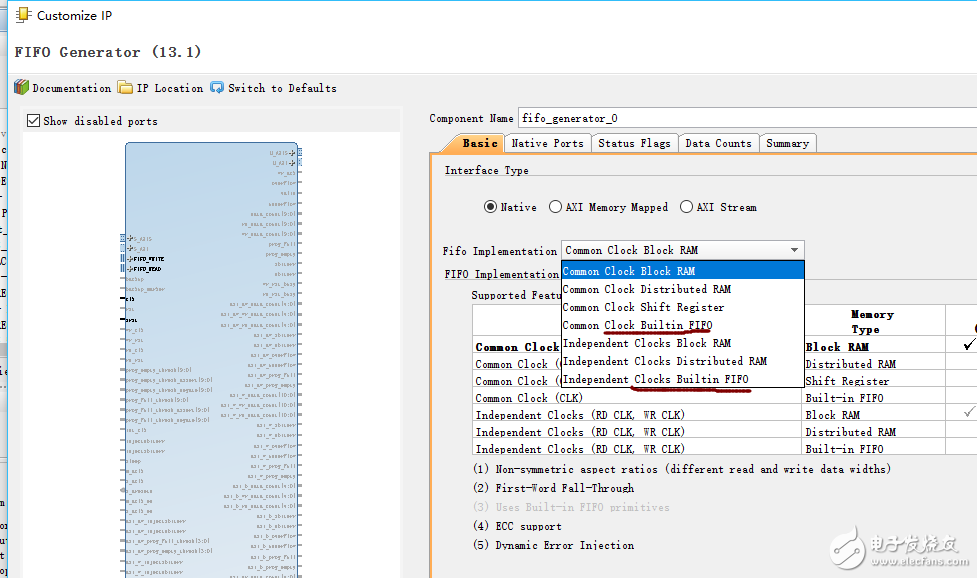

Block Memory中的BRAM还可配置为FIFO(同步或异步),同时提供专用的FIFO Logic用于生成FIFO的控制信号和状态信号。使用专用的FIFO Logic的FIFO称为build-in FIFO。Vivado提供了IP:FIFO Generator,即可以将BRAM配置为build-in FIFO,也可以采用CLB资源生成FIFO控制逻辑,并结合BRAM构成FIFO。

对于7系列FPGA内部未使用的18KB BRAM,Vivado通过Power Gating技术不会对其进行初始化,从而可以有效降低功耗。

-

苹果64位A7处理器,并没那么好?2013-09-13 7156

-

FPGA零基础学习系列精选:半导体存储器和可编程逻辑器件简介2024-03-28 1784

-

AVR系列单片机内部有哪几种类型的存储器2021-07-13 1075

-

AVR系列单片机内部有三种类型的被独立编址的存储器2021-11-23 1300

-

FPGA零基础学习:半导体存储器和可编程逻辑器件简介2023-02-23 1247

-

利用XILINX解决方案快速创建存储器接口设计2010-01-08 862

-

存储器和高速缓存技术2010-11-11 968

-

Xilinx DDR2存储器接口调试代码2016-06-07 933

-

基于OTP存储器存储单元读取阀值2017-11-07 2393

-

FPGA的雷达工程基本存储器概述2019-11-12 2178

-

如何配置存储器保护单元(MPU)2021-04-01 1412

-

一文详解xilinx CLB基本逻辑单元2022-04-24 5564

-

微控制器内部的存储器有哪些2024-08-22 2446

-

内部存储器有哪些2024-09-05 8195

-

存储器芯片的内部结构及其引脚类型2024-09-18 3984

全部0条评论

快来发表一下你的评论吧 !