On Semi RSL10蓝牙5多协议无线片上系统(S0C)开发方案

嵌入式技术

描述

On Semi公司的RSL10是蓝牙5规范多协议无线片上系统(S0C),具有双核架构和2.4GHz收发器,提供业界最低功耗,支持蓝压低功率和2.4GHz专用或定制协议,可使超低功耗蓝牙应用到无线应用如心率监视仪具有先进的无线特性而有最佳的系统尺寸和电池寿命.RSL10采用1.2V和1.5V电池,发送功率-17到+6dBm,RX接手灵敏度-94dBm,数据速率52.5-2000kbps,主要用在IoT前节点应用,蓝牙低功耗技术,可穿戴,能量收获,血糖仪(BGM).本文介绍了RSL10主要特性,框图和架构图及其主要单元,应用电路,以及开发板与评估板和开发板主要特性,电路图,材料清单和PCB设计图.

RSL10 is a Bluetooth 5 certified, multi-protocol radio System on Chip (SoC) which brings ultra-low-power Bluetooth Low Energy towireless applications.

Offering the industry’s lowest power consumption, RSL10 helps provide devices like heart rate monitors with advanced wirelessfeatures while optimizing system size and battery life.

Unlike most other multi-protocol radio SoCs, RSL10 is specifically designed for applications using 1.2 and 1.5 V batteries, andsupports a voltage supply range between 1.1 and 3.3 V without a required DC/DC converter. The highly-integrated radio SoCfeatures a dual-core architecture and a 2.4 GHz transceiver, providing the flexibility to support Bluetooth Low Energy and 2.4 GHzproprietary or custom protocols.

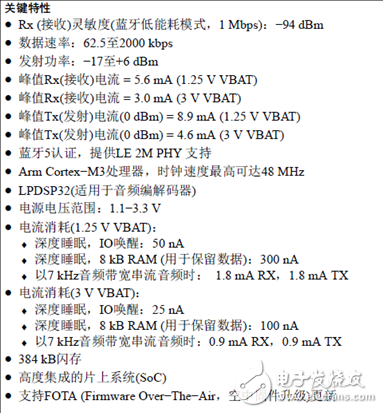

RSL10主要特性:

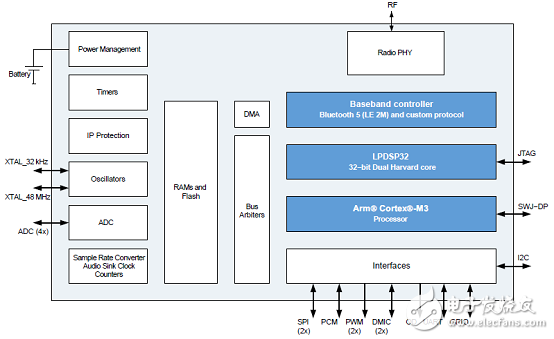

图1.RSL10框图

图2.RSL10架构图

RSL10架构图中主要单元:

RSL10应用

• IoT Edge-Node Applications

• Bluetooth Low Energy Technology

• Wearables

• Energy Harvesting

• Blood Glucose Monitors (BGM)

RSL10终端产品:

• Fitness Trackers/Activity Monitors

• Smart Watches

• Hearing Aids/Hearables

• Heart Rate Monitors

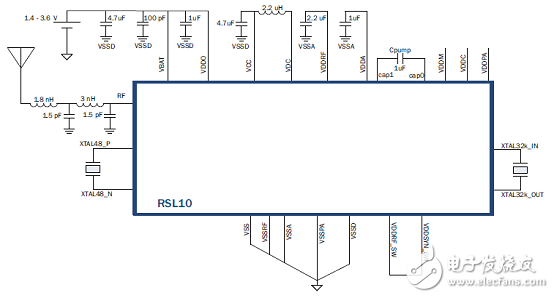

图3.RSL10降压模式应用框图

图4.RSL10 LDO模式应用框图

RSL10开发板

The RSL10 development board is used to easily develop Bluetooth® low energy technology-enabled applications based on the industry’s lowest power radio System-on-Chip (SoC).

RSL10开发板主要特性:

Compliance with the Arduino form factor

Support for PMOD (e.g., J4 is a standard connector)

On-board J-Link feature for simple debugging

Alternate on-board SWJ-DP (serial-wire and/or JTAG) for ARM® Cortex® -M3 processor debugging

Access to all RSL10 peripherals via standard 0.1" headers

On-board 4-bit level translator to translate the LPDSP32 debug interface at a low voltage to a 3.3 V JTAG debugger

Antenna matching and filtering network

Integrated PCB antenna

Bluetooth_ Low Energy IoT Development Kit (B-IDK)

This document helps you get started with the Bluetooth Low Energy IoT Development Kit (B−IDK). The B−IDK is acomprehensive node−to−cloud and a modular IoT platform that allows development of various BLE based use cases. Alongwith the hardware and software, the B−IDK includes a mobile app to interact with sensors and actuators.

The B−IDK features RSL10, Industry’s lowest power Bluetooth 5 SoC and comprises of a baseboard (BDK−GEVK) andseveral sensor and actuator daughter cards. For a complete listing of available daughter cards, please visithttps://www.onsemi.com/B−IDK. The daughter cards connect to the baseboard, via the two PMOD connectors and/or theArduino connector to enable various use cases.

HARDWARE

• BDK−GEVK − B−IDK Baseboard

• Daughter Cards – Optional

• BDK−DCDC−GEVB – Power Shield For Use With Higher Power

Daughter Cards – Optional

图5.RSL10开发板外形图

图6.RSL10开发板电路图(1)

图7.RSL10开发板电路图(2)

图8.RSL10开发板电路图(3)

图9.RSL10开发板电路图(4)

图10.RSL10开发板电路图(5)

图11.RSL10开发板电路图(6)

图12.RSL10开发板电路图(7)

图13.RSL10开发板电路图(8)

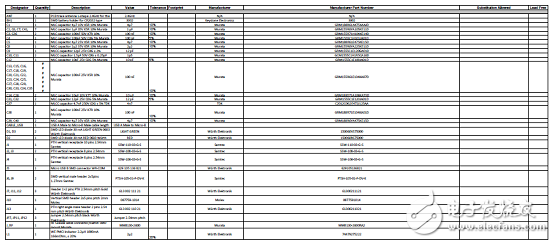

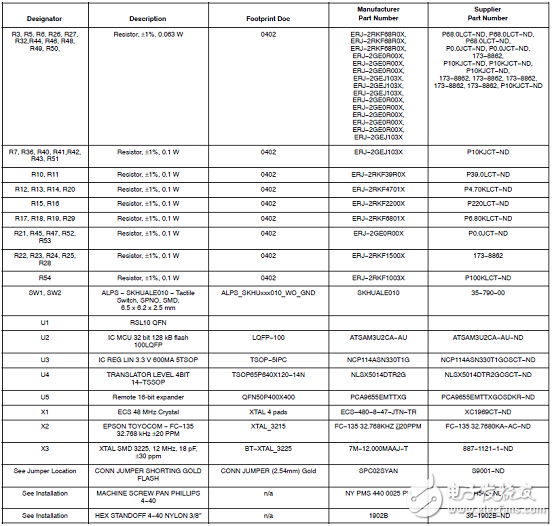

RSL10开发板材料清单:

RSL10评估板和开发板

The RSL10 Evaluation and Development Board is usedfor evaluating the RSL10 SoCand for applicationdevelopment. The board provides access to all input andoutput connections via 0.1″ standard headers. The on-boardcommunication interface circuit provides communication tothe board from a host PC. The communication interface

translates RSL10 SWJ−DP debug port signals to the USB ofthe host PC. There is also an on-board 4-bit level shifter fordebugging; it translates the I/O signal level of RSL10 to the 3.3 V digital logic level.

The Evaluation and Development Board enablesdevelopers to evaluate the performance and capabilities ofthe RSL10 radio SoC in addition to developing,demonstrating and debugging applications.

RSL10评估板和开发板主要特性:

• J−Link onboard solution provides a SWJ−DP(serial-wire and/or JTAG) interface that enables you todebug the board via a USB connection with the PC

• Alternate onboard SWJ−DP (serial-wire and/or JTAG)interface for ArmR CortexR−M3 processor debugging

• Access to all RSL10 peripherals via standard 0.1″headers

• Onboard 4-bit level translator to translate the LPDSP32debug interface at low voltage to a 3.3 V JTAGdebugger

• Antenna matching and filtering network

• Integrated PCB antenna

• Compliance with the Arduino form factor

• Support for PMOD (i.e., J4 is a standard connector)

图14.RSL10评估板和开发板建立图

图15.RSL10评估板和开发板采用外接J-Link调试器建立图

图16.RSL10评估板和开发板电路位置图(顶视)

图17.RSL10评估板和开发板电路位置图(底视)

图18.RSL10评估板和开发板3D电路位置图(顶视)

图19RSL10评估板和开发板3D电路位置图(底视)

图20.RSL10评估板和开发板3D电路图(1)

图21.RSL10评估板和开发板3D电路图(2)

图22.RSL10评估板和开发板3D电路图(3)

图23.RSL10评估板和开发板3D电路图(4)

RSL10评估板和开发板材料清单:

- 相关推荐

- 热点推荐

- soc

-

用于低功耗IoT应用的RSL10开发平台2021-11-17 1519

-

RSL10智能拍摄相机平台和RSL10传感器开发套件2021-03-11 2855

-

RSL10传感器和RSL10太阳能电池多传感器的使用差异2020-09-03 1507

-

【大联大世平ON Semiconductor BLE5.0 RSL10开发板试用体验】虽然小,但很强 --记安森美RSL102020-07-25 2582

-

【大联大世平ON Semiconductor BLE5.0 RSL10开发板试用体验】第三帖-2020-7-10-着手环境之一2020-07-10 1312

-

【大联大世平ON Semiconductor BLE5.0 RSL10开发板试用体验】板子牛刀小试(一)2020-07-05 2628

-

【大联大世平ON Semiconductor BLE5.0 RSL10开发板试用申请】基于世平ON Semiconductor BLE5.0 RSL10开发板智能可穿戴设备研发2020-06-30 960

-

RSL10传感器开发套件怎么助力物联网?2019-08-07 3848

-

RSL10 无线SoC,超低功耗多协议Bluetooth®5认证2019-04-18 1217

-

安森美最热门产品RSL10无线电SoC和KAF-09001 CCD图像传感器EDN2018-10-12 2006

-

[原创] On Semi RSL10蓝牙5多协议无线片上系统(SoC)解决方案2018-09-26 758

-

基于RSL10超低功耗多协议蓝牙5系统级芯片解决方案2018-06-16 21071

-

贸泽电子备货RSL10 多协议片上系统,为各应用提供超低功耗无线连接2018-01-23 1343

全部0条评论

快来发表一下你的评论吧 !