系统接口配置的关键在于Thunderbolt接口的引入

嵌入式技术

描述

随着当今高清视频技术的发展和4K超高清标准的即将出台,视频制作过程中需要更多的带宽来传输源头(如相机和存储器)与汇集处(显示器和存储器)之间的视频数据。输出这些数据的传统方法主要借助于数据USB接口或视频输出DisplayPort或高清晰度多媒体接口(HDMI)。而Thunderbolt接口的引入简化了系统接口配置,仅需一个接口就可满足数据和视频的传输需求。

随着视频分辨率从高清到超高清的升级,数据的传输量和速率也在不断提升。例如,一个像素分辨率为4096×2160、色彩模式为RGB444、色彩精度为12比特的4K视频的原始未压缩比特率为19.11Gbps或2.39Gbps,而这仅仅是一帧视频的大小,如果存储时长为30s的该视频,需要71.66GB的磁盘空间。

USB3.0是视频接口技术的一个连接选项。然而,当用户使用硬盘上存储的视频进行实时编辑时,USB3.0会导致明显的迟滞。主要原因在于,虽然拥有5Gbps的数据传输率,但USB特有的命令集并非是用来处理实时视频传输的。此外,当多个USB装置以菊花链方式连接在一起时,迟滞时间会更长。

具有10Gbps数据速率的Thunderbolt接口可使结构设计实现实时视频后期制作的理想速度、最小时滞和存储能力。专业工作室和广播视频设备可在视频采集卡、存储设备、适配器及视频显示器中利用这一技术。此外,与其它串联协议相比,Thunderbolt接口可通过配套电缆以菊花链方式最多外连6个设备,同时还不会大幅降低数据开销。

Thunderbolt简介

ThunderboltI/O技术由Intel公司开发,每个接口配备两个10Gbps全双工数据路径链路,要比Firewire800接口快达12倍。Thunderbolt采用64b/66b数据编码格式,而Intel开发的接口控制器可将PCI–Express和DisplayPort复用成为一个单数据流。Intel公司开发的第一代控制器代号为Light Ridge,随后的第二代、第三代控制器代号分别是Cactus Ridge和Redwood Ridge,而新一代(第四代)控制器的代号是Falcon Ridge。

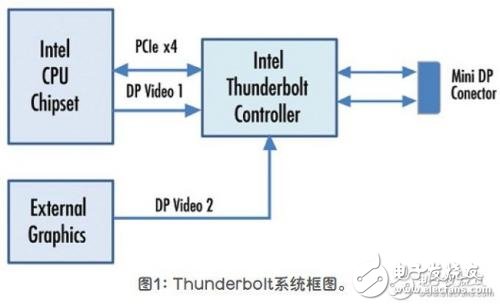

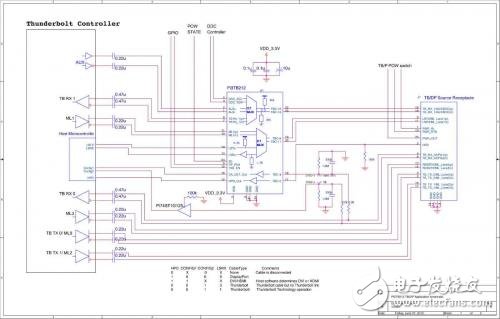

在主机设备中,控制器从I/O控制器集线器中获取PCI–Express数据,从I/O控制器中的负信号或如图1所示的外部图形控制器中获取DisplayPort数据。接下来,该组合信号通过全双工差分信号发出。一般情况下,每个控制器配备两个端口,可进行菊花链方式的连接。

Thunderbolt采用的是已有的迷你DisplayPort连接器,并已针对Thunderbolt信号的特点对该插槽进行了重新设计。Thunderbolt还可兼容标准DisplayPort连接。

表1中对比了映射到迷你DisplayPort连接器上的Thunderbolt信号和标准DisplayPort信号。线缆可以是电缆或光缆,但无论哪一种线缆都必须要保持活动状态以确保接收端信号的完整性。对于处于活动状态的铜缆,最大长度约为3m,而光缆的长度可扩展至数十米。外围系统会接收Thunderbolt信号,并将其送至另一控制器中,使其在终端提取PCIExpress与DisplayPort信号。

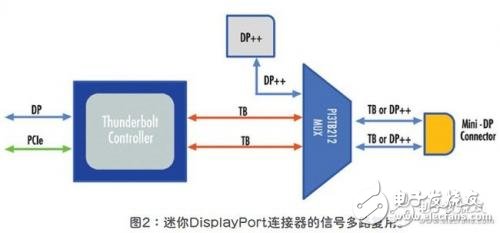

迷你DisplayPort连接器可在本地DisplayPort模式或Thunderbolt模式下工作,但由于使用的是同一引脚,这两种工作模式无法同时实现。如图2所示,控制器外部会设一个MUX集成电路(IC),用来控制Thunderbolt模式信号或DisplayPort模式信号的切换。

高速信号设计的挑战

对设计工程师来说,信号完整性是10Gbps以上数据速率传输所面临的一大挑战。这一问题一般是由信号本身的电磁特性引起的,会导致EMI/EMC信号衰减,进而缩短接收或终端侧的时间窗口并导致信号质量恶化。在设计过程中,工程师必须特别注意反射噪声、电源噪声和串扰噪声的影响。通过电路板中残段(stub)产生的阻抗失配反射可使噪声随着不断增大的频率/距离而增强。因此,应避免在PCB各层之间使用语音干扰分析装置(VIAS)。

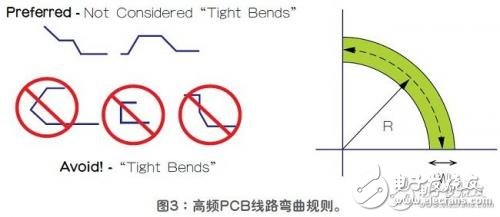

在走线布线期间,应使10Gbps信号驻留在PCB的某一层上,而不要穿越其它层。所有线路都应避免90°的弯曲,理想状况是径向弯曲或大于135°的弯曲,如图3所示。在高频率信号设计中应设置至少4个PCB层:10Gbps信号层、数字逻辑控制信号层、电源层和接地层。

将终端电阻置于接收端可最大限度地降低生成的残段长度。在一个普通的电路线路布局中,生成的残段始于主要的差分信号对到终端连接器,且线路长度应为最短。最佳方法就是将Thunderbolt接口芯片置于距离连接器最近的地方。

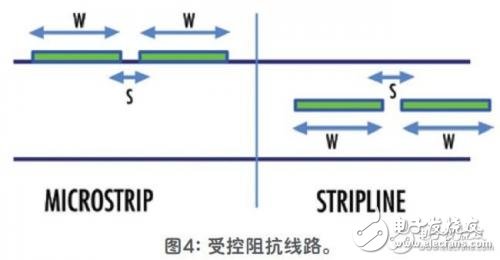

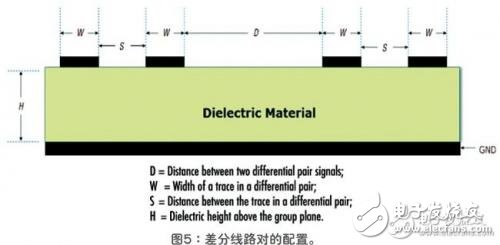

使用契合阻抗差分线路。可使用紧密耦合的边缘耦合带状线或微带线,以确保接收器能够抑制共模噪声(如图4所示,s距离被最小化)。将10Gbps差分对视为一个独特的信号,通过抑制或缩小线路的倾斜度来保持平衡。

高速接口设备周边的供电设计也是一个重要的考量因素。良好的供电设计是在电源和接地层中使用薄膜电介质(2mil~4mil,1mil=0.0254mm),从而为PCB电源电路创造一个平面电容,并将电源层和接地层用作旁路电源。这样一来就可以很容易地增加额外的外部旁路电容器,同时也可以节约BOM成本。剩余的外部旁路可使用小型(0603)X7R电容器,然后要密切留意这些电容器的共振频率,因为这有可能会导致旁路功能失效。

另外一个需要密切留意的参数就是抖动。这种信号失真形式会沿着数据路径累积,分随机性抖动(Rj)和定量性抖动(Dj)两种。所有的导电材料都会出现一定程度的信号衰减,因而会抑制抖动并缩小数据路径接收端的眼图开口度。使用再驱动器/中继器等信号完整性产品可恢复眼图质量并减小比特误码率(BER)。

由于时间窗口较小,10Gbps数据传输速率更易受抖动的影响。阻抗失配可以减少时间抖动容许量。配有适当滤波和旁路功能的清洁电源对于减少抖动来说也是非常必要的。为此,应在有源IC的各个VCC引脚旁安装一个低ESR的0.1μF去耦电容器。

控制器与迷你DP连接器之间视频与非视频数据都会复用和路由至迷你DP连接器上,这是通向外部空间的一个主要Thunderbolt接口。Thunderbolt控制器配有一个内部处理器,可控制外部MUXIC的切换。连接器配有一个热插拔检测(HDP)引脚,可根据插入设备类型告知处理器切换到相应信号(如表2所示)。

针对Thunderbolt控制器与连接器之间的MUXIC,可从

下载实际设计电路图,供您做进一步参考。MUXIC中包含2个MUX。3:1MUX可在显示数据通道(DDC)、DisplayPortAUX数据与10GbpsThunderbolt接口接收数据之间切换。2:1MUX可在DisplayPort主链路1(ML1)与Thunderbolt低速控制器数据之间切换。

p位于Thunderbolt控制器、MUXIC与连接器之间的10Gbps差分对是十分关键的信号路径。一般会有两个10Gbps发送信号对(HS0TX与HX1TX)和两个10Gbps接收对(HS0RX与HS1RX)。HS1RX差分信号对通过3:1MUX进行切换,因此要确保MUX的动态特性参数(如差分插损、差分回损、串扰、隔离性及倾斜度)不会导致10Gbps信号恶化。所有的10Gbps信号必须位于同一PCB层上,不应穿过其它任何一层。这些信号应呈条状线或微带线分布,且应完美契合,以避免出现倾斜。

接口中有多个10Gbps差分信号对。使用微带线时,为了实现最佳的信号完整性,应确保两个差分信号对之间的距离(D)为差分信号间缺口距离的两倍以上,这样就可以最大限度地减少两个差分信号对之间的串扰。当差分信号对离开MUXIC或控制器IC时,将差分线路(S)的长度设为3H,具体细节参考图5。

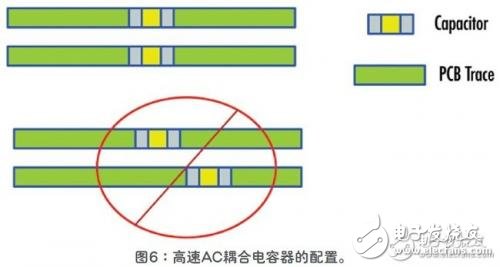

所有的高速及低速差分对都会AC耦合到Thunderbolt控制器中。根据Thunderbolt互联规范,10Gbps接收路径的AC耦合电容器值应介于0.34μF和0.6μF之间,发送路径的值应介于0.17μF~0.3μF之间。在该示例设计中,发送路径上使用的是0.22μF的电容器,而接收路径上使用的是0.47μF的电容器。此外,AC耦合电容器的大小应与微带线PCB线路的宽度相匹配,以减少信号丢失或阻抗失配。如图6所示,电容器应并行放置,且彼此之间不得相互抵消。更可取的做法是将电容器置于传输线对的终端。

在整体设计过程中,在控制器与连接器之间使用低成本ThunderboltMUX可最大限度地减少外部组件的数量。这样一来,只要满足了所有高速电路板设计指南的要求,这一架构方案就可使速率高于10Gbps的信号以一种直接、可靠的方式进行路由。

- 相关推荐

- 热点推荐

- 接口

-

Intel Thunderbolt接口科普2023-09-12 3889

-

物联网增长的关键在于可靠的通信技术资料下载2021-04-28 806

-

高级配置和电源接口规范2020-12-10 1403

-

请问TI有支持Thunderbolt接口的芯片吗?2019-05-24 1670

-

赵盛宇:国内智能装备的突破之路关键在于两点:内部定位和外部环境2018-01-12 5020

-

thunderbolt接口是什么_thunderbolt接口有什么用_thunderbolt怎么用2017-12-05 59489

-

接口配置2016-12-24 766

-

高速传输技术接口新霸主:Intel再创Thunderbolt“一线”生机2013-07-02 3803

-

专访格罗方德Subramani Kengeri:28nm量产致胜关键在于HKMG2012-07-15 5775

-

手机无线充电关键在于兼容性2011-12-24 3322

-

关于Thunderbolt接口你应该知道的事2011-12-02 3963

-

超导体关键在于磁性?美科学家努力找证据2010-02-23 1292

-

汽车音响的关键在于调试2010-01-14 1458

-

传感口器的关键在于涂层2009-11-17 557

全部0条评论

快来发表一下你的评论吧 !