什么是时钟呢 时钟信号的关键指标

电子说

描述

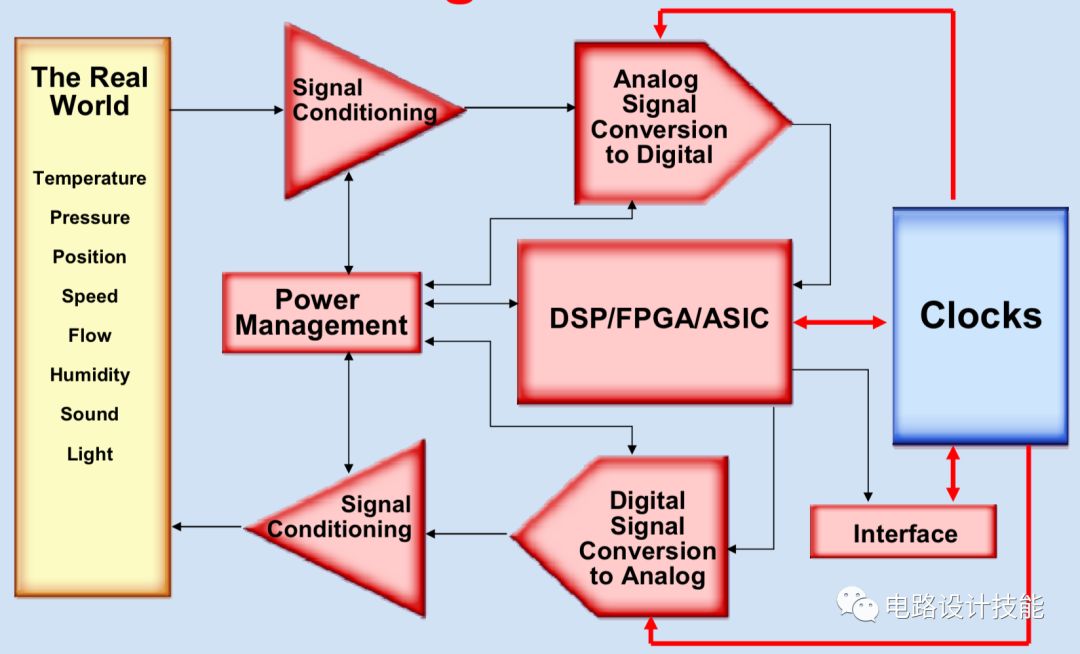

电子产品系统中有一个非常重要的部位 - 时钟。多数工程师意识不到它的重要性,觉得只要板子上的晶体/晶振能工作就可以了,其实不然,在今天数字逻辑、数字计算统治的世界里,几乎所有的操作都是在时钟的作用下实现的,因此时钟对于电子产品来讲就如同人的心脏一样重要。

时钟是电子系统的心脏

我们今天的这一讲就先看看时钟信号的一些关键指标:

什么是时钟呢?

简单的来讲就是由电路产生的具有周期性的脉冲信号,它不一定就是方波,更不一定就是50%占空比的方波,系统中时钟信号被用来为系统中多个同步执行的电路之间、为不同系统之间的数据传输提供参考基准。微处理器的指令执行也都是在时钟的节拍下进行操作的,很多时候我们以处理器的时钟频率高低来粗暴地评价该系统的性能。

信号链路中时钟的重要性 - 数字域离不开时钟

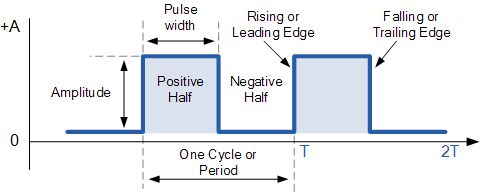

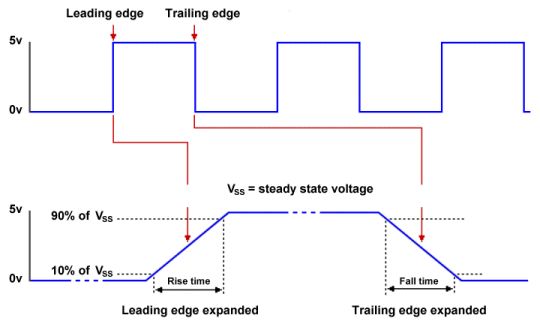

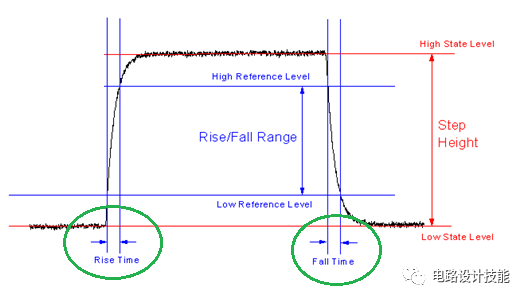

首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边沿(上升沿或下降沿)进行同步的,时钟的边沿要求比较快,而时钟的周期则比较长,至少相对于时钟的边沿会长很多,因此我们通常以方波来表征时钟(如下图)。虽然我们理想中画的时钟边沿时间为0,实际数字电路在高、低电平之间的翻转是需要时间来实现的,也就是说矩形波时钟的上升沿和下降沿都是有一定的持续时间的,50%占空比的方波看起来最对称、最完美,但实际的系统中矩形波的高低电平持续的时间未必是1:1,因此矩形波时钟信号常用5个关键的参数指标来描述:

矩形波时钟(包括50%占空比的方波)

时钟上升沿和下降沿的定义

时钟信号的幅度(也称为电平,比如5V、3.3V、TTL、LVCOMS等)

时钟信号的周期T 或 频率F = 1/T

时钟信号的脉冲宽度- 高电平持续的时间

上升沿时间

下降沿时间(未必跟上升沿时间一样)

实际的时钟上升沿(充电)和下降沿(放电)的时间是不同的

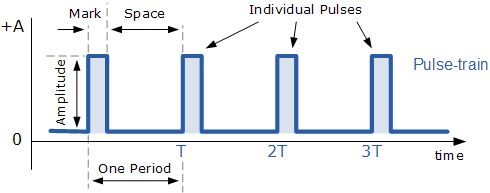

有时我们会用到脉冲时钟信号,本质上它是矩形波时钟信号的一种,只是我们更关注的是其高、低电平的持续时间,而不是其信号的上升沿和下降沿。

脉冲时钟信号波形

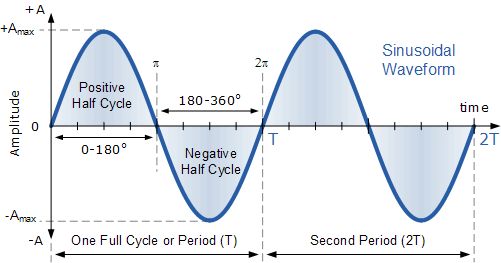

当时钟信号频率变高到一定程度,由于时钟信号的周期长度已经跟时钟的上升、下降沿接近,因此此时的时钟信号就变成了正弦波。

正弦波时钟信号波形

理解了上述关键指标的涵义,就可以看懂所有的数字器件中最重要的时序信息,比如下面就是SPI接口数据传输的时序图,在使用具体的SPI器件的时候,我们不仅要根据这个时序图看懂各个相关的数字信号之间的时序关系,更重要的是要根据起数据手册中的具体数据(比如高电平持续时间、时钟上升沿时间等)来设计系统的时钟信号及相应的时序以满足器件数据手册中的规格要求。

SPI的时序图

精准度和稳定度

不同的系统对时钟这些参数的要求是不同的,如果你仅仅是让单片机执行一些简单的指令,比如采集一些信息(传感器信号)、输出一些信号(点亮LED等),而这些动作并不需要精准的时钟频率,对频率的精度要求就可以很低,系统只需要一个RC震荡的时钟就可以了。但如果你想用单片机或非常简单的数字逻辑做一个数字钟表,经过校准以后,你希望一周、一个月以后这个钟表还能够分秒不差,那你的时钟源不仅要求精准度要足够高,而且长期的稳定度也要高,并且不要随着温度发生漂移。

高速的通信系统对系统时钟的精度、准确度、各种环境下的稳定度要求更高,普通的晶体振荡器也不能满足系统的要求了。

边沿抖动(Jitter)

数字电路的工作都是在时钟的边沿进行同步的,因此即便是时钟的频率稳定、高精度,如果时钟的边沿发生抖动,也会导致系统的性能下降。

时钟的边沿抖动(jitter)

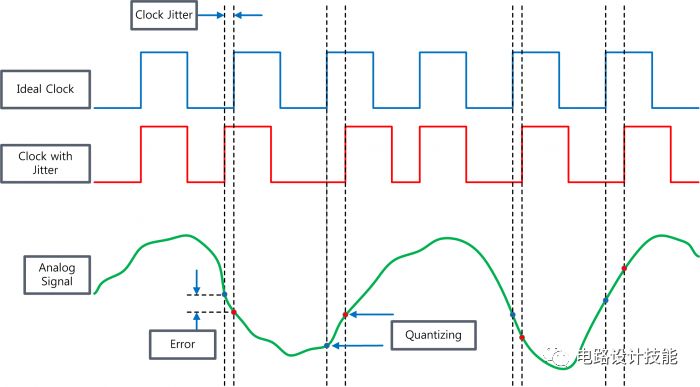

如下图,在一个模拟/数字转换的系统中,通过时钟的上升沿对输入的模拟信号进行采样,如果采样时钟的上升沿发生了抖动,其上升沿采样的模拟信号的时间点相对于理想的时钟信号应该采样的时间点发生了比较大的偏差,造成了采样误差,也就相当于对输入的模拟信号带来了噪声,而这种噪声有可能非常严重,导致系统的性能大大降低。即使你使用了高性能器件(当然价钱也很高),如果你使用的时钟由于种种原因导致边沿发生了抖动,也会让你的系统产生灾难性的后果。

实际电路中的时钟信号会发生变形

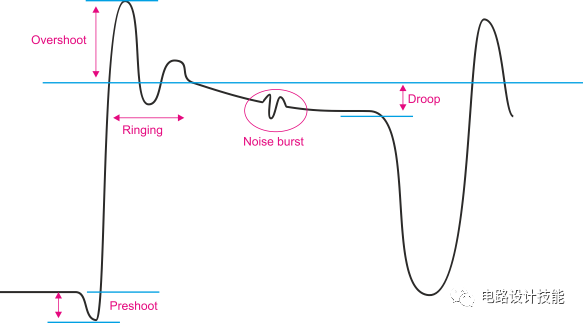

多数情况下,你会看到你板子上的时钟信号如下图所示,矩形波已经不再是好看的矩形波,时钟沿出现了过冲和振铃,如果严重就会对你的电路性能造成影响。

用示波器观看到的时钟信号的波形

实际电路上时钟信号的过冲和振铃

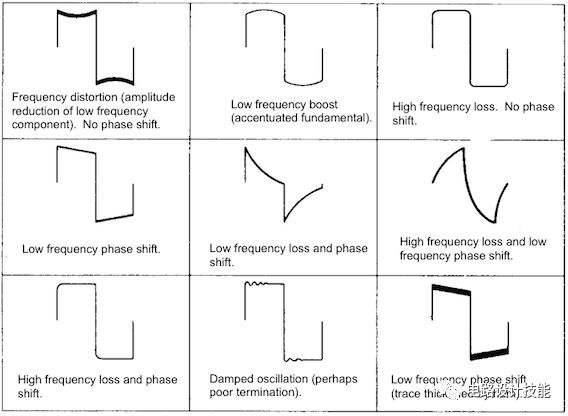

还有下面图中所示的各种情形,都有可能在电路中出现,导致这种波形失真的原因可以根据图中所示进行分析。

系统中会导致时钟信号变形的一些原因

从理论上分析就要借助神奇的傅立叶变换 - 任何一个信号都可以分解成n个不同频率的正弦波, 通过观察信号的波形变化,可以分析出相对应的各个频率的信号幅度的变化,进而判断出你的电路设计中存在的问题。

-

相位噪声的概念、关键指标及晶振选择2022-07-14 5975

-

时钟信号的关键指标2019-05-06 6343

-

时钟信号的关键指标(上)2019-07-21 6929

-

示波器的关键指标2019-07-24 1389

-

音频功放的关键指标是什么?2021-06-03 1670

-

PWM三个关键指标说明2021-12-13 3111

-

音频功放的关键指标2009-12-24 2258

-

探析MEMS时钟技术对5G的重要性2019-01-24 3644

-

采用MPC92433高性能时钟合成源完成时钟信号电路的设计2019-10-03 1559

-

Linux运维中常见的关键指标参数汇总2021-05-05 2134

-

跨时钟域信号该如何处理呢?2023-06-27 2189

-

工业ai质检的关键指标有哪些2023-11-02 2369

-

示波器的三大关键指标有哪些?2024-01-17 2535

-

什么是时钟信号?数字电路的时钟信号是怎么产生呢?2024-01-25 14969

-

什么是CPU时钟速度2024-09-26 2626

全部0条评论

快来发表一下你的评论吧 !