新型的存储器技术有哪些 新型存储器能解决哪些问题

存储技术

描述

小存储单元尺寸 (Cell Size)、高性能 (Performance) 以及低功耗 (Power Consumption) 一直是存储器业者持续追求的目标。然而,14nm 以下,半导体工艺迁移到 Fin-FET (Fin Field-Effect Transistor,鳍式场效应晶体管),一种新的晶体管结构,这技术无法直接套用在既有的ㄧ些嵌入式存储元件上。再者,为因应未来人工智能 (AI) 及边缘计算 (Edge Computing) 等等高计算能力的需求,既有高容量存储器,如 DRAM、NAND 闪存的高耗电及速度问题已无法跟上需求的脚步。

因此,半导体产业正处于转折点。微控制器 (MCUs) 和 ASICs 中的嵌入式存储器,以及,从手持移动装置到超级计算机等所有应用的离散存储器芯片都在考虑更换。这些替换将有助于系统设计人员降低功耗,从而延长手持移动装置电池寿命或降低数据中心系统冷却要求,也能提高系统性能,符合未来这些高运算能力系统的需求。在某些情况下,通过使用更先进的工艺技术或系统设计,替换传统的存储器类型还能降低系统成本。

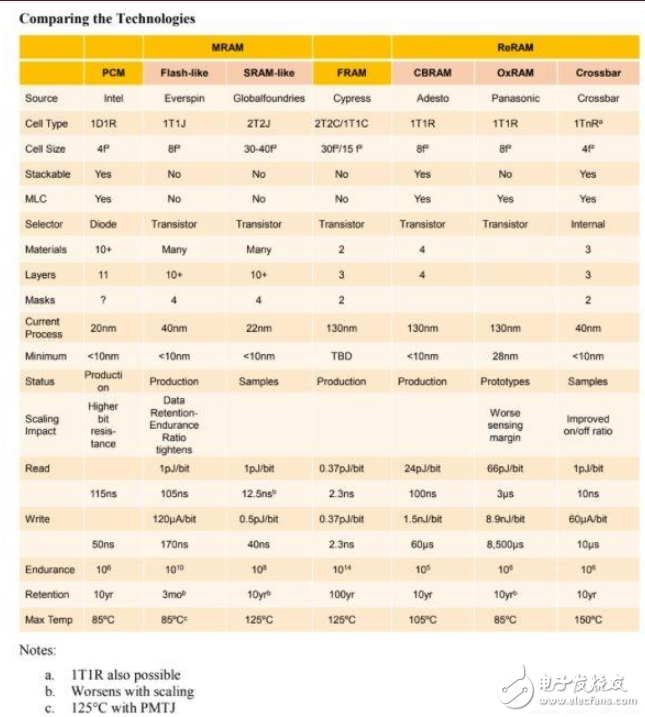

尽管ㄧ些新存储器技术已经研发出来,但在这竞争激烈的市场,只有极少数能够成功。 图1是ㄧ些新存储器技术的列表。然而,无论哪一个技术胜出,这些新型非易失性技术系统的功耗肯定会低于现有的嵌入式 NOR 闪存和 SRAM,或是,离散 的 DRAM 和 NAND 闪存的系统。

嵌入式存储器 (Embedded Memory) 的问题

这里面包含二个问题,嵌入式存储器的尺寸以及功耗。

先进的逻辑工艺已超越 14nm,迁移到 Fin-FET 结构,过去十年或更长时间内用作片上存储的嵌入式 NOR 闪存已失去跟上这些过程的能力收缩。这个问题被称为闪存的 ”缩放限制”- 无论芯片上其余的 CMOS 能够缩小多少,闪存都无法跟上步伐。必须要有新的嵌入式存储器技术能搭配这些先进工艺制造的 ASIC 和 MCU。

嵌入式 NOR 闪存并不是唯一受到工艺演进影响的。嵌入式 SRAM 也面临着相似的问题。随着工艺缩小到几十纳米或更小,SRAM 存储单元 (Memory Cell) 的大小无法跟上。与 NOR 闪存不同,SRAM 的问题在于其存储单元的尺寸不会与工艺成比例地缩小。当工艺缩小 50% 时,它可能仅缩小 25%。

这限缩了嵌入式 NOR 和嵌入式 SRAM 的发展,我们需要新存储单元技术能继续与流程成比例地缩小。幸运的是,这些技术已经存在,并且已经开发很多年了。

另一个问题为转向新的存储器技术提供了强有力的论据,那就是存储器消耗太多电力。物联网 (IoT) 和移动装置使用电池电力运行,其存储器必须谨慎选择,因为它们消耗大部分的电池电力,降低电池使用时间,而新的嵌入式存储器技术可以降低功耗,因应这方面的需求。

下一代移动架构将为人工智能及边缘计算导入更高的计算能力需求,同时要求更低的功耗以满足消费者的期望以及在严峻的市场竞争中获胜。当然这些必须以低成本实现,而这就是现有存储器技术的挑战。当今大多数电池供电的移动装置和其他各种应用使用的 MCU 均采用 CMOS 工艺制造,CMOS 工艺支持两种存储器技术:NOR 闪存和 SRAM。虽然这些技术在 CMOS 逻辑工艺中很容易嵌入,但它们消耗的功率通常超过预期。

当需要更大的存储器时,设计人员通常会添加外部存储器芯片,如 SPI (Serial Peripheral interface) NOR 闪存、NAND 闪存、DRAM 或这些存储器的组合。然而这些外部存储器对功耗的影响更大。

以上二个现有存储器的问题迫使设计人员开始评估新型的存储器技术,试图彻底解决这些问题。

大系统中的功率问题

在物联网的另一端,在云端 (Cloud),数据中心服务器 (Server) 的存储器和数据存储架构也非常重要,因为功耗通常是数据中心成本最高的元素之一,尤其是纳入冷却系统时。

DRAM 和 NAND 闪存是当今用于计算系统,从智能手机到数据处理设备,的主流存储技术。然而对计算系统设计而言,这两种存储器类型都无法单独存在,因为,虽然 DRAM 支持快速读取和写入,但 DRAM 存储单元之电容的电荷在几毫秒 (ms) 內就会衰减消失,所以需要不断进行刷新 (Refresh),而刷新会消耗大量功率。即使系统是闲置的,DRAM 也需不断地使用电源进行刷新。

8Gb DRAM 芯片消耗的大约 20% 的功率用于刷新,在芯片总功耗 140 毫瓦中占了 25 毫瓦。如果断电,DRAM 的内容就会消失 (易失性存储器) - 即使复电也不会回复,因此 DRAM 不适合作为启动、应用程序、操作系统等等代码 (Code) 存储使用,系统须搭配其他非易失性存储器来执行代码存储功能。

另外,由于其多路 (Multiplexed) 寻址技术,DRAM 也相对较慢。DRAM 行地址选择 (RAS) 和列行地址选择 (CAS) 让随机读取需花费 25 到 300 奈秒 (ns) 的时间,而这个延长的时间导致更高的总能量消耗。

闪存 (Flash Memory) 存储的数据不会衰减,断电后可以保持其内容多年,但 NOR 闪存比 DRAM 贵很多,而 NAND 闪存是顺序读取而且无法存取至特定的字节。这与计算机运算随机寻址读取的需求并不匹配。 所以 NAND 闪存必须与 DRAM 配对才能用于代码存储使用。

与 DRAM一样,NAND 闪存也具有ㄧ些特性导致其消耗的功率超出预期。首先,它需要使用片上 (On-Chip) 电荷泵产生高内部电压。其次 NAND 闪存的写入速度也很慢。最麻烦的是,NAND 闪存在写入时不能直接覆盖旧数据,在将新数据写入闪存之前须先擦除 (Erase) 原有存储的数据,并且必须一次写入整个页面 (Page,通常为 8,096 字节),无法只写入单一特定的字节。

闪存技术不使用相同的机制来编程或擦除内容,您不能只擦除单ㄧ位 (bit)、字节 (byte) 或页面,而是必须整块 (Block) ㄧ起,ㄧ个块通常包含数十万个页面。页面写入是一个缓慢且耗能的过程,通常需要 300 微秒 (μs) 时间并消耗 80 微焦耳 (与读取时的 2 微焦耳相比) 能量。块擦除 (需要前面提到的高内部电压) 所需时间更长,通常为 2 毫秒 (ms),消耗 150 微焦耳能量。虽然有这些大缺点,然而 NAND 闪存系统非常便宜,因此设计人员愿意牺牲这些 NAND 复杂的写入过程和高耗能代价来换取其低成本。

大多数智能手机和计算系统都混合使用 DRAM 和 NAND 闪存来满足其存储器和存储需求。在智能手机中,当手机处在开机状态时,DRAM 保存程序的副本以便执行,而 NAND 则在电源电源关闭时存储保存程序、照片、视频、音乐和其他对速度不敏感的数据。计算系统服务器将程序和数据存储在其 DRAM 主存储器中 (服务器不会关闭电源,除非停电),另外配置使用 NAND 闪存的 SSD 固态硬盘 (Solid State Drive) 进行长期和备份存储。

较小的系统可能使用 NOR 闪存代替 NAND 闪存,使用 SRAM 代替 DRAM,但前提是它们的存储器需求必需非常的小。NOR 闪存每个字节的成本比 NAND 闪存高出一个或两个数量级,而 SRAM 的成本比 DRAM 的成本高出几个数量级。

为何新型存储器能解决问题

前面提到各个因素造成现今使用之存储器的功耗问题,在许多目前正在开发的新型存储器技术中并不存在。此外,这些新型的存储器都是非易失性的,所以不需要刷新它们。与 DRAM 相比,这可以自动降低 20% 的功耗。由于它们都可以在不擦除的情况下覆盖旧数据,因此可以节省闪存所需的高擦除能耗,以及慢擦除周期引起的延迟 (该属性称为原位编程 (In-Situ Programming))。与闪存相比,这些新技术的写入过程能量要求非常低,减少或消除了对低效电荷泵的需求。最后,所有这些新技术都提供随机数据访问,减少了保留两个副本 — 一个在闪存,一个在 DRAM — 的需求。

不用说,无论何时使用任何新型的存储器技术来取代当今的传统 DRAM + NAND 闪存架构,所有这些属性都将带来显著的的功率节省以及性能提升。

一些新的存储器类型

我们将介绍的新型存储器类型包含下列几种。

大多数新型存储器技术拥有下列属性:

所有这些都是非易失性或持久性的,对比于需要定期刷新、高耗电量需求的 DRAM 具有明显的优势。

它们都不需要闪存所需的高电荷泵擦除/写入电压。

它们都没有使用闪存 (NAND 和 NOR) 所需的笨拙的块擦除/页写入方法,从而大大降低了写入耗电需求,同时提高了写入速度。

其中一些可以通过工艺来缩小尺寸进而降低成本,超越了当今根深蒂固的存储器技术:DRAM 和闪存。

选择器装置 (Selector)

许多这些存储器类型之间的一个重要差别是它们是如何被寻址的,这是通过位选择器 (Bit Selector) 进行的。有些选择器元件是晶体管 (Transistor),这会限缩存储器单元尺寸的微小程度。其他的使用二极管 (Diode) 或其他双端选择器元件,这能缩小存储器单元的大小,并有助于将存储器位堆叠成 3D 阵列。选择器类型影响这些存储器的成本,并且可能是生产这些元件的困难度的原因之ㄧ。

双端选择器单元可以获得理想的4f2单元面积,“f” 的是芯片制造工艺的最小特征尺寸 (Feature Size),4f2 单元是两倍最小特征尺寸的平方 (4f2 = 2f x 2f)。在 14nm 工艺上 (f =14nm),该数字为 2 x 14nm x 2 x 14nm 或 4 x (14nm)2。 4f2 存储单元单元面积是目前所有存储器可以制造的最小单元面积。基于晶体管的存储单元通常为 8f2,但在某些情况下,可缩小至 6f2。

使用双端选择器的存储单元具有另一个优点,也就是它们可以堆叠以进一步降低成本。而到目前为止,还没有公司试图堆叠使用晶体管选择器的存储单元。

双端选择器有两种类型:简单二极管和双向选择器。在这两者中,二极管更容易设计。

接下来我们就来介绍ㄧ些为解决这些问题所开发的新型存储器类型。

相变存储器 (PCM,Phase Change Memory)

相变存储器 (Phase Change Memory),也有人称之为 PRAM (Phase-change RAM),已经研究了几十年,Intel 联合创始人 Gordon Moore 早在 1970 年就发表了一篇描述早期原型的论文。相变存储器通过热能的转变,让相变材料在低电阻结晶 (导电) 状态与高电阻非结晶 (非导电) 状态间转换。也因为这理由,相变存储器也被归类在阻变存储器 (RRAM) 分类内。

图片来源 : Intel & Objective Analysis (Modified by Author)

PRAM 在执行置位 (Set) 和复位 (Reset) 功能时,电流是在相同方向上移动,因此可以使用简单二极管来做选择器装置,这使得 PRAM 更容易设计与生产,因为二极管比双向选择器简单多了。由于存储单元是构建在 CMOS 逻辑电路之上并且设计可用于堆叠,因此二极管选择器必须使用新材料,而不是将其构建在底层 CMOS 中。这增加了晶圆生产的层数,相对地增加了芯片的成本。

Intel 和 Samsung 于 2006 年生产第一款商用 PCM 芯片。 Intel 芯片持续生产多年,而 Samsung 芯片在停产前只有安装在的某ㄧ型号 Samsung手机中不到一年。被寄予厚望,由 Intel 和 Micron 合作开发,名为 3D XPoint (XPoint 发音为 “Crosspoint”) 的存储器,也是ㄧ种相变存储器 (虽然 Intel 否认它是 PRAM (或 RRAM),但逆向工程师 (Reverse Engineers) 分析其芯片后,都说它是)。 3D XPoint 旨在作为计算系统中 DRAM 与 NAND 闪存 SSD 之间的新增存储器层。

铁电存储器 (FRAM或FeRAM,Ferroelectric RAM)

铁电存储器,称为 FRAM 或 FeRAM,在 1987 年左右就已推出,但直到 20 世纪 90 年代中期才开始商业化。虽然叫做铁电存储器,FRAM 并非使用铁电材料。该名称源于这样的事实,即位存储机制的行为类似于铁磁存储的行为,也就是滞后 (Hysteresis),滞后是磁记录的基础。FRAM 的电压 - 电流关系具有可用于存储位的特征滞后回路。正电流将在移位时使位单元处于具有正偏置的状态,而负电流将该位单元的状态改变为负偏置。铁电位单元使用晶体进行存储,中心有一个原子。该原子位于晶体的顶部或底部。位存储是该原子位置的函数。

图片来源 : Objective Analysis (Modified by Author)

Ramtron 和 Symetrix 两家公司主导 FRAM 的开发,它们各自使用不同的材料,Ramtron 所使用的技术是基于一种称为铅锆钛 (PZT) 材料所形成的存储器结晶体。PZT 在半导体工厂中並不受欢迎,因为铅的高离子迁移特性会污染硅片。Symetrix 的专有材料虽然更复杂,却也遭遇了类似的问题。因此,新的铁电存储器材料持续在研发中。

FRAM 一个不幸的事实是其读取是破坏性的,每次读取后必须通过后续写入来抵消,以将该位的内容恢复到其原始状态。这不仅耗费时间,而且还使读取周期消耗的功率加倍,这对那些对功耗敏感的应用是一个潜在问题。然而 FRAM 独特的低写入耗电是其卖点。

1990 年 Ramtron 的合作伙伴 Fujitsu 将嵌入式 FRAM 量产用于地铁票价卡芯片。之所以选择 FRAM 是因为其独特的低写入能量,让芯片得以经由询问无线电信号就可为数据读写提供电源,而无需任何其他电源。

目前的 FRAM 存储单元是基于双晶体管,双电阻器单元 (2T2R),造成其尺寸至少是 DRAM 位单元的两倍。 1T1R 存储单元正在开发中,只有在开发完后,才能使 FRAM 成本接近 DRAM 的成本。

磁性存储器 (MRAM,Magnetic RAM)

磁性 RAM 或 MRAM 是磁记录技术的自然结果。事实上,MRAM 是最早期计算机的核心存储器,它被 SRAM 取代,然后在 1970 年代再被 DRAM 所取代。

最原始的 MRAM 称为 “Toggle MRAM” 或是 “SRAM 类型 MRAM”,它通过磁化和消磁位单元,强制它们进入不同的状态来读取它们。这样做所需的电流原本是可控制的,但到了大约 75nm 工艺节点,电流变得无法控制的高,因为电流保持不变,但导体随工艺缩小,导致电流密度高到无法接受。因此研究人员开始尝试新的方法,从 STT (Spin Torque Tunneling)开始,到 pSTT (Perpendicular Spin Torque Tunneling),现在大家所谈论的 STT-MRAM 都是 pSTT-MRAM。MRAM 技术还有ㄧ种 SOT (旋转轨道隧道),它采用三端式 MTJ 结构,将读取和写入路径分开,故比 STT-MRAM 具备更快的读写速度和更低的功耗,但目前仍处于研发阶段。

所有这些元件都是使用隧道层 (Tunneling Layer) 的 “巨磁阻效应” (Giant Magnetoresistive Effect) 来读取位单元:当该层两侧的磁性方向一致时,该层提供低电阻,因此电流大,但当磁性方向相反时,电阻会变很高,导致电流流量中断。基本单元需要三层或更多层的堆栈来实现,两个磁层 (Magnetic Layer) 和ㄧ个隧道层。

图片来源 : Avalanche Technology (Modified by Author)

STT MRAM有两种,一种是尺寸较小但速度较慢的单晶体管 (1T) 单元,另一种是尺寸较大但速度较快的双晶体管单元 (2T)。单晶体管 STT MRAM 每个单元需要一个晶体管和一个磁隧道结 (MTJ,Magnetic Tunnel Junction),称为 1T1R。它具有与 DRAM 相当的芯片尺寸,但其 200ns 的写入周期相对较慢。为了更快的类似 SRAM 的写入速度,设计人员使用具有两个晶体管的单元,称为 2T2R,以支持高速差分感测。然而,这会使得 MRAM 的芯片尺寸增加一倍以上,使其成本显着增加。

由于嵌入式 SRAM 面积太大,嵌入式 NOR 闪存无法继续跟随工艺缩小,STT-MRAM 越来越受到瞩目。 Everspin 跟 Global Foundries 结盟,UMC 和 Avalanche Technology 结盟,推广 STT-MRAM。它们跟 Samsung、TSMC 均已推出 2x nm 嵌入式 STT-MRAM,用以取代嵌入式 NOR 闪存。

IBM 刚发表的 19 TB SSD 则使用 Everspin 的 STT-MARM 取代 DRAM 来做为 SSD 的写入高速缓存 (Write Cache),主要是著眼于其非易失性的特性。因为 DRAM 是易失性的。因此需仰赖超级电容 (Supercaps) 在断电时来供应电能,使用 MRAM 可以免除这些笨重的超级电容器,这为 STT-MRAM 的应用又跨出ㄧ步。

STT-MRAM 被看好可以非常容易地扩展到 10nm 以下, 其可扩展性使 STT-MRAM 可能在未来几年成为低密度和中密度应用之 DRAM 和闪存的替代方案。

阻变存储器 (RRAM或ReRAM,Resistive RAM)

阻变存储器,称为 ReRAM 或 RRAM,包括许多不同的技术类别,其中包括氧空缺存储器 (Oxygen Vacancy Memories)、导电桥存储器 (Conductive Bridge Memories)、金属离子存储器 (Metal Ion Memories)、忆阻器 (Memristors)、以及,纳米碳管 (Carbon Nano-tubes),有些人甚至认为相变存储器也应该包括在这一类中。所有这些技术的共同之处在于存储器机制是由电阻器组成,依该电阻器处于高电阻或低电阻状态以表示 “1” 或 “0”。电流流过电阻器读取它,并使用更高的电流来覆盖它。其中,氧空缺 ReRAM 也被称为基于氧化物的 ReRAM (Oxide-based ReRAM),简称 OxRAM。

ReRAM 都承诺简化和缩小存储器单元,因为它们不一定使用晶体管作为选择器,而是使用在位单元上方或下方构建的双端选择器。这不仅应该将存储单元低降到其理论最小尺寸 4f2,而且还允许存储单元垂直堆叠,大大增加芯片密度,并可降低成本。

目前可用于生产的 ReRAM 有 Crossbar 的 40nm ReRAM、Adesto 的 130nm CBRAM 和 Panasonic 的 130nm TaOx ReRAM。Crossbar 和 Panasonic 的工艺已经可以嵌入半导体代工厂 CMOS 逻辑工艺中,而 Adesto 目前是作为离散芯片生产的。

Crossbar 的 ReRAM 中在两个电极间夹着一种金属氧化物材料,未编程的单元其纳米导电金属细丝 (小于 5 纳米宽的纳米导电金属细丝是由离子原子组成) 没有形成,所以不会传导电流。通过在正确方向上传递更高的电流,纳米导电金属细丝会形成,金属细丝几乎,但不完全,桥接两个电极。当一个小的读取电流以相同的方向通过单元时, 最后的间隙会被桥接,此时该位单元变为完全导通。一个小的反向读取电流会造成间隙无法密合,较大的反向电流则完全清除导电路径。Crossbar 目前与中芯合作生产其 40nm ReRAM,并且已经开始开发 1x nm 嵌入式设计。

图片来源 : Objective Analysis (Modified by Author)

Crossbar 的 ReRAM 单元是 “自我选择” 的,因为选择器本身就是单元的一部分,这使得单元像二极管ㄧ样运作,因此不需要选择器元件。这大大地简化了生产过程,因为单元是由单ㄧ个组合的 选择器元件 + 位单元 所组成,而其他 Re-RAM 技术需要与位单元分开的选择器元件。这是 Crossbar ReRAM 的最大优势。

Adesto 的 CBRAM (导电桥 RAM) 也是通过构建和摧毁导电细丝来创造电阻状态。但是不同之处在于,CBRAM 是将铜或银金属注入到硅中,从而在两个电极之间的硫属化物 玻璃绝缘体上形成导电桥,这个导电桥只有几个原子宽。正电流将银离子从单元的阳极移动到玻璃绝缘体中,形成导电通路。反向电流将这些银离子移回阳极,使导电桥断开并切断电流路径。

图片来源 : Adesto Technologies (Modified by Author)

Panasonic 将基于氧空缺的 ReRAM 集成到其 130 nm MCU 产品线中,并于 2017 年宣布与代工 UMC 合作,共同开发 40 nm工艺。

以上这些存储器是使用高电压将原子移入或移出位单元之玻璃绝缘体以形成或移除导电路径。另一个氧空缺 ReRAM 技术由 HP 开发,称为忆阻器 (Memristor)。尽管该公司证明这是 一次革命性的改变,不同于之前的任何技术,但仔细检查发现它只是氧空缺存储器的另一个名称而已。HP 之前的研究已经生产出四晶体管单元 (4T2R) 和一个晶体管单元 (1T1R),但该公司最近没有公布任何新消息。

另一种有趣的 ReRAM 类型是碳纳米管 (CNT,Carbon Nanotubes) 存储器。该存储器在硅衬底 (Silicon Substrate) 中使用碳纳米管的沉积膜 (或纤维) 来存储位。当电流在一个方向流过单元时,这些 纳米管压缩成高导电状态。当电流反转时,纳米管膨胀使得导电性降低。当电流移除后,编程的位单元保持在它们的压缩状态。Nantero 主导碳纳米管存储器的开发,因此该存储器也被称为 NRAM,并已授权给富士通作为 FRAM 的可能继承者,但 NRAM 尚未有样品问世。

图片来源 : Nantero

新型存储器技术的比较

表 1 比较了本白皮书中审查的元件。

也许这比较中最重要的因素是单元大小,因为这决定了成本。成本在存储器技术选择过程中非常重要 - 比较昂贵的技术通常被低成本的技术所取代,即使这种变化需要大量的解决方案。

选择器类型

使用晶体管作为选择器机制 (表中表示为 1T1R 或 2T2R) 的技术,会比使用双端选择器 (“1S1R” 中的 “S”) 或二极管 (1D1R) 的技术,具有较大的位单元尺寸 .Crossbar栏位中的 1TnR 指的是该公司的单元具有内置选择器元件,其行为类似于内部二极管。每个个单元组都需要一个晶体管,但这只会增加很小比例的单元有效尺寸。

选择器的创建会增加晶圆加工的复杂性,而复杂性会增加晶圆加工的成本。但是其影响并不是最大的,单元尺寸大小对存储器的成本具有更深远的影响,8f2 单元消耗的面积 是 4f2 单元的两倍,FRAM 的 30f2 单元消耗的面积是任何 4f2 技术的 7.5 倍。

单元大小不仅决定了存储器的成本,还限制了在给定区域内可以产生的最大存储器容量。许多嵌入式设计具有有限的芯片面积可用于片上存储器。那些具有最小单元尺寸的存储器在给定的空间量内支持最大的存储密度。

永久性 (Persistence)

与现有技术相比,所有这些技术都是非易失性的,是 DRAM 所沒有的重大优势,并且它们都支持原位编程 (In-Situ Programming),这使得它们比 NAND 或 NOR 闪存的编写速度快得多。

可扩展性 (Scalability)

另一个重要的考虑因素是该技术的可扩展性。某些新型的存储器技术,特别是 FRAM 和 PCM,已经面临挑战。但 FRAM 还没有成功地在 90nm 以下成功缩放,PCM的 “on” 电阻会随着单元尺寸的缩小而增加,使得该技术在工艺缩小时面临不少杂音,虽然 PCM 研究人员在十年前成功就已开发出 5nm 的单元。

氧空缺 ReRAM 据称在缩放到 10nm 以下时会遇到问题。Adesto的导电桥技术和Crossbar 的纳米导电金属细丝技术预计可以做到10nm以下。

工艺复杂性

PCM (Intel 的 3D XPoint 存储器) 和 Crossbar 的导电金属细丝存储器在这方面具有优势,因为 它们的选择器元件比其他技术更简单。Crossbar 的选择器包含在位单元内,而 PCM 在同一方向上使用电流进行置位,复位和读取操作,因此它只需要一个简单的二极管 (二极管)。在这两个中,Crossbar 单元的工艺更简单,由于没有选择器元件,它所需的沉积层更少。

缺点

所有这些新型存储器技术与当今稳固的存储器技术相比,确实存在一些缺点:没有ㄧ种速度可以像 SRAM 及 DRAM 那样快。而且,在未来几年之内,没有任何ㄧ种可以在成本上与 NAND 闪存竞争,主要原因是来自经济规模。

在嵌入式应用中,我们通常使用 NOR 闪存来存储代码和数据,但嵌入式 NOR 闪存无法跟上先进工艺持续缩小单元尺寸,而这些新型技术提供了超越嵌入式 NOR 扩展限制的方法。对于那些无法使用 NOR 闪存而必须使用替代技术的应用,通常是依据添加到芯片的成本来选择新技术。因此这些应用将倾向于使用能提供最小单元尺寸,以及,晶圆加工成本增加最少的技术。

结论

因工艺的限制及功耗的考量,存储器产业已进入一个必须评估及发展替代技术的时代。几十年来,研究人员一直在研究几种新型存储技术,这些技术争相竞争,希望成为一个可以取代嵌入式 NOR 闪存,甚至 DRAM,的新存储器技术。

本文重点介绍了ㄧ些新型存储器技术,并探讨它们在扩展到最先进的工艺节点,以及,在可承受的制造成本下,保持引人注目的性能上所面临的限制。存储器公司和半导体代工厂正在密切合作,共同开发并将嵌入式存储器扩展到大规模生产。使用标准 CMOS 材料和简单的制造加工步骤和工具,在竞争激烈的市场中获得成功的机会将会最大。

虽然本文提供了为什么某些技术比其他技术更具有获得成功的原因,但最终采用者和存储器IP 提供商与制造合作伙伴之间战略协作的优势,将决定哪些技术将成为非易失性存储器的新选择。

-

h1654156006.2372

2020-08-15

0 回复 举报“虽然叫做铁电存储器,FRAM 并非使用铁电材料。”纠正这里的错误,虽然叫铁电存储器,但人家是不含铁元素!铁电材料是肯定要使用的! 收起回复

h1654156006.2372

2020-08-15

0 回复 举报“虽然叫做铁电存储器,FRAM 并非使用铁电材料。”纠正这里的错误,虽然叫铁电存储器,但人家是不含铁元素!铁电材料是肯定要使用的! 收起回复

-

由浅入深介绍各种新型存储器2017-10-19 11273

-

相变存储器(PCM) :新的存储器技术创建 新的存储器使用模式2018-05-17 3467

-

存储器的分类及原理2008-08-17 1150

-

几种新型非易失性存储器2006-03-24 3022

-

相变存储器:能实现全新存储器使用模型的新型存储器2009-12-31 1522

-

光存储器,光存储器特点和常用类型有哪些?2010-03-20 6901

-

相变存储器(PCM)与存储器技术的比较2010-11-11 2692

-

Xilinx 新型FPGA:拥有最高存储器带宽,能将存储器带宽提升 20 倍2018-07-31 3162

-

新型存储器有望取代动态随机存取存储器和闪存驱动器2019-06-25 3835

-

新型存储器难大量生产的原因是什么2019-12-31 1232

-

新型存储器与传统存储器介质特性对比2020-04-25 3619

-

存储器和新兴非易失性存储器技术的特点2020-06-09 1775

-

浅谈MCU中集成新型存储器的选择2022-12-01 1521

-

IEDM 2022上的新型存储器简介2023-02-14 3421

-

一文了解新型存储器MRAM2023-04-19 5035

全部0条评论

快来发表一下你的评论吧 !