矿机中的芯片封装设计方案

电子说

描述

随着时代的发展,越来越多的技术伴着EDA工具的不断完善以及工作的细分,从前觉得很专业的事情,现在变得门槛越来越低,闲下来的时候想想如果我依然只会画画原理图,画画PCB,那么迟早会被更加有精力、更加专业的人替代就觉得心慌。比如五年前,我当时能够完成一拖8的DDR3设计,在当时可以靠这个混口饭吃。然而现在你在去看,满大街的layout工程师,他们比我有精力、比我更渴望学习、比我更加容易接受新的EDA工具和新的设计理念。因此我必需给自己找条更好的路,让自己的技术更加丰富起来,更加有能力去解决一些在当下很多人无法解决的问题。 我觉得在未来,底层的layout也好,数字电路设计也好,基本一个普通的大专生培训3个月就可以非常轻松的上手,毫不夸张的说,只要你懂欧姆定律,就可以实现一个平板电脑的设计,因为现在的很多功能都已经sip到了芯片内部去了,哪怕是模拟的RF部分,现在也将LNA、SWITCH等等射频电路集成了,前端只有做个天线的阻抗匹配即可,所以你可以看到,其实技术依然在,只是越来越多的活被做芯片人干掉了,所以我以时俱进,去干一干系统集成的一个部分:如何通过芯片级的设计去解决一些板级发生的问题。

在研究挖矿机的时候,我发现了一个比较严峻的问题:

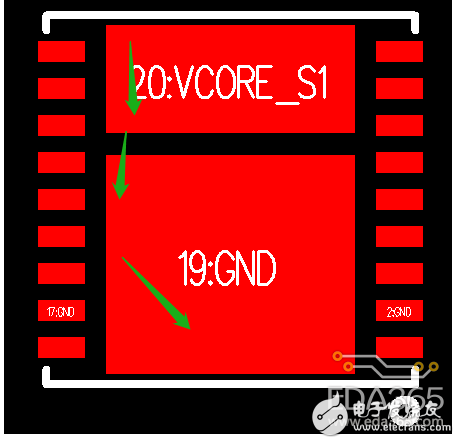

由于芯片的电流非常的大,传统的芯片VCC和VSS的焊盘设计见下图:

上图设计,工程师一般要把DIE放置在VSS焊盘上,因此我们会看到,电流的流通路径必然会是从VCC焊盘取电,然后通过基板在通过DIE的BALL传递到内核,在经过die的BALL传导到基板在下到PAD在回到电源负极,见图,

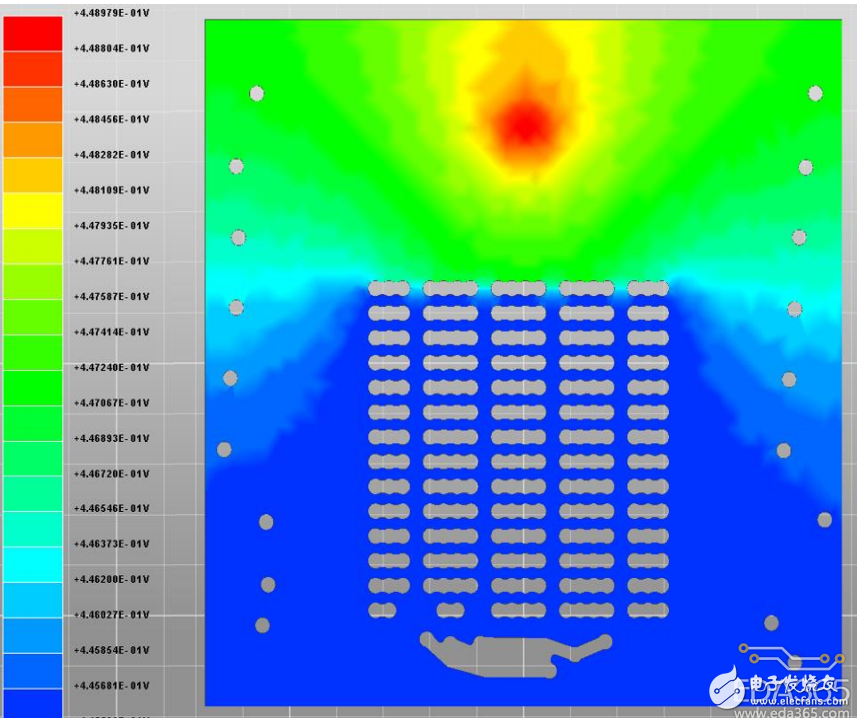

如果电流很小,那么我么可以不用考虑这个路径上的阻抗导致的drop。然而BTC的芯片过电流往往会是30A以上,因此我以30A模拟仿真了下数据,可以发现一些端倪:

上图可以看到,红色部分为VCC焊盘下方,设置的输入源,我们看IR-DROP可以看到,在DIE的下端明显压降远远大于上端。这就会造成一个问题:DIE下端的单元获取到电压会低于上端电压,进而如果按理论VCC=0.5V供电会导致下端的计算单元的正确率低于上端,如何解决该问题呢?一个简单的办法就是加压:把电压抬高到下端能够达到0.5V,但是这样造成一个新问题:上端的单元供电电压偏高进而造成功耗增大。。 ^. E’ W“ |; Z$ u

以上问题,如果是一个原理工程师或者PCB工程师或者单纯的substrate工程师都可能无法真正的认识到并做出改进,因为实际上对于封装工程师而言,也许他不会意识到系统设计上的大电流给后端造成的困扰,而原理图工程师由于不清楚封装设计原理从而无从下手,很好,我发现我可以做这件事,因为我既懂得板级设计又懂芯片设计,应该有机会靠这个混碗饭吃。1 p& Q” \/ C3 E4 r

如何改进改办法呢?我们还是要分析一下,用的知识点不懂,就是欧姆定律:压降大原因是阻抗大,为什么阻抗大?是因为过电流层只有基板上的铜,而这个铜一般只有30um,在30A的电流下,催生了如此大的压降。因此改进点就是:如何降低路径上的阻抗。方法如下:- S4 M. P5 a2 ` {。 x8 d9 v/ j

1、基板加层。我去,太贵了。

2、基板铜厚增加,一样,太贵了。

3、减短路径。

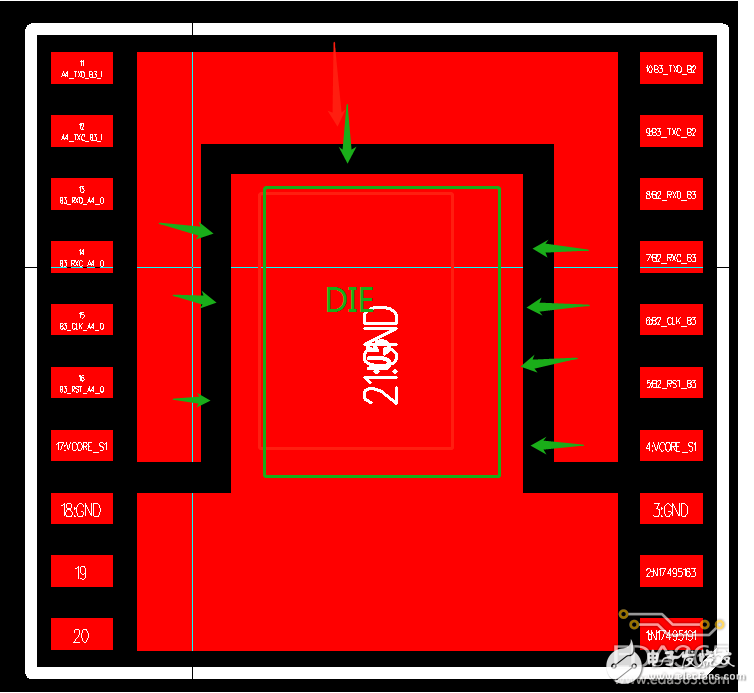

我考虑了下,第三个办法应该是可行的,如何减短路径?我把焊盘重新调整了下:

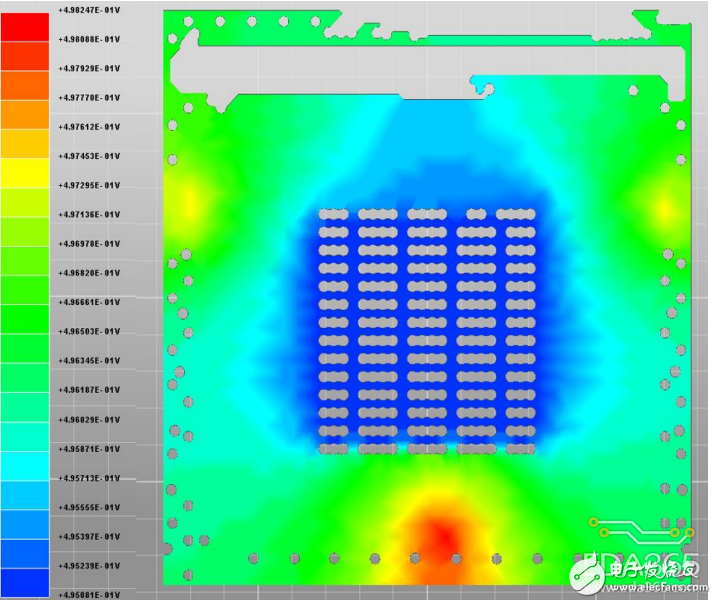

上图的改进点在于,我将电源的焊盘延伸下来了,由于PCB铜厚可以做的2OZ,因此可以大大减小路径阻抗,同时由于四周都进电源,也能侧面减小路径,看一下仿真图:

结果果然:very good!

真想做一下这个测试,可惜做一个16nm的芯片从RTL设计到板级 没有2000万是下不来了,遗憾没有办法实际来验证一下这个结论。然而从这里有可以看到,越往芯片级的设计,越需要设计者考虑的更加的充分,做好仿真,通过理论和仿真进行对比,进而做出最优的设计,因为你再也不敢说:错了没事,咱在打一板不就得了。

-

如何制定芯片封装方案2025-04-08 1248

-

如何通俗理解芯片封装设计2025-03-14 2279

-

深度解读芯片封装设计2025-03-06 1875

-

为什么需要封装设计?封装设计做什么?2024-04-16 2012

-

半导体后端工艺:封装设计与分析2024-02-22 2664

-

RedEDA使用教程(芯片封装设计RedPKG)2023-11-13 732

-

全球范围内先进封装设备划片机市场将迎来新的发展机遇2023-10-18 1526

-

芯片封装设计2023-06-12 3313

-

为什么需要封装设计?2023-03-15 1651

-

芯片封装设计中的wire_bonding知识介绍2012-01-13 48738

-

SMT电路板安装设计方案2010-03-29 1899

全部0条评论

快来发表一下你的评论吧 !