STM32单片机APB1和APB2的区分

控制/MCU

描述

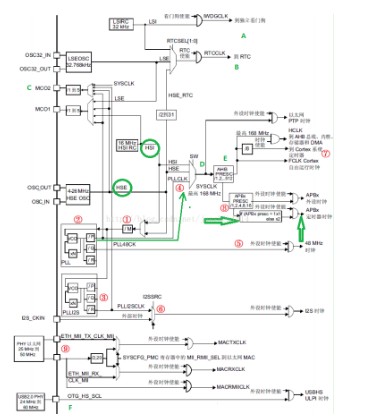

1.首先注意的的是图中画绿色圈圈的两个,HSE和HSI分别表示外部时钟和内部时钟,其中HSE 是是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,HSE 也可以直接做为系统时钟或者 PLL 输入(从红圈4处可以看出),频率范围为 4MHz~26MHz。STM32默认为25Mhz,像原子的板子就是8Mhz的,所以移植时一定要格外注意。

2.注意红圈2代表的部分,这里是主锁相环倍频输出,用于产生系统需要的高速时钟信号,如图绿色箭头所示(STM32还有一个副锁相环,如红圈3)

主 PLL 时钟的时钟源要先经过一个分频系数为 M 的分频器,然后经过倍频系数为 N 的倍频器出来之后的时候还需要经过一个分频系数为 P(第一个输出 PLLP)或者 Q(第二个输出 PLLQ)的分频器分频之后,最后才生成最终的主 PLL 时钟。例如我们的外部晶振选择 8MHz。同时我们设置相应的分频器 M=8,倍频器倍频系数 N=336,分频器分频系数 P=2,那么主 PLL 生成的第一个输出高速时钟 PLLP 为:PLL=8MHz * N/ (M*P)=8MHz* 336 /(8*2) = 168MHz(来源:正点原子)

3.区分APB1和APB2

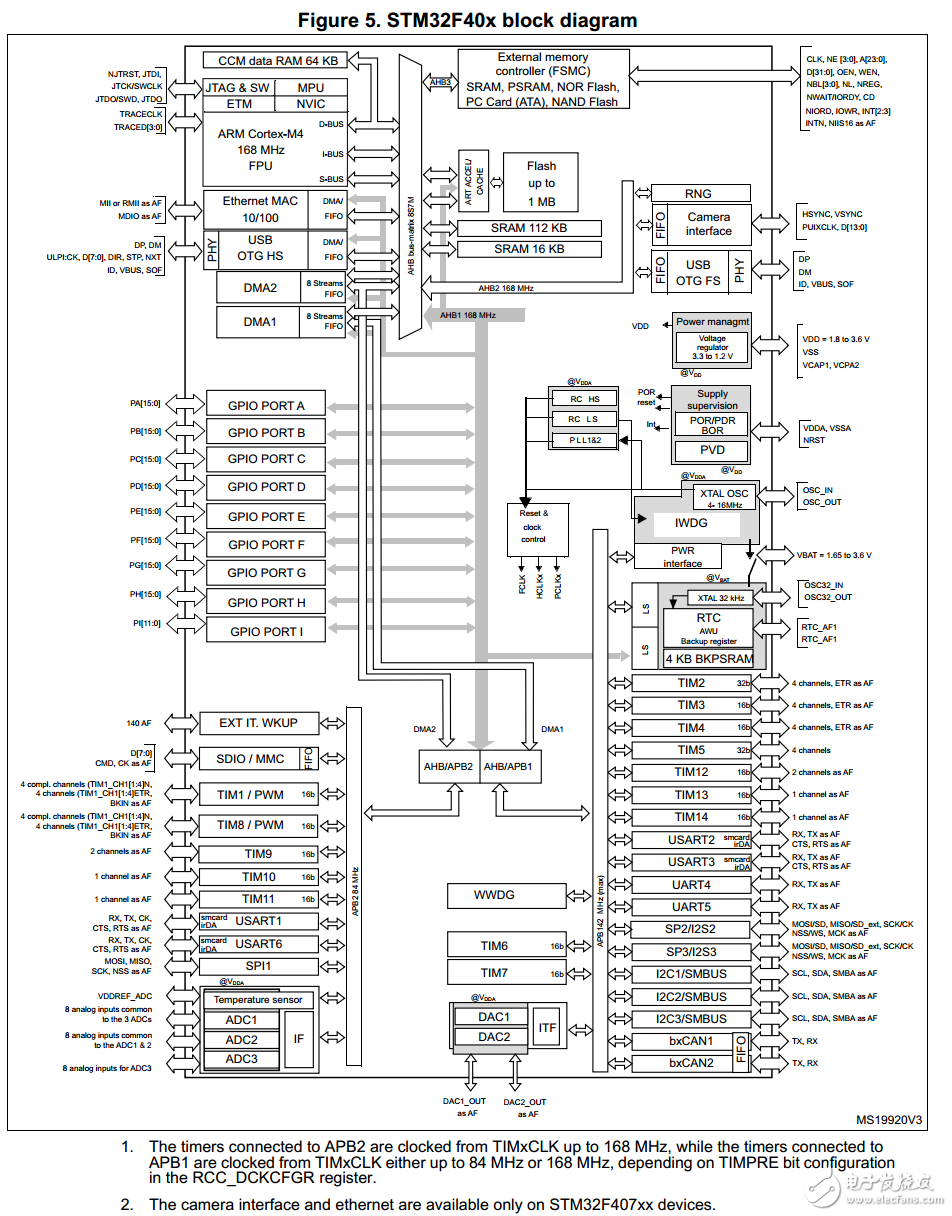

如红圈8表示的位置,STM32F4 很多外设的时钟来源,即两个总线桥: APB1 和 APB2,其中 APB1是低速总线(最高 42Mhz),APB2 是高速总线(最高 84Mhz)。另外定时器部分,如果所在总线( APB1/APB2)的分频系数为 1,那么就不倍频,如果不为 1(比如 2/4/8/16),那么就会 2 倍频( Fabpx*2)后,作为定时器时钟输入。

简单点说,举个APB1的例子,系统时钟是168Mhz,APB1分频系数为4(system_stm32f4xx.c配置),则APB1速度为42Mhz,但是挂靠在在该总线上的定时器3,由于分频系数4而不是1,因此定时器输入频率为42Mhz x 2 =84 Mhz,具体详见这篇文章点击打开链接

4.AHB总线频率

见图

-

stm32定时器的时钟可以不来自主频的APB1或APB2吗,选择外部的32K晶振可以吗?2024-04-03 344

-

怎样去区分STM32单片机的APB1和APB2呢2022-02-21 1715

-

使用J-Link-RTT打印STM32系列APB1/APB2/HCLK/SYSCLK时钟频率2022-01-25 880

-

使能APB2上的GPIOC时钟原因2022-01-05 1498

-

STM32单片机APB1和APB2的区分2021-12-27 1609

-

stm32f103的APB1和APB2有哪些不同之处呢2021-12-14 2406

-

STM32F1xx 外部晶振为12MHZ,设置系统时钟(SYSCLK),APB2(PCLK2),HCLK为72MHZ2021-11-23 731

-

APB1和APB2的对应外设2021-08-18 1733

-

STM32的时钟系统APB22021-08-12 1481

-

AHB系统总线分为APB1和APB22021-08-05 3053

-

STM32单片机的学习笔记30条合集免费下载2019-11-11 970

-

STM32F030的APB1和APB2时钟中断溢出时间不一样2019-01-29 7373

-

STM32单片机定时器的时钟源设置2018-12-18 9108

-

超详细的STM32单片机学习笔记汇总2018-07-26 26068

全部0条评论

快来发表一下你的评论吧 !