STM32单片机的外部时钟晶振该如何选择频率

控制/MCU

描述

芯片的主晶振频率范围一般来说在数据手册(Datasheet)和技术参考手册(Technical Reference Manual)中都有介绍。

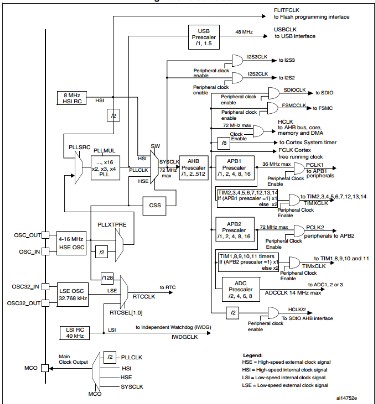

你提到的时钟先分频再倍频,这个需要深入到STM32的内部去一探究竟了,在其技术参考手册的第7.2节Clocks的一开始有一个表格,时钟树(Figure 8. Clock tree),它完全地列出来STM32这个芯片内部各个模块的时钟来源以及相关的从属关系。

在这个图的正中央,有一个核心时钟:SYSCLK,它最大频率是72MHz,它的时钟信号通过选择器SW可以由PLLCLK提供(也可由HIS、HSE提供)。

PLL,毫无疑问,它是用来倍频的,可以*2,*3,*4……*16,它的时钟信号通过选择器PLLSRC可以由8MHz的高速内部RC振荡器经过二分频提供,也可由PLLXTPRE的选择器输出提供,而PLLXTPRE的选择器就接的是我们的8MHz的高速外部时钟(直接接入或二分频接入)。

总的来说,对于我们这个板子,若使用高速外部时钟给STM32内核提供时钟源,一般以下两条路:

① [高速外部时钟:8MHz]>>>[不分频:8MHz]>>>>[PLL倍频,2到16倍]>>>[SYSCLK,16MHz-128MHz]

②[高速外部时钟:8MHz]>>>[二分频:4MHz]>>>>[PLL倍频,2到16倍]>>>[SYSCLK,8MHz-64MHz]

我们注意到,在8MHz外部时钟给PLL之前若分频的话,那么最大(×16)才64MHz,因此,我们都会给PLL以8MHz的时钟源让其倍频,这样能使它发挥到72MHz的高频率

正因如此,系统时钟总是8的倍数。

我们看这个芯片的数据手册,立刻就能明白,不是必须得接8MHz的晶振的

①高速外部时钟源频率范围(P55-P58):1MHz~25MHz(有源);4MHz~16MHz(无源)

②PLL输入时钟源频率范围(P62):1MHz-25MHz

③PLL输出时钟源频率范围(P62):16MHz~72MHz

我们自己设计板子的时候只要满足它的范围就可以了。

例如:我们可以选择一个12MHz的无源晶体接到STM32芯片上。

在给STM32进行时钟配置的时候,

①选择PLLXTMRE的输入源为12MHz/2 = 6MHz

②选择PLLSRC的输入源为PLLXTMRE的输出6MHz,

③在PLL内进行3到12倍的倍频(最小16MHz,最大72MHz),

最终我们可选择的频率就有:18MHz、24MHz、30MHz、36MHz、42MHz、48MHz、54MHz、60MHz、66MHz、72MHz

图示:

-

单片机的内外部晶振,到底有什么区别?2024-01-24 8050

-

STM32使用内部晶振还是外部晶振?2023-12-15 8784

-

单片机的晶振频率怎么选择?2023-10-25 696

-

STM32单片机外部晶振内部晶振配置2021-12-24 4505

-

选择外部时钟晶振频率的方法2021-11-25 1304

-

关于外部时钟晶振频率选择2021-11-16 1253

-

RCC时钟晶振在单片机中的作用2021-08-23 1469

-

单片机晶振概述及工作原理2021-05-18 10419

-

为什么手按住晶振后单片机就能工作了?2020-10-13 6729

-

如何判断单片机晶振是否工作及问题排除2019-10-27 15907

-

STM32单片机外部晶振配置时钟设置2018-10-12 36296

-

单片机为什么需要晶振2018-09-06 76141

-

晶振对于单片机的影响分析2017-12-21 13095

全部0条评论

快来发表一下你的评论吧 !