fido5100和fido5200 REM交换芯片与主机和网络处理器配合使用

工业以太网

描述

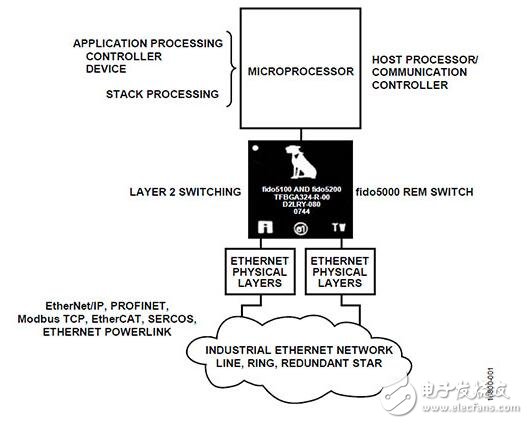

在工业自动化和运动控制应用中,工业以太网设备的使用正在成为现实,取代了CANbus或RS-485等传统现场总线连接。

处理实时应用需要高度的确定性和可靠性,主要原始设备制造商(OEM)引入了许多协议,例如Profinet、EtherCAT、Ethernet/IP、Sercos和Modbus TCP。兼容这些协议,以及需要更新以兼容未来增强功能(如时间敏感网络(TSN))的可能性,是每个工业通信设计的重要考虑因素。ADI公司通过实时以太网多协议(REM)交换芯片fido5100和fido5200支持最常见工业以太网协议。此交换芯片与fido1100通信控制器配合使用,使可编程多协议RAPID方案更加完善。fido5100和fido5200 REM交换芯片为Profinet IRT、EtherCAT、Ethernet/IP、Modbus TCP和Powerlink提供预认证的解决方案。

本应用笔记介绍fido5100和fido5200 REM交换芯片与任何微处理器的主机接口,另外还说明了存储器总线接口以及控制以太网接口所需的附加信号。

在本文中,低电平有效信号用上横线和信号名称来表示(例如RESET))。

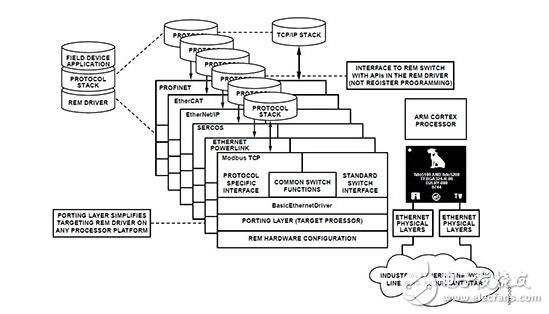

图1.基于fido5100和fido5200的工业以太网设备架构和支持的软件协议栈

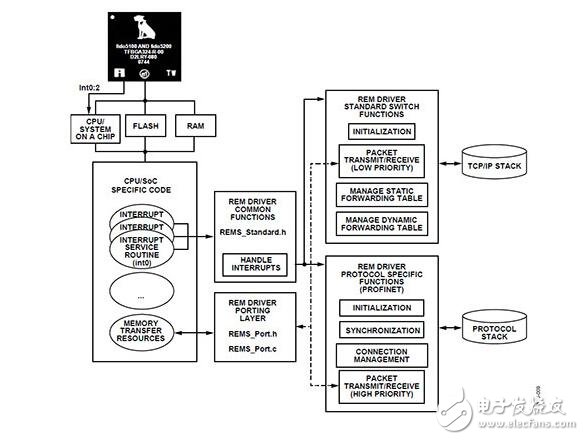

主机接口

fido5100和fido5200 REM交换芯片通过一个设计为标准异步存储器总线端口的主机接口连接到通信处理器。他们各有两个以太网接口,支持介质独立接口(MII)或精简介质独立接口(RMII)。由于以太网物理层配置差异性,所以交换芯片不处理以太网物理层部分。通用架构如图2所示。

图2.通用架构

主机接口为16位或32位存储器总线,地址和数据可以复用,从而减少引脚数量。多路复用总线选择(MBS)和数据总线大小(SIZE_32)信号选择此总线模式。MBS和SIZE_32在RESET)信号的上升沿采样。

另一个要考虑的方面是字节序,它由从小到大顺序(LE)信号决定。LE电平也是在RESET)的上升沿采样。

交换芯片数据总线定义如下:

•D0为最低有效位(LSB)。

•D15为16位总线的最高有效位(MSB)。

•D31为32位总线的MSB。

所有控制和状态寄存器都是16位宽,所以即便使用32位总线,数据也必须按D15到D0的顺序传输。有关如何处理字节序的详细信息以及引脚功能的详细描述,请参阅fido5100/fido5200数据手册。

地址总线有四位数据,可以访问16个直接地址寄存器。如果是非多路复用数据总线(例如MBS = 0),用户必须考虑地址的另外四个引脚。

查看时序图(参见fido5100/fido5200数据手册)非常重要,它显示了非多路复用和多路复用模式下的读写操作。

图3.同相缓冲器驱动CS)信号

在非多路复用操作的情况下,地址建立时间(tAS)是异步存储器访问的关键参数。根据微处理器架构,地址线和CS)可以同时驱动(tAS = 0),或者二者之间可以有一个很小的延迟。

关于非多路复用操作,市场上的许多Cortex®-M4系列(例如ADI公司ADSP-CM408F或STM32F4)和Cortex-Ax系列(例如ADI公司ADSP-SC589和NXP imx6)可无延迟地驱动CS)和地址线。在其他情况下,如Motorola 68000架构,CS)在地址线有效后置位。

fido5100和fido5200 REM交换芯片使用CS)下降沿来锁存地址线,并且需要一个很小的延迟tAS(最小20 ps)。

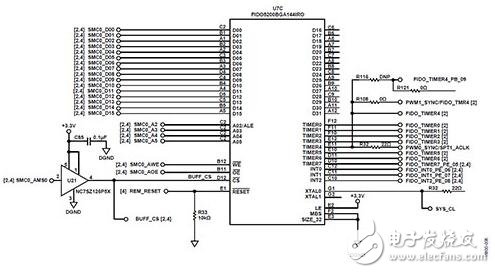

当微处理器同时置位CS)和地址时,应给CS)增加几ns的延迟。例如,ADSP-CM408F通过一个快速的单通道同相缓冲器(通常增加2.5 ns的延迟)将CS)驱动到fido5100和fido5200 REM交换芯片。

对于多路复用存储器访问,地址和ALE信号有效之间的时序关系也可能要求在ALE信号上增加一个短延迟,这取决于所使用的处理器。

中断

三条中断线用作fido5100和fido5200 REM交换芯片的输出。主机微处理器必须监视这些线路。

MDIO接口

所有以太网物理层都需要配置,它们可以提供状态信息。许多器件使用管理数据输入和输出(MDIO)接口。此通信接口由两条线组成:一条数据线(MDIO)和一条管理数据时钟线(MDC)。IEEE802.3规范定义了一个特定通信协议。fido5100和fido5200REM交换芯片不驱动此通信接口。主机处理器必须能够相应地管理MDIO和MDC。

存储器要求

理想情况下,REM交换芯片驱动器需要50 kB到100 kB的只读存储器(ROM)。在RapID平台上,fido1100使用46 kB ROM。此外,某些工业以太网协议需要8 kB RAM来同时处理飞行中处理器的多个数据包。

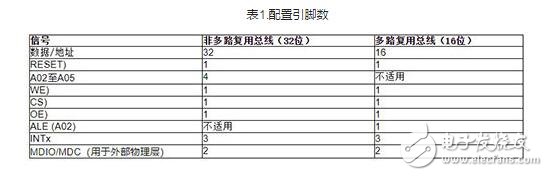

引脚数

表1总结了使用最大引脚数(125 MB/s,非多路复用总线)的配置的引脚数和使用最小引脚数(62.5 MB/s,多路复用总线)的配置的引脚数,假设MBS、SIZE_32和LE处于某一固定电平。非多路复用总线中有45个引脚,多路复用总线中有26个引脚。

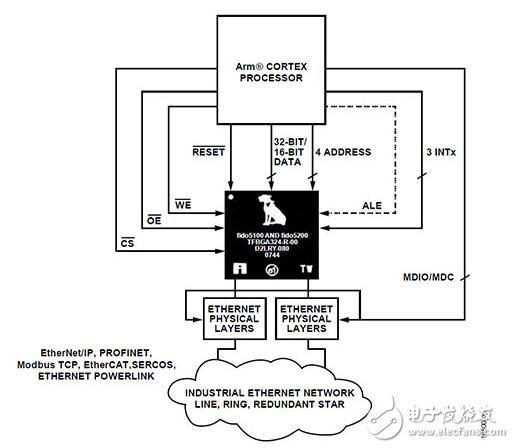

互连框图

图4显示了主机或网络处理器与fido5100和fido5200REM交换芯片之间以及两个以太网物理层的完整互连框图。图4中的虚线表示仅用于多路复用模式的连接。在多路复用模式下,请勿连接四条地址线,只能连接A02/ALE。A02/ALE具有双重功能。在多路复用模式下,A02线充当ALE信号来验证地址线。

图4.互连框图

REM交换芯片软件驱动程序

REM交换芯片软件驱动程序为fido5100和fido5200提供标准的与协议无关的接口。软件驱动程序用于初始化、中断管理、定时器管理以及独立于协议的数据包传输和接收。针对每种支持的协议(Profinet、Ethernet/IP、EtherCAT、ModbusTCP和POWERLINK),REM交换芯片软件驱动程序以源代码形式提供。驱动程序使用C语言编写,并针对选定的协议配置交换芯片。固件从主机处理器下载。

配置通常在上电时执行,但配置可在系统复位后的任何时间执行。

如图5所示,C代码被组织成一组应用程序编程接口(API),分为两个主要功能组别:协议专用接口和标准交换接口。

任何传输控制协议/互联网协议(TCP/IP)协议栈都可以连接到标准交换接口,任何协议栈都可以连接到协议专用接口。标准交换接口在所有驱动程序中都是通用的,因此用户只需连接到TCP/IP协议栈一次即可。

用户可以选择作为处理器开发环境的操作系统(OS)一部分的TCP/IP协议栈,以及来自第三方供应商的PROFINET协议栈。然后,协议栈由主机处理器管理,并连接到REM交换芯片驱动程序中的协议特定API,而REM驱动程序中的标准交换API连接到OS中的TCP/IP协议栈。

图5.多协议能力

驱动程序不依赖于任何操作系统资源(例如无线程和令牌),所以移植仅限于定义主机处理器如何与REM交换芯片通信以及一些调试选项。

移植相关代码(REMS_Port.h和REMS_Port.c)位于Porting目录中(/Porting/inc/和/Porting/src/)。为支持特定硬件平台,必须修改这两个文件,其依赖于主机处理器。

REM软件驱动程序架构如图6所示。

图6.REM软件驱动程序架构

应用范例

本部分包含一些与工业应用中常用的微处理器架构配合使用的范例。有关更多信息,请参阅相应集成电路(IC)制造商提供的具体文档。

ADI公司ADSP-CM408F(带FPU的Arm® CORTEX-M4)

ADSP-CM408F带有一个灵活的外部存储器接口。静态存储器控制器(SMC)可以编程为控制最多四组外部存储器。允许异步非复用16位操作。

表2显示了fido5100和fido5200 REM交换芯片与ADSP-CM408F处理器之间的连接。

表2.连接至ADSP-CM408F

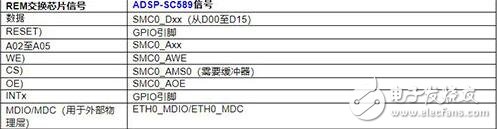

ADI公司ADSP-SC589(带ARM CORTEX-A5的SHARC®+双核DSP)

ADSP-SC589配有SMC,可控制最多两个外部存储器模块。允许异步非复用16位操作。正如ADSP-CM408F中所建议的那样,CS)信号需要一个外部缓冲器,MDIO接口由嵌入式控制器管理。

表3显示了fido5100和fido5200 REM交换芯片和双核SHARC+Arm处理器之间的连接。

由于ADSP-SC589没有嵌入式闪存,因此处理器需要在上电时对REM交换芯片进行编程以从外部ROM下载代码。

表3.连接至ADSP-SC589

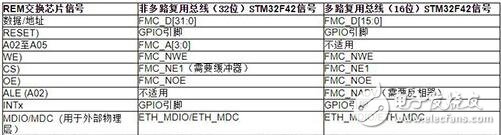

ST MICROELECTRONICS STM32F42系列(带FPU的ARM CORTEX-M4)

STM32F42系列具有灵活的内存控制(FMC)接口,允许异步16位和32位多路复用和非多路复用访问操作。由于FMC_NE(片选)预测地址有效的时间最长可达2 ns,因此该信号可能需要更长的延迟时间。

表4显示了fido5100和fido5200 REM交换芯片与STM32F42处理器之间的连接。

表4.连接至STM32F42

在多路复用操作的情况下,需要一个反相器,因为FMC_NADV是低电平有效信号,但fido5100和fido5200需要高电平有效信号来锁存地址。这种情况下无需增加延迟,因为tw (NADV)时间足以让fido5100和fido5200锁存地址线。

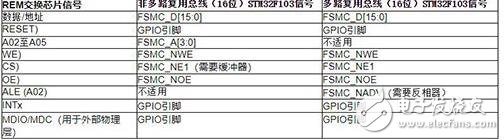

ST MICROELECTRONICS STM32F103系列(Arm CORTEX-M3)

STM32F103系列具有灵活的嵌入式静态存储控制器(FSMC),可以管理最多四组不同类型的存储器,包括SRAM。FSMC允许异步多路复用和非多路复用16位操作。由于FSMC_NE(片选)可以在地址线有效之前最多3 ns时置位,所以此信号可能需要更长的延迟时间。

表5显示了fido5100和fido5200REM交换芯片与STM32F103处理器之间的连接。

表5.连接至STM32F103

在多路复用操作的情况下,需要一个反相器,因为FSMC_NADV是低电平有效信号,但fido5100和fido5200需要高电平有效信号来锁存地址。这种情况下不需要增加延迟,因为tw (NADV)时间足以让fido5100和fido5200锁存地址线。

该系列Cortex-M3处理器未实现MDIO接口。

尽管如此,可以使用两个GPIO来代替,而MDIO功能必须通过软件来模拟。

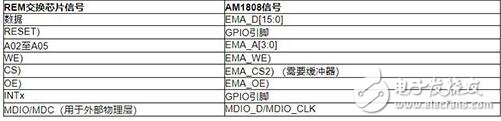

TEXAS INSTRUMENTS AM1808 SITARA系列(Arm9)

AM1808有一个支持异步SRAM的外部存储器接口(EMIFA)。EMIFA可以管理16位非复用访问。片选信号需要一个缓冲器。

表6显示了fido5100和fido5200 REM交换芯片与AM1808处理器之间的连接。

表6.连接至AM1808

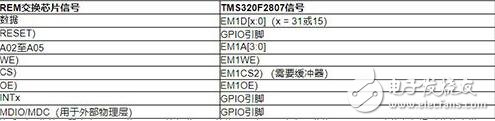

TEXAS INSTRUMENTS TMS320F2807 PICCOLO系列(32位浮点微控制器)

TMS320F2807系列具有支持异步SRAM的EMIFA。EMIFA可以管理32位和16位非复用访问。片选信号需要一个缓冲器。

表7显示了fido5100和fido5200 REM交换芯片与TMS320F2807处理器之间的连接。

表7.连接至TMS320F2807

该系列32位处理器未实现MDIO接口。尽管如此,可以使用两个GPIO来实现此接口,而MDIO功能必须通过软件来模拟。

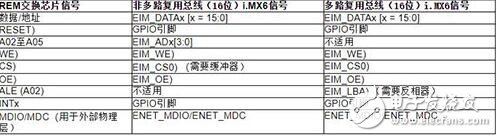

NXP i.MX 6ULL系列(Arm CORTEX-A7)

i.MX 6ULL处理器配有外部接口模块(EIM),其可提供对SRAM的16位非复用和复用访问。

表8显示了fido5100和fido5200 REM交换芯片与i.MX 6ULL处理器之间的连接。

表8.连接至i.MX 6ULL

在多路复用操作的情况下,需要一个反相器,因为EIM_LBA)是低电平有效信号,但fido5100和fido5200需要高电平有效信号来锁存地址。

因为EIM_LBA)解除置位(成为地址的锁存时间)取决于可编程参数,所以计算W40A时序时要小心。可能需要缓冲器。

时序W31(EIM_CSx)有效至地址有效)是可编程的,可以为负值(CS)在地址有效前置位)。可能需要缓冲器。

-

fido5100/fido5200实时以太网多协议(REM)交换机技术手册2025-05-15 1729

-

FIDO5100 adi2025-03-11 153

-

绍fido5100和fido5200 REM交换芯片与任何微处理器的主机接口2023-11-23 446

-

fido5100和fido5200 REM交换芯片与主机和网络处理器使用2023-11-22 575

-

fido5000:一个芯片,多种以太网协议2023-03-06 2022

-

ADI的fido5100 / fido5200如何与许多不同的协议连接?2021-06-30 2266

-

FIDO5100FIDO5200 IBIS型号2021-06-02 654

-

FIDO5100/FIDO5200:实时以太网多协议(REM)交换机产品手册2021-05-11 999

-

AN-1554:fido5100和fido5200 REM交换芯片与主机和网络处理器配合使用2021-03-21 716

-

FIDO5100/FIDO5200 IBIS Model2021-02-04 621

-

请问fido5100芯片内核集成了协议栈吗?2019-01-30 3160

-

工业网络的要求是什么?fido5000的应用介绍2018-10-31 2782

-

fido5000一颗支持多种以太网协议的芯片2018-10-22 3799

全部0条评论

快来发表一下你的评论吧 !