基于FPGA自适应数字频率计的设计

FPGA/ASIC技术

描述

在电子工程,资源勘探,仪器仪表等相关应用中,频率计是工程技术人员必不可少的测量工具。频率测量也是电子测量技术中最基本最常见的测量之一。不少物理量的测量,如转速、振动频率等的测量都涉及到或可以转化为频率的测量。目前,市场上有各种多功能、高精度、高频率的数字频率计,但价格不菲。为适应实际工作的需要,本文在简述频率测量的基本原理和方法的基础上,提供一种基于FPGA的数字频率计的设计和实现过程,本方案不但切实可行,而且具有成本低廉、小巧轻便、便于携带等特点。

1 数字频率测量原理和方法及本系统硬件框架

数字频率计是直接用十进制数字来显示被测信号频率的一种测量装置。它不仅可以测量正弦波、方波、三角波和尖脉冲信号的频率。而且还可以测量它们的周期。数字频率计在测量其他物理量如转速、振动频率等方面也获得广泛应用。

1.1 数字频率的测频原理和方法

众所周知,所谓“频率”就是周期性信号在单位时间(1s)内变化的次数。若在一定时间间隔T内测得这个周期性信号的重复变化次数N,则其频率可衰示为f=N/T 。

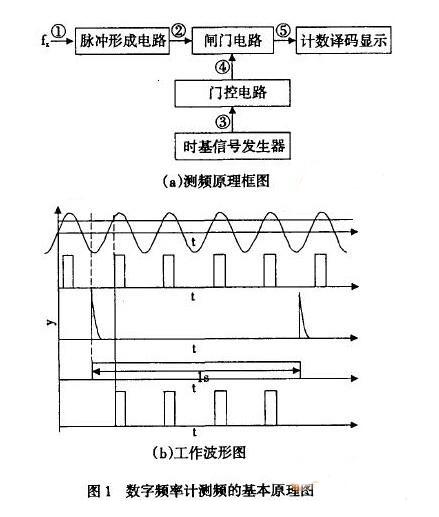

数字频率计测频率的原理框图可示如图1(a)。其中脉冲形成电路的作用是:将被测信号变成脉冲信号,其重复频率等于被测频率fx。时间基准信号发生器提供标准的时间脉冲信号、若其周期为1s。则门控电路的输出信号持续时间亦准确地等于1s。闸门电路由标准秒信号进行控制,当秒信号来到时,闸门开通。被测脉冲信号通过闸门送到计数译码显示电路。秒信号结束时闸门关闭,计数器停止计数,各点的波形如图1(b)所示。由于计数器计得的脉冲数N是在1秒时间内的累计数 所以被测频率fx=NHz。

目前,有三种常用的数字频率测量方法:直接测量法(以下称M法)、周期测量法(以下称T法)和综合测量法(以下称M/T法)。M法是在给定的闸门时间内测量被测信号的脉冲个数,进行换算得出被测信号的频率。T法是通过测量被测信号一个周期时间计时信号的脉冲个数,然后换算出被测信号的频率。这两种测量法的精度都与被测信号有关,因而它们属于非等精度测量法。而M/T法设实际闸门时间为t,被测信号周期数为Nx,则它通过测量被测信号数个周期的时间,然后换算得出被测信号的频率,克服了测量精度对被测信号的依赖性。M/T法的核心思想是通过闸门信号与被测信号同步,将闸门时间t控制为被测信号周期长度的整数倍。测量时,先打开预置闸门,当检测到被测闸门关闭时,标准信号并不立即停止计数,而是等检测到的被测信号脉冲到达是才停止,完成被测信号的整数个周期的测量。测量的实际闸门时间与预置闸门时间可能不完全相同,但最大差值不超过被测信号的一个周期。

1.2 系统的硬件框架设计

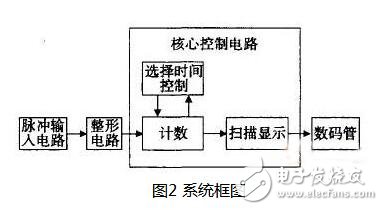

本系统由脉冲输入电路、整形电路、核心控制电路(由FPGA构成)和输出显示电路组成,如图2所示。

控制的核心芯片是FPGA,它由两大功能模块组成:(1)频率计数模块,包含两个部分,选通时间控制部分,可改变选通时间;计数部分,根据选通时间的长短对被测信号正脉冲进行计数;(2)扫描显示模块,对计数的结果进行扫描显示,从而完成整个测频率的过程。外围的电路相对简单,只有信号输入整形电路和数码管显示电路。

系统的工作原理是,被测信号经整形生成矩形波输入到控制核心芯片FPGA的计数模块,计数模块根据所提供的矩形波上升沿计数,计数时间则由选通时间控制部分决定,根据频率所处的范围来决定档位;将计数的结果给显示电路,通过扫描,在数码管上显示频率的大小。

整形电路是将待测信号整形变成计数器所要求的脉冲信号。电路形式采用由555定时器所构成的施密特触发器。若待测信号为正弦波,输入整形电路,设置分析为瞬态分析,启动电路,其输入、输出波形如图1(b)所示。由图可见输出为方波,二者频率相同,频率计测得方波的频率即为正弦波的频率。

2 基于FPGA的系统设计

2.1 EDA技术和VHDL语言的特点

EDA(电子设计自动化)代表了当今电子设计技术的最新发展方向,它的基本特征是:设计人员按照“自顶向下”(Top Down)的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC)实现,然后采用硬件描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终目标器件。FPGA可以通过软件编程对目标器件的结构和工作方式进行重构,能随时对设计进行调整,具有集成度高、结构灵活、开发周期短、快速可靠性高等特点,数字设计在其中快速发展,应用这种技术可使设计过程大大简化。VHDL语言最大的特点是描述能力极强,可以覆盖逻辑设计的诸多领域和层次,并支持众多的硬件模型。其特点包括:

(1)设计技术齐全,方法灵活,支持广泛;

(2)系统硬件描述能力强;

(3)VHDL语言可以与工艺无关地进行编程;

(4)VHDL语言标准、规范,易于共享和重用。

2.2 系统设计

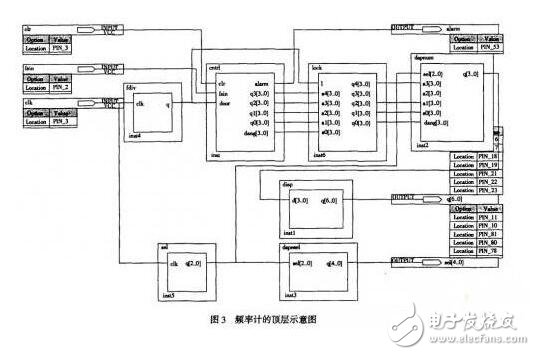

设计采用实验教学中常用的altera公司的FLEX10K10系列芯片,该芯片的反应时间可达ns级,频率计的测频范围可为1Hz~999MHz。系统在兼顾测量精度和测量反应时间的基础上,实现了量程的自动转换,测量可以全自动地进行。其控制和逻辑电路是基于quartus II和VHDL语言进行设计,外部电路相当简单。图3是本设计的顶层示意图。设计主要由分频模块、控制模块、锁存模块等共七个模块组成。脉冲信号由fsin引脚输入到cntrl模块,由clr引脚和fdiv输出信号q共同决定fsin的有效性,并由cntd实现自适应控制,当fsin的频率高出或低于某个量程,cntrl模块会根据具体的值选择相应合适的量程(本设计共有分为1~9999Hz、10~99.99kHz、100~999.9kHz、1M~999M等四个量程)。再经由lock锁存之后,由dspnum选择具体的通路,由dspsel和disp实现动态扫描显示,扫描显示模块有dspsel控制七段数码管的片选信号,间锁存保存的BCD码数据动态扫描译码,以十进制形式显示。以上的各功能模块都是在FLEX10K10中,用VHDL予以实现的,较之以往的传统型电路更为简单,更易于实现频率计的小型化、微型化甚至芯片化设计。

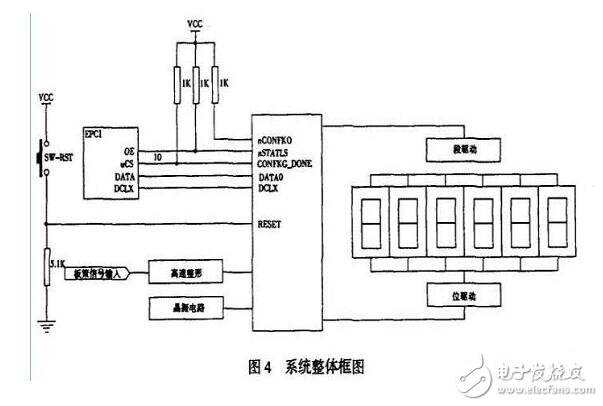

顶层示意图中的各模块用VHDL语言生成后,再生成图3所示的示意图,经编译链接之后就可以下载到系统中。再在外部扩展信号采集和相应的数码显示电路,就可以完成一个相对简单的数字频率计。图4是系统的整体框图。

信号从被测信号输入处输入到波形整形电路后,经过FPGA算法处理,再由数字显示部分输出。在数字显示部分根据不同的档位,可以把相应的单位加入即可,人一档时单位为Hz,二档时为kHz,其余类推。

此外,在硬件电路设计时,应注意FPGA的接口部分,包括电平转换、标准CPU接口等等。比如FPGA器件的I/O电压不能达到TTL电平,则需要添加必要的电平转换芯片,即通常指的Transceiver。又如,驱动LED等功能的需要是经常遇到的,但FPGA器件的驱动能力不一定能够满足需要,因此提供驱动能力也是设计时需要考虑的问题之一。同时,时钟设计是FPGA设计的核心问题之一,时钟系统的不稳定和不合理,往往不能发挥器件的全部功能和潜力,严重时还会导致系统失败。对于多时钟、多速率系统,如何做到全局同步设计、保证时延特性、达到设计速率等,对系统成功都是极为关键的。

本文在介绍了频率计的基本原理的基础上,阐述了如何基于FPGA设计和实现自适应频率计的设计,并且给出了完整的设计过程,以及针对设计中应该注意的问题加以说明。其外,如果使用更高频率的FPGA芯片,频率计的量程上限可以进一步的提高。

- 相关推荐

- 热点推荐

- FPGA设计

-

基于FPGA数字频率计的设计2017-08-04 2127

-

基于FPGA的数字频率计2017-07-26 3735

-

基于Multisim的数字频率计2016-06-21 2589

-

数字频率计设计论文2016-05-06 1010

-

简易数字频率计设计2015-12-14 1627

-

基于verilog语言的数字频率计设计2015-12-08 1472

-

数字频率计的制作2015-11-20 1279

-

求助基于FPGA的数字频率计各种资料2015-08-13 3898

-

设计简易数字频率计2011-06-28 8056

-

数字频率计2011-04-07 4207

-

简易数字频率计课程设计报告2010-08-10 2059

-

数字频率计电路图2009-04-11 5982

-

基于FPGA的数字频率计的设计与实现2009-03-17 967

-

数字频率计测频率的基本原理2008-12-01 4048

全部0条评论

快来发表一下你的评论吧 !