关于PCB高速和低速设计的区别

电子说

描述

要判断一个信号是否为高速信号首先要区分几个误区。

误区一:信号周期频率 FCLOCK 高的才属于高速设计

其实我们在设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率) Fknee 。

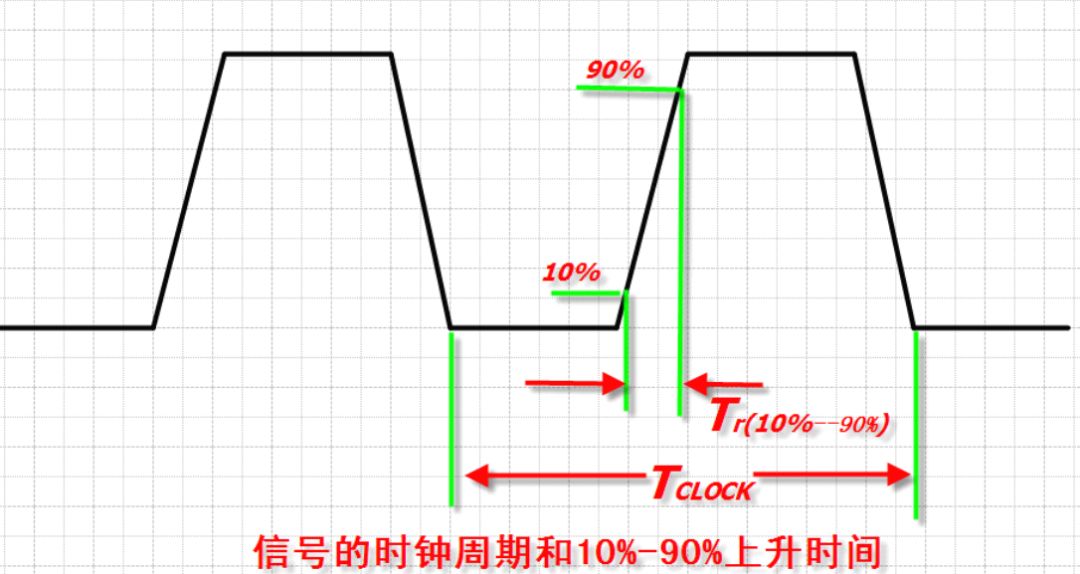

如上图信号周期频率与有效(转折)频率定义为:

FCLOCK Tclock = 1/(10% 90%) 0.5/ Fknee = Tr − (实际中多数信号而言)

误区二:电容、电感式理想器件

在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。但在高速领域,PCB 上的电容电感等已经不能简单的视为纯粹的电容电感了。例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为 F,则电容 C 两侧表现出的电抗值为1/ 2πF ×C ,,,,在工作频率很高的情况下电抗值变得很小,电容表现为短路。认清上面两个误区我们来讨论低速信号和高速信号的问题。对于低速信号而言,传输路径上的个点的电平近似相同,我们可以采用集总的思维来对待传输路径,即传输路径上的各点状态相同;对于高速信号而言,传输路径上的各点电平不同,需要采用分布式的思维来看待,即各个点的状态不同。因此,高速低速区分还要看信号传输路径的长度。

一般而言,在信号传输路径的长度(即信号线的长度)小于信号的有效波长的 1/6 1/6 1/6 1/6 时,可以认为在该传输路径上,各点的电平状态近似相同。由信号波长与频率的关系 λ = c / F ,我们可以按下面的步骤进行高速低速的区分;

1 获得信号的有效频率 Fknee 和走线长度 L;

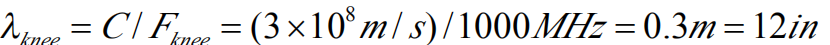

2 利用 Fknee 计算出信号的有效波长 λknee ;

3 判断 LLLL 与 1/6 1/6 1/6 1/6λknee的关系,若 LLLL>>>>1/6 1/6 1/6 1/6λknee,则信号为高速信号;反之,则为低速信号。

注意: Fknee 的获得方式一是可以直接测量,二是经验值可以假设信号的上升沿时间为信号周期的 7%,此时有效频率 Fknee 约为周期频率 FCLOCK 的 7 倍,如周期频率 FCLOCK 为100MHz 的时钟信号,可以估计其有效频率约为 700MHz。

综上,我们还可以得到传输线和非传输线的概念。和高速低速信号的判断一样,高速信号的走线我们视为传输线,反之亦反。

如果你想学习更全面的PADS技能知识,

可了解凡亿的PADS F系列精品课程。

例子:

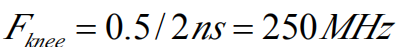

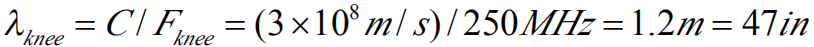

信号 1111: FCLOCK 为 100MHz,上升沿时间 2ns,走线长度 L 为 6in(英寸);

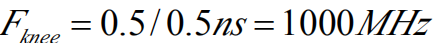

信号 2222: FCLOCK 为 100MHz,上升沿时间 0.5ns,走线长度 L 为 6in(英寸)。

对于信号 1 :

对于信号2:

其中:1mmmm=39.37 in

信号 1 的走线长为 6in,小于λknee的 1/6,因此可以视为非传输线;

信号 2 的走线长为 6in,大于λknee的 1/6,因此应视为传输线。

好啦,今天的知识就分享到这里啦,小伙伴们,如果还有其他技术问题,可以扫文章顶部二维码加入凡亿技术交流群,同行、老师实时交流解答。

凡亿教育一直秉承与学员共进步的理念,为了给大家提供更好的服务,邀请您抽出2分钟时间,将您的感受及建议告诉我们,我们非常重视每位用户的宝贵意见,期待您的参与!填写完成后,都可随机抽取1-10元现金红包,50%中奖率。

-

高速CAN总线和低速CAN总线的特性2023-04-07 3968

-

ADS1274低速模式和高速模式的区别是什么?2025-02-12 381

-

高速信号和低速信号有什么区别,怎么定义高速和低速呢2014-12-18 35166

-

如何区分电路设计中高速和低速2017-04-20 11617

-

浅谈高速PCB设计2019-05-30 1425

-

请问高速和低速的UART编码的区别是什么?2020-12-07 2222

-

stm32高速时钟与低速时钟2021-08-13 2419

-

高速低速测速器2009-01-10 1186

-

如何区分高速和低速板2016-07-26 4801

-

PCB设计中高速信号与低速信号如何区分2019-08-20 10777

-

关于高速串行信号隔直电容的PCB设计注意点2023-10-24 1660

-

如何区分高速和低速.zip2022-12-30 225

-

高速can和低速can区别2023-12-07 6076

-

高速CAN总线和低速CAN总线的区别2024-02-15 6919

-

高速pcb与普通pcb的区别是什么2024-06-10 10710

全部0条评论

快来发表一下你的评论吧 !