光刻技术的基本原理!光刻技术的种类光学光刻

电子说

描述

在集成电路的制造过程中,有一个重要的环节——光刻,正因为有了它,我们才能在微小的芯片上实现功能。

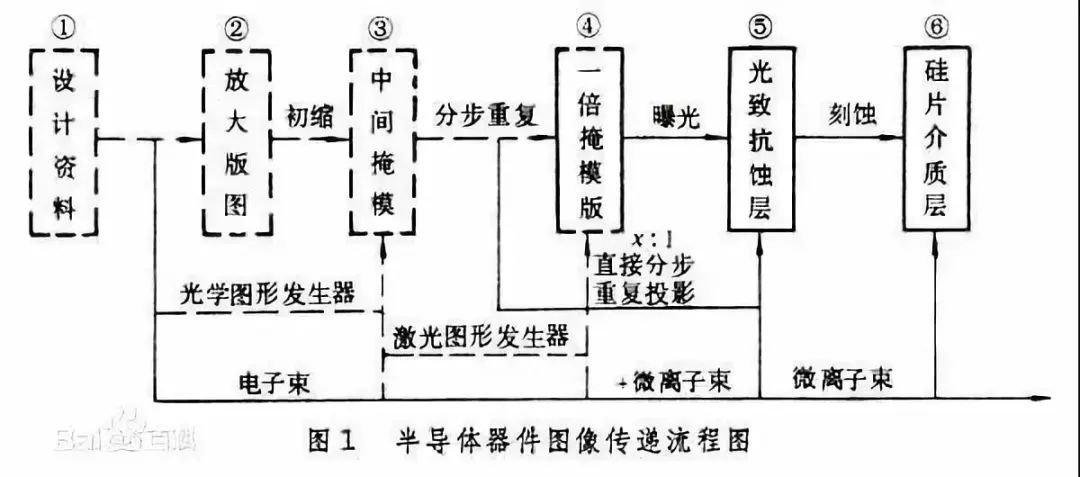

根据维基百科的定义,光刻是半导体器件制造工艺中的一个重要步骤,该步骤利用曝光和显影在光刻胶层上刻画几何图形结构,然后通过刻蚀工艺将光掩模上的图形转移到所在衬底上。这里所说的衬底不仅包含硅晶圆,还可以是其他金属层、介质层,例如玻璃、SOS中的蓝宝石。

01光刻技术的基本原理

光刻的基本原理是利用光致抗蚀剂(或称光刻胶)感光后因光化学反应而形成耐蚀性的特点,将掩模板上的图形刻制到被加工表面上。

光刻半导体芯片二氧化硅的主要步骤是:

1、涂布光致抗蚀剂;

2、套准掩模板并曝光;

3、用显影液溶解未感光的光致抗蚀剂层;

4、用腐蚀液溶解掉无光致抗蚀剂保护的二氧化硅层;

5、去除已感光的光致抗蚀剂层。

光刻技术的不断发展从三个方面为集成电路技术的进步提供了保证:

其一是大面积均匀曝光,在同一块硅片上同时做出大量器件和芯片,保证了批量化的生产水平;

其二是图形线宽不断缩小,使用权集成度不断提高,生产成本持续下降;

其三,由于线宽的缩小,器件的运行速度越来越快,使用权集成电路的性能不断提高。随着集成度的提高,光刻技术所面临的困难也越来越多。

02光刻技术的种类光学光刻

光学光刻是通过广德照射用投影方法将掩模上的大规模集成电路器件的结构图形画在涂有光刻胶的硅片上,通过光的照射,光刻胶的成分发生化学反应,从而生成电路图。限制成品所能获得的最小尺寸与光刻系统能获得的分辨率直接相关,而减小照射光源的波长是提高分辨率的最有效途径。因为这个原因,开发新型短波长光源***一直是各个国家的研究热点。目前,商业化***的光源波长已经从过去的汞灯紫外光波段进入到深紫外波段(DUV),如用于0.25微米技术的分子激光(波长为248纳米)和用于0.18微米技术的准分子激光(波长为193纳米)。

除此之外,根据光的干涉特性,利用各种波前技术优化工艺参数也是提高分辨率的重要手段。这些技术是运用电磁理论结合光刻实际对曝光成像进行深入的分析所取得的突破。其中有移相掩膜、离轴照明技术、邻近效应校正等。运用这些技术,可在目前的技术水平上获得更高分辨率的光刻图形。如1999年初Canon公司推出的FPA-1000ASI扫描步进机,该机的光源为193纳米,通过采用波前技术,可在300毫米硅片上实现0.13微米光刻线宽。

光刻技术是包含***、掩模、光刻材料等一系列技术,涉及光、机、电、物理、化学、材料等多个研究方向。目前科学家正在探索更短波长的F2激光(波长为157纳米)光刻技术。由于大量的光吸收,获得用于光刻系统的新型光学及掩模衬底材料是该波段技术的主要困难。光科技束是很多学科的综合,任何一门学科的突破就能对光刻技术的发展做出巨大贡献。

电子束光刻

电子束光刻技术是微型技术加工发展的关键技术,他在纳米制造领域中起着不可替代的作用。电子束光刻主要是刻画微小的电路图,电路通常是以纳米微单位的。

随着中国纳米技术和纳米电子学的蓬勃发展,纳米加工技术的研究越来越重要,而电子束光刻技术将是纳米结构图形加工中非常重要的手段。电子束光刻技术要应用于纳米尺度微小结构的加工和集成电路的光刻,必须解决几个关键的技术问题:电子束高精度扫描成像曝光效率低;电子在抗蚀剂和基片中的散射和背散射现象造成的邻近效应;在实现纳米尺度加工中电子抗蚀剂和电子束曝光及显影、刻蚀等工艺技术问题。

实践证明,电子束邻近效应校正技术、电子束曝光与光学曝光系统的匹配和混合光刻技术及抗蚀剂曝光工艺优化技术的应用,是一种提高电子束光刻系统实际光刻分辨能力非常有效的办法。电子束光刻最主要的就是金属化剥离,第一步是在光刻胶表面扫描到自己需要的图形。第二部是将曝光的图形进行显影,去除未曝光的部分,第三部在形成的图形上沉淀金属,第四部将光刻胶去除,在金属剥离的过程中,关键在于光刻工艺的胶型控制。最好使用厚胶,这样有利于胶剂的渗透,形成清晰的形貌。

聚焦粒子束光刻

聚焦离子束(Focused Ion beam, FIB)的系统是利用电透镜将离子束聚焦成非常小尺寸的显微切割仪器,她的原理与电子束光刻相近,不过是有电子变成离子。目前商业用途系统的离子束为液态金属离子源,金属材质为镓,因为镓元素具有熔点低、低蒸气压、及良好的抗氧化力;典型的离子束显微镜包括液相金属离子源、电透镜、扫描电极、二次粒子侦测器、5-6轴向移动的试片基座、真空系统、抗振动和磁场的装置、电子控制面板、和计算机等硬设备,外加电场于液相金属离子源 可使液态镓形成细小尖端,再加上负电场(Extractor) 牵引尖端的镓,而导出镓离子束,在一般工作电压下,尖端电流密度约为1埃10-8 Amp/cm2,以电透镜聚焦,经过一连串变化孔径 (Automatic Variable Aperture, AVA)可决定离子束的大小,再经过二次聚焦至试片表面,利用物理碰撞来达到切割之目的。

在成像方面,聚焦离子束显微镜和扫描电子显微镜的原理比较相近,其中离子束显微镜的试片表面受镓离子扫描撞击而激发出的二次电子和二次离子是影像的来源,影像的分辨率决定于离子束的大小、带电离子的加速电压、二次离子讯号的强度、试片接地的状况、与仪器抗振动和磁场的状况,目前商用机型的影像分辨率最高已达 4nm,虽然其分辨率不及扫描式电子显微镜和穿透式电子显微镜,但是对于定点结构的分析,它没有试片制备的问题,在工作时间上较为经济。

聚焦离子束投影曝光除了前面已经提到的曝光灵敏度极高和没有邻近效应之外还包括焦深大于曝光深度可以控制。离子源发射的离子束具有非常好的平行性,离子束投影透镜的数值孔径只有0.001,其焦深可达100μm,也就是说,硅片表面任何起伏在100μm之内,离子束的分辨力基本不变。而光学曝光的焦深只有1~2μm为。她的主要作用就是在电路上进行修补 ,和生产线制成异常分析或者进行光阻切割。

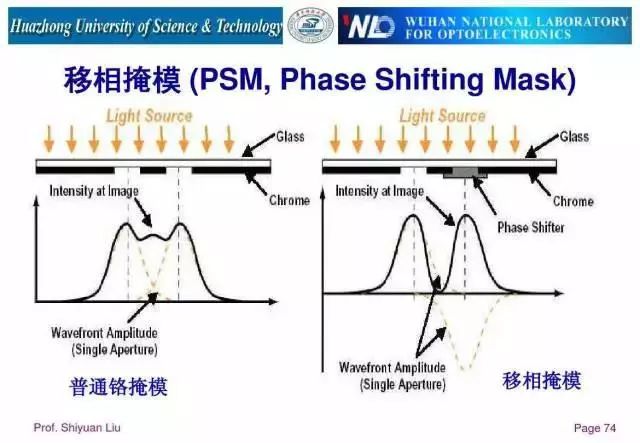

移相掩模

光刻分辨率取决于照明系统的部分相干性、掩模图形空间频率和衬比及成象系统的数值孔径等。相移掩模技术的应用有可能用传统的光刻技术和i线***在最佳照明下刻划出尺寸为传统方法之半的图形,而且具有更大的焦深和曝光量范围。例如使用PSM,在NA=0.5,λ=248nm,分辨率可达0.15um;NA=0.6,λ=365nm,实际分辨率可达0.2um。相移掩模方法有可能克服线/间隔图形传统光刻方法的局限性。

随着移相掩模技术的发展,涌现出众多的种类, 大体上可分为交替式移相掩膜技术、衰减式移相掩模技术;边缘增强型相移掩模, 包括亚分辨率相移掩模和自对准相移掩模;无铬全透明移相掩模及复合移相方式( 交替移相+ 全透明移相+ 衰减移相+ 二元铬掩模) 几类。尤其以交替型和全透明移相掩模对分辨率改善最显著, 为实现亚波长光刻创造了有利条件。全透明移相掩模的特点是利用大于某宽度的透明移相器图形边缘光相位突然发生180度变化, 在移相器边缘两侧衍射场的干涉效应产生一个形如“刀刃”光强分布, 并在移相器所有边界线上形成光强为零的暗区, 具有微细线条一分为二的分裂效果, 使成像分辨率提高近1 倍。

光学曝光技术的潜力, 无论从理论还是实践上看都令人惊叹, 不能不刮目相看。其中利用控制光学曝光过程中的光位相参数, 产生光的干涉效应,部分抵消了限制光学系统分辨率的衍射效应的波前面工程为代表的分辨率增强技术起到重要作用, 包括: 移相掩模技术、光学邻近效应校正技术、离轴照明技术、光瞳空间滤波技术、驻波效应校正技术、离焦迭加增强曝光技术、表面成像技术及多级胶结构工艺技术。在实用化方面取得最引人注目进展的要数移相掩模技术、光学邻近效应校正技术和离轴照明技术, 尤其浸没透镜曝光技术上的突破和两次曝光技术的应用, 为分辨率增强技术的应用更创造了有利条件。

X射线光刻

软X射线投影光刻作为特征线宽小于0.1μm的集成电路制造技术,倍受日美两个集成电路制造设备生产大国重视。随着用于软X射线投影光刻的无污染激光等离子体光源、高分辨率大视场投影光学系统、无应力光学装调工艺、深亚纳米级镜面加工和多层膜制备、低缺陷反射式掩膜、表面成像光刻胶、精密扫描机构等关键技术均取得了突破。

03光刻技术的详细工序

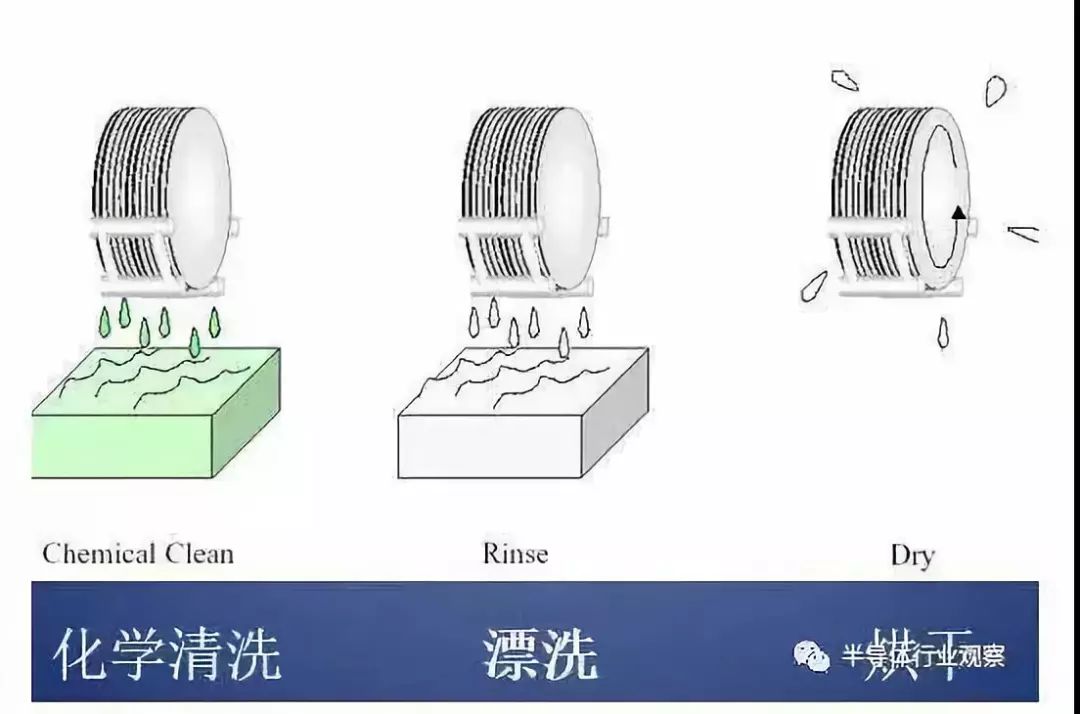

一、清洗硅片(Wafer Clean)

清洗硅片的目的是去除污染物去除颗粒、减少针孔和其它缺陷,提高光刻胶黏附性

基本步骤:化学清洗——漂洗——烘干。

硅片经过不同工序加工后,其表面已受到严重沾污,一般讲硅片表面沾污大致可分在三类:

1、有机杂质沾污: 可通过有机试剂的溶解作用,结合超声波清洗技术来

去除。

2、颗粒沾污:运用物理的方法可采机械擦洗或超声波清洗技术来去除粒径 ≥ 0.4 μm颗粒,利用兆声波可去除 ≥ 0.2 μm颗粒。

3、金属离子沾污:必须采用化学的方法才能清洗其沾污,硅片表面金属杂质沾污有两大类:

a. 一类是沾污离子或原子通过吸附分散附着在硅片表面。

b. 另一类是带正电的金属离子得到电子后面附着(尤如“电镀”)到硅片表面。

硅抛光片的化学清洗目的就在于要去除这种沾污。

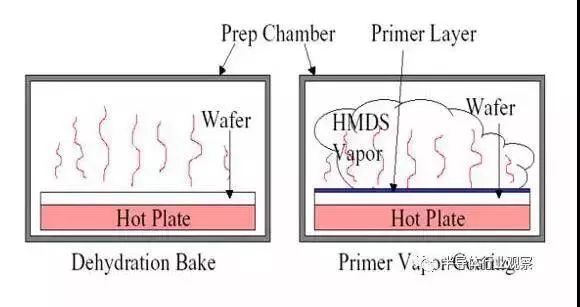

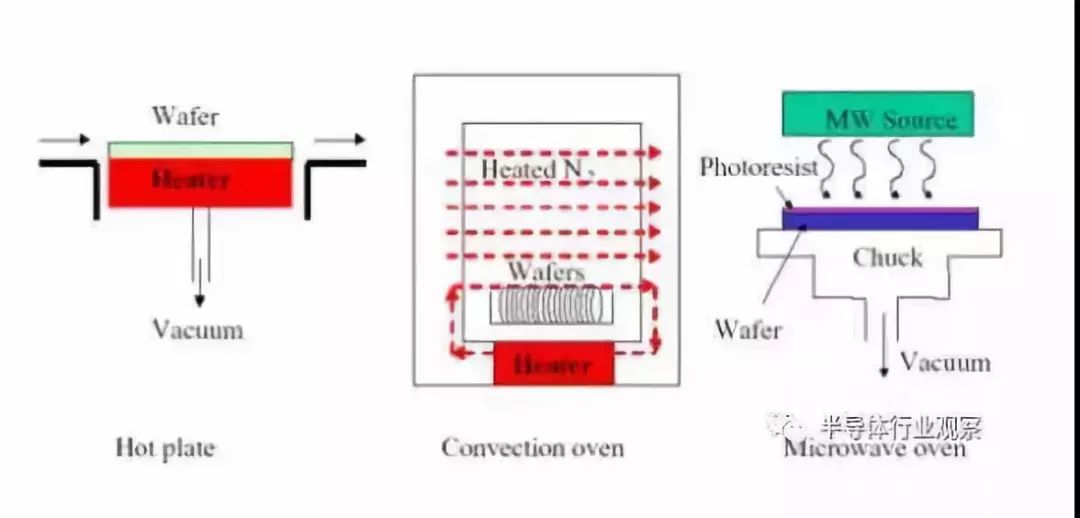

二、预烘和底胶涂覆(Pre-bake and Primer Vapor)

由于光刻胶中含有溶剂,所以对于涂好光刻胶的硅片需要在80度左右的。硅片脱水烘焙能去除圆片表面的潮气、增强光刻胶与表面的黏附性、通常大约100 °C。这是与底胶涂覆合并进行的。

底胶涂覆增强光刻胶(PR)和圆片表面的黏附性。广泛使用: (HMDS)六甲基二硅胺、在PR旋转涂覆前HMDS蒸气涂覆、PR涂覆前用冷却板冷却圆片。

三、光刻胶涂覆(Photoresist Coating)

光刻胶涂覆通常的步骤是在涂光刻胶之前,先在900-1100度湿氧化。氧化层可以作为湿法刻蚀或B注入的膜版。作为光刻工艺自身的第一步,一薄层的对紫外光敏感的有机高分子化合物,即通常所说的光刻胶,要涂在样品表面(SiO2)。首先光刻胶被从容器中取出滴布到置于涂胶机中的样品表面,(由真空负压将样品固定在样品台上),样品然后高速旋转,转速由胶粘度和希望胶厚度确定。在这样的高速下,胶在离心力的作用下向边缘流动。

涂胶工序是图形转换工艺中最初的也是重要的步骤。涂胶的质量直接影响到所加工器件的缺陷密度。为了保证线宽的重复性和接下去的显影时间,同一个样品的胶厚均匀性和不同样品间的胶厚一致性不应超过±5nm(对于1.5um胶厚为±0.3%)。

光刻胶的目标厚度的确定主要考虑胶自身的化学特性以及所要复制图形中线条的及间隙的微细程度。太厚胶会导致边缘覆盖或连通、小丘或田亘状胶貌、使成品率下降。在MEMS中、胶厚(烤后)在0.5-2um之间,而对于特殊微结构制造,胶厚度有时希望1cm量级。在后者,旋转涂胶将被铸胶或等离子体胶聚合等方法取代。常规光刻胶涂布工序的优化需要考虑滴胶速度、滴胶量、转速、环境温度和湿度等,这些因素的稳定性很重要。

四、前烘(Soft Bake)

完成光刻胶的涂抹之后,需要进行软烘干操作,这一步骤也被称为前烘。前烘能够蒸发光刻胶中的溶剂溶剂、能使涂覆的光刻胶更薄。

在液态的光刻胶中,溶剂成分占65%-85%。虽然在甩胶之后,液态的光刻胶已经成为固态的薄膜,但仍有10%-30%的溶剂,容易沾污灰尘。通过在较高温度下进行烘培,可以使溶剂从光刻胶中挥发出来(前烘后溶剂含量降至5%左右),从而降低了灰尘的沾污。同时,这一步骤还可以减轻因高速旋转形成的薄膜应力,从而提高光刻胶 衬底上的附着性。

在前烘过程中,由于溶剂挥发,光刻胶厚度也会减薄,一般减薄的幅度为10%-20%左右。

五、对准(Alignment)

光刻对准技术是曝光前一个重要步骤作为光刻的三大核心技术之一,一般要求对准精度为最细线宽尺寸的 1/7---1/10。随着光刻分辨力的提高 ,对准精度要求也越来越高 ,例如针对45am线宽尺寸 ,对准精度要求在5am 左右。

受光刻分辨力提高的推动 ,对准技术也经历 迅速而多样的发展 。从对准原理上及标记结 构分类 ,对准技术从早期的投影光刻中的几何成像对准方式 ,包括视频图像对准、双目显微镜对准等,一直到后来的波带片对准方式 、干涉强度对准 、激光外差干涉以及莫尔条纹对准方式 。从对准信号上分 ,主要包括标记的显微图像对准 、基于光强信息的对准和基于相位信息对准。

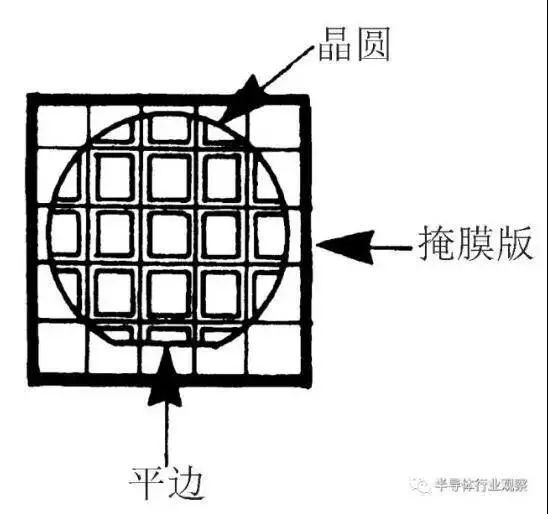

对准法则是第一次光刻只是把掩膜版上的Y轴与晶园上的平边成90,如图所示。接下来的掩膜版都用对准标记与上一层带有图形的掩膜对准。对准标记是一个特殊的图形(见图),分布在每个芯片图形的边缘。经过光刻工艺对准标记就永远留在芯片表面,同时作为下一次对准使用。

对准方法包括:

a、预对准,通过硅片上的notch或者flat进行激光自动对准

b、通过对准标志,位于切割槽上。另外层间对准,即套刻精度,保证图形与硅片上已经存在的图形之间的对准。

六、曝光(Exposure)

在这一步中,将使用特定波长的光对覆盖衬底的光刻胶进行选择性地照射。光刻胶中的感光剂会发生光化学反应,从而使正光刻胶被照射区域(感光区域)、负光刻胶未被照射的区域(非感光区)化学成分发生变化。这些化学成分发生变化的区域,在下一步的能够溶解于特定的显影液中。

在接受光照后,正性光刻胶中的感光剂DQ会发生光化学反应,变为乙烯酮,并进一步水解为茚并羧酸(Indene-Carboxylic-Acid, CA),羧酸在碱性溶剂中的溶解度比未感光部分的光刻胶高出约100倍,产生的羧酸同时还会促进酚醛树脂的溶解。利用感光与未感光光刻胶对碱性溶剂的不同溶解度,就可以进行掩膜图形的转移。

曝光方法:

a、接触式曝光(Contact Printing)掩膜板直接与光刻胶层接触。

b、接近式曝光(Proximity Printing)掩膜板与光刻胶层的略微分开,大约为10~50μm。

c、投影式曝光(Projection Printing)。在掩膜板与光刻胶之间使用透镜聚集光实现曝光。

d、步进式曝光(Stepper)

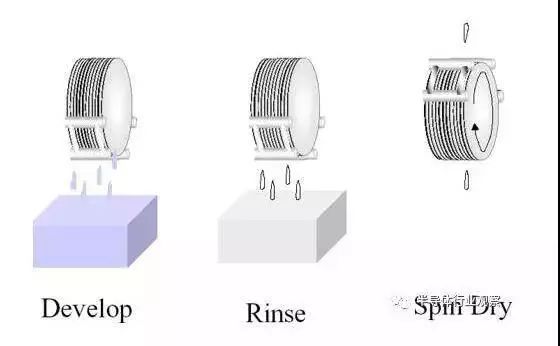

七、显影(development)

通过在曝光过程结束后加入显影液,正光刻胶的感光区、负光刻胶的非感光区,会溶解于显影液中。这一步完成后,光刻胶层中的图形就可以显现出来。为了提高分辨率,几乎每一种光刻胶都有专门的显影液,以保证高质量的显影效果。

显影工序使将在曝光过程中形成的隐性图形成为光刻胶在与不在的显性图形,以作为下一步加工的膜版。显影中进行的是选择性溶解的过程,最重要的是曝光区和未曝光区之间溶解率的比值(DR)。商用正胶有大于1000的DR比,在曝光区溶解速率为3000nm/min,在未曝光区只有几nm/min。

现在有二种显影方法,一是湿显影,他IC和微加工中正广泛使用,另一种是干显影。

八、坚膜 (Hard Bake)

刻胶显影完成后,图形就基本确定,不过还需要使光刻胶的性质更为稳定。硬烘干可以达到这个目的,这一步骤也被称为坚膜。在这过程中,利用高温处理,可以除去光刻胶中剩余的溶剂、增强光刻胶对硅片表面的附着力,同时提高光刻胶在随后刻蚀和离子注入过程中的抗蚀性能力。另外,高温下光刻胶将软化,形成类似玻璃体在高温下的熔融状态。这会使光刻胶表面在表面张力作用下圆滑化,并使光刻胶层中的缺陷(如针孔)减少,这样修正光刻胶图形的边缘轮廓。

用O2等离子体对样品整体处理,以清除显影后可能的非望残留叫de-scumming。特别是负胶但也包括正胶,在显影后会在原来胶-基板界面处残留聚合物薄层,这个问题在结构小于1um或大深-宽比的结构中更为严重。当然在De-scumming过程中留胶厚度也会降低,但是影响不会太大。

最后,在刻蚀或镀膜之前需要硬烤以去除残留的显影液和水,并退火以改善由于显影过程渗透和膨胀导致的界面接合状况。同时提高胶的硬度和提高抗刻蚀性。硬烤温度一般高达120度以上,时间也在20分左右。主要的限制是温度过高会使图形边缘变差以及刻蚀后难以去除。

九、刻蚀或离子注入

刻蚀是半导体器件制造中利用化学途径选择性地移除沉积层特定部分的工艺。刻蚀对于器件的电学性能十分重要。如果刻蚀过程中出现失误,将造成难以恢复的硅片报废,因此必须进行严格的工艺流程控制。半导体器件的每一层都会经历多个刻蚀步骤。

刻蚀一般分为电子束刻蚀和光刻,光刻对材料的平整度要求很高,因此,需要很高的清洁度。 但是,对于电子束刻蚀,由于电子的波长极短,因此分辨率与光刻相比要好的多。 因为不需要掩模板,因此对平整度的要求不高,但是电子束刻蚀很慢,而且设备昂贵。

对于大多数刻蚀步骤,晶圆上层的部分位置都会通过“罩”予以保护,这种罩不能被刻蚀,这样就能对层上的特定部分进行选择性地移除。在有的情况中,罩的材料为光阻性的,这和光刻中利用的原理类似。而在其他情况中,刻蚀罩需要耐受某些化学物质,氮化硅就可以用来制造这样的“罩”。

离子注入是一种将特定离子在电场里加速,然后嵌入到另一固体材料之中的技术手段。使用这个技术可以改变固体材料的物理化学性质,现在已经广泛应用于半导体器件制造和某些材料科学研究。离子注入可以导致核转变,或改变某些固体材料的晶体结构。

十、光刻胶的去除

光刻胶的主要功能是在整个区域进行化学或机械处理工艺时,保护光刻胶下的衬底部分。所以当以上工艺结束之后,光刻胶应全部去除,这一步骤简称去胶。只有那些高温稳定的光刻胶,例如光敏感聚酰亚胺,可以作为中间介质或缓冲涂层而留在器件上。

为避免对被处理表面的任何损伤,应当使用低温下温和的化学方法。超声波的应用也可以增强剥离效能。因为有腐蚀问题、一些已知的剥离液不能作用与铝等金属表面;在此情况下、臭氧或氧等离子体(灰化)是首先采用的。这些等离子体同样成功地作为非铝表面的光刻交剥离剂,但是,器件表面的损坏仍是要解决的问题。

刻蚀或离子注入之后,已经不再需要光刻胶作保护层,可以将其除去。

去胶的方法分类如下:

湿法去胶:a、有机溶剂去胶:利用有机溶剂除去光刻胶;b、无机溶剂:通过使用一些无机溶剂,将光刻胶这种有机物中的碳元素氧化为二氧化碳,进而而将其除去。

干法去胶:利用等离子体将光刻胶剥除。

除了这些主要的工艺以外,还经常采用一些辅助过程,比如进行大面积的均匀腐蚀来减小衬底的厚度,或者去除边缘不均匀的过程等等。一般在生产半导体芯片或者其它元件时,一个衬底需要多次重复光刻。

以上就是光刻技术一些基本的介绍,小伙伴心中的光刻知识体系有木有更清晰了?

-

光学光刻技术有哪些分类 光刻技术的原理2023-10-24 1803

-

什么是光刻工艺?光刻的基本原理2023-08-23 5485

-

计算光刻技术的发展2022-10-26 4079

-

光刻工艺中使用的曝光技术2022-07-27 4806

-

国科大《集成电路先进光刻技术与版图设计优化》课程分享之二:浸没式光刻工艺缺陷种类、特征及自识别方法2021-10-14 7862

-

半导体光刻技术基本原理2021-07-26 2748

-

光刻工艺步骤2021-01-12 4358

-

芯片光刻技术的基本原理及主要步骤2020-11-11 25812

-

光刻机工艺的原理及设备2020-07-07 17322

-

光刻胶在集成电路制造中的应用2018-08-23 7262

-

光刻胶2018-07-12 2876

-

光刻技术概述及光刻技术的原理2018-04-17 35700

-

光刻及资料分享—Optical Lithography2014-09-26 21932

-

光刻技术原理及应用2012-01-12 10629

全部0条评论

快来发表一下你的评论吧 !