IC设计常见的异步电路处理故障

EDA/IC设计

描述

0.引言

大四保研到实验室正好碰到师兄师姐们找工作,听到的一些面试常问的内容就是“跨时钟域”、”异步处理“、”异步FIFO“等。然而我看的一些经典的书籍都是这样说的”异步电路很难设计,最好全部使用同步技术进行设计,所有寄存器器使用一个全局时钟驱动“。可在实际项目中,我又发现现代芯片设计中很难只使用一个时钟,时钟分频逻辑、时钟选择多路器,除了多时钟,有时还必须在两个不同的时钟间传递数据。也就是异步电路处理问题(两个没有特定关系的时钟传递数据被认为是异步的)。”异步电路很复杂“会有很多设计的不确定性。

1.亚稳态

时序逻辑中大量使用D触发器,D触发器的一般结构是:两个串联的反相器加两个传输门构成锁存器,两个锁存器串联构成D触发器。D触发器是一种双稳态电路,两个稳定状态”1“、”0“。两个反向器构成的反馈回路可能会产生亚稳态。

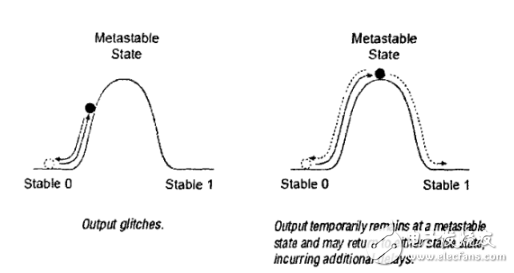

图 1-1 两个反向器反馈回路输出特性

如图1-1所示,当电压处于两个曲线的交叉点时,在没有任意外部干扰的情况下,电路将保持此状态不变,也就是进入了亚稳态。实际电路不可能完全没有外部干扰,在外部干扰下,电路可能会重新趋于一个稳定状态。(ps:从特性曲线看,如果上升和下降斜率越大,电路能越快从亚稳态电路中恢复过来。)

图 1-2 双稳态图示

建立时间保持时间

建立时间:为了保证触发器可靠的接受输入数据,数据需要在时钟上升沿到来之前保持稳定的最小时间。

保持时间:时钟有效沿后,数据还需要保持的最小时间。

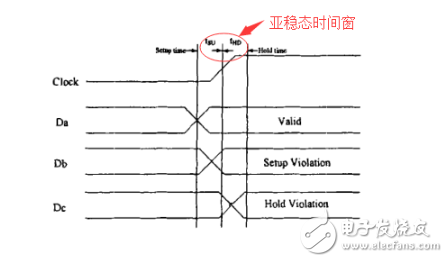

图 1-3 建立保持时间与亚稳时间窗

建立时间保持时间方程

Tco+Tcomp+Tsu<=T+Tskew;

Tco+Tcomp>=Thd+Tskew;

亚稳态

如果不能满足最小建立时间或最小保持时间,DFF输出将是不定状态,或在高低电平之间震荡,几进入亚稳态。

亚稳态:指触发器无法在某个规定的时间段内达到一个可确认的状态。但触发器进入亚稳态时,既无法预测改单元输出电平,也无法预测何时才能稳定在某个正确电平上。

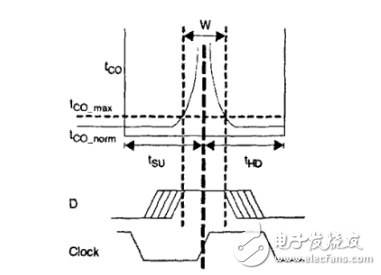

图 1-4 亚稳态时间窗

如图所示,当在输入数据在亚稳时间窗变化时,Tco增大,在Tco_max之后还没有稳定的情况就是亚稳态。

2.异步数据传输

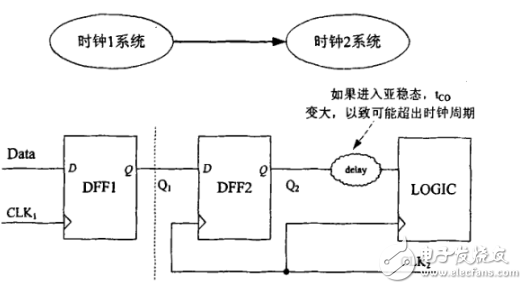

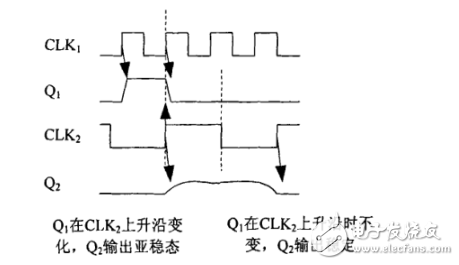

异步数据传输可能导致亚稳态,如图2-1所示

图 2-1 异步数据传输

两个时钟CLK1和CLK2没有相关性,无法保证DFF1的输出在DFF2上能满足建立保持时间。CLK1的数据传输到CLK2上可能发生以下情况:

1)满足建立保持时间,数据正确接收

2)实际的建立时间小于临界时间点,数据无法接收

3)数据实际建立时间不满足建立时间,但大于临界时间点,数据Tco增大。

4)数据越接近临界时间点变化,延时时间越大,相差很小时,输出无法预测,噪声可使结果出现随机性。

图 2-2 异步传输亚稳态时序

在CLK1和CLK2没有任何关系的情况下,Q1可能在CLK2上升沿的任何时候跳变,DFF2输出必定有一定的概率进入亚稳态,一旦DFF2进入亚稳态,Tco增大,当Tco增大到大于T+Tskew-Tcomb-Tsu时,DFF2到DFF3会产生建立时间违例,从而产生亚稳态传播。

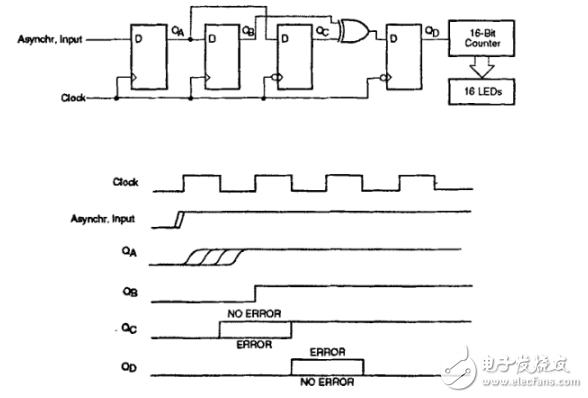

图 2-3 亚稳态测量电路

通过改变时钟周期,可测得一系列不同Tco的MTBF值。

3.异步处理电路

针对不同的异步数据可以采用不同的同步处理方式。

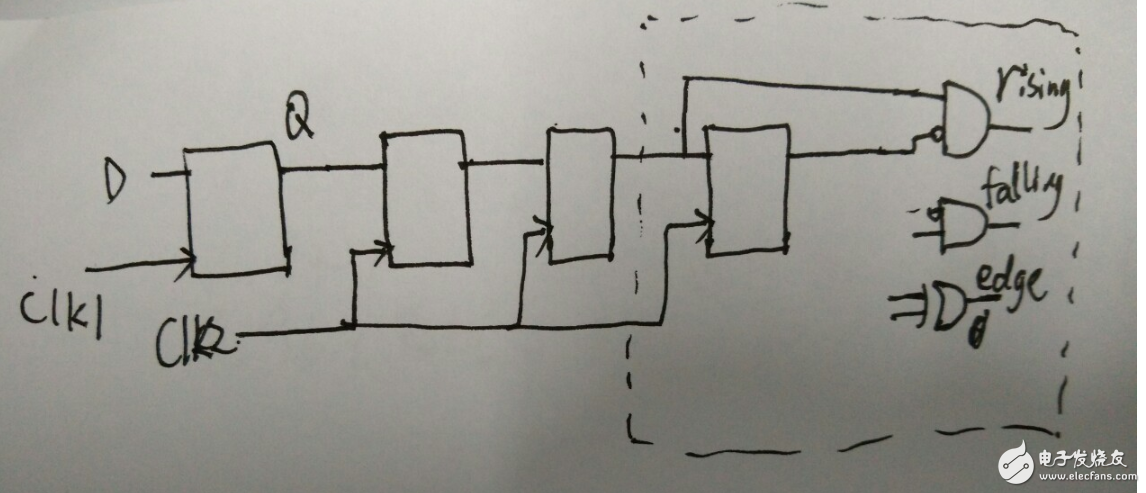

1)电平信号:多级串联的DFF(2级以上)。

2)脉冲信号:

①在慢时钟到快时钟域传递,且连个时钟相差比较大时,慢时钟的脉冲可以被快时钟当做电平,使用电平同步技术同步后,在采用边沿检测电路即可得到相应的脉冲信号。

②快时钟到慢时钟,使用脉冲同步器,下图给出了两个电路,不归0翻转电路,反馈清0电路

3)多bit数据:使用握手协议或者异步FIFO。在握手协议中,异步的REQ/ACK需要使用上述同步技术进行同步处理,异步FIFO也是如此。关于FIFO涉及的内容比较多,后续专门讲解。

-

电子电路常见故障类型及处理方法系统解析2016-09-22 12383

-

你知道三相异步电动机的常见故障有哪些吗2021-09-24 2870

-

常见主电路及控制电路故障处理方法2021-11-16 2192

-

静止进相器的常见故障及处理方法还有哪些?2022-05-19 3623

-

PLC常见故障处理2009-07-05 834

-

常见CPU故障处理方法2010-01-12 1103

-

通用示波器的常见故障处理2016-05-05 679

-

碳刷选用及常见故障的处理2017-01-02 1242

-

三相交流异步电动机几种常见故障原因分析及故障处理方法2017-09-11 1640

-

相异步电动机常见故障原因及解决方法2022-02-15 4677

-

污水处理厂三相异步电动机常见故障维修和保护2023-01-09 1622

-

AMT变速箱常见的故障及故障的处理方式2023-04-06 5953

-

异步电动机的常见故障及处理方法2024-06-03 2728

-

如何处理时钟电路的常见故障2024-09-09 4477

-

buck电路常见故障及处理2024-11-04 3688

全部0条评论

快来发表一下你的评论吧 !