ic设计——CDC的基本概念

EDA/IC设计

1078人已加入

描述

随着技术的发展,数字电路的集成度越来越高,设计也越来越复杂。很少有系统会只工作在同一个时钟频率。一个系统中往往会存在多个时钟,这些时钟之间有可能是同步的,也有可能是异步的。如果一个系统中,异步时钟之间存在信号通道,则就会存在CDC(clock domain crossing)问题。在下面的文章里,我们将会讨论CDC的一些技术细节。

一, CDC的基本概念

我们首先来看CDC的一些基本的概念:

1. 时钟域(Clock domain)

如果某一设计只有一个或者几个有固定相位关系的时钟驱动,我们称这个设计属于一个时钟域。比如,一个时钟和它的反相时钟以分频时钟一般有固定的相位关系,属于同一个时钟域。而如果两个或者多个时钟之间没有固定的相位关系,则它们属于不同的时钟域。

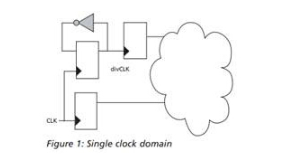

如下图中,divCLK是由CLK分频得到的,divCLK和CLK被认为是同步时钟,而由divCLk和CLK驱动的设计被认为是属于同一个时钟域。

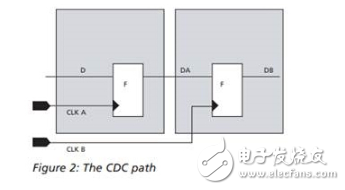

如下图中,CLKA和CLKB之间没有固定的相位关系,是异步时钟。前半部分设计属于时钟域CLKA,后半部分设计属于时钟域CLKB。DA信号从时钟域CLKA进入到时钟域CLKB,是一个跨时钟域的信号,这条path也会被称为CDC path。

如今的数字电路设计中,跨时钟域的情况及其普遍。举一个最简单的例子,一个USB转串口的模块,串口因为波特率的不同,会工作在不同的时钟频率下,USB接口也会因为工作在不同的速度而有不同的工作频率。USB接口的时钟和串口的时钟之间不存在任何相位上的关系,也就是说,USB接口模块和串口模块属于不同的时钟域,他们之间相连的path就是跨时钟域的path。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

微带的基本概念2009-11-02 3644

-

Proteus涉及的基本概念2012-08-01 3042

-

电子元件基本概念和原理2012-08-05 3058

-

Fpga Cpld的基本概念2012-08-20 2978

-

集成电路(IC)常用基本概念2013-01-11 4701

-

C语言基本概念2015-08-01 4226

-

数据结构的基本概念是什么2020-05-27 1087

-

阻抗控制相关的基本概念2021-02-25 2278

-

智能天线的基本概念2021-08-05 2150

-

CODESYS的基本概念有哪些2021-09-18 1884

-

微波基本概念2022-06-23 29873

-

照明常识基本概念2010-07-24 1902

-

通信原理的基本概念讲解2021-05-27 1356

-

verilog的一些基本概念2022-07-07 2407

-

基本概念.zip2022-12-30 592

全部0条评论

快来发表一下你的评论吧 !