串行外设接口SPI通信协议的应用

接口/总线/驱动

描述

简介

SPI(全称SerialPeripheral Interface),串行外设接口。

SPI是串行外设接口(SerialPeripheral Interface)的缩写。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,如今越来越多的芯片集成了这种通信协议,比如AT91RM9200。

--from 百度百科

该接口由摩托罗拉在20世纪80年代中期开发,并已成为事实标准。

--from Wiki

从维基百科查阅的的“事实标准”,在这来科普一下知识盲点:

事实标准是指非由标准化组织制定的,而是由处于技术领先地位的企业、企业集团制定(有的还需行业联盟组织认可,如DVD标准需经DVD论坛认可),由市场实际接纳的技术标准。

--from 百度百科

SPI接口定义了一主多从这样的一个通信架构,在同一SPI总线上只有一个主机,可以有多个从机。这样的架构就限制了通信的主动权只能在主机端,主机发起一次通信,从机做出想要。

信号线

SPI被称为四线串行总线,其信号线分别有:

SCLK:串行时钟(主机输出)

MOSI:主输出从机输入或主机输出从机输入(主机输出的数据)

MISO:主输入从输出或主输入从输出(从输出的数据输出)

SS:从机选择(通常为低电平有效,主机输出)

信号线命名也是五花八门,以下的命名也是会遇见的:

串口时钟:

SCLK:SCK

主输出--->从输入(MOSI):

SIMO,MTSR - 对应主设备和从设备上的MOSI,相互连接

SDI,DI,DIN,SI - 在从设备上; 连接到主设备上的MOSI,或连接到下面的连接

SDO,DO,DOUT,SO - 在主设备上; 连接到从站上的MOSI,或连接到上面的连接

主输入<---从输出(MISO):

SOMI,MRST - 对应主设备和从设备上的MISO,相互连接

SDO,DO,DOUT,SO - 在从设备上; 连接到主设备上的MISO,或连接到下面的连接

SDI,DI,DIN,SI - 主设备; 连接到奴隶上的MISO或上面的连接

从机选择:

SS:SSEL,CS,CE,nSS,/ SS,SS#

以上容易让人混淆的名字是SDO、SDI、DOUT、DIN等,这些都需要看具体印在主设备还是从设备上单独讨论。但是一般的还是尽量写清写规范,这样不容易产生歧义。

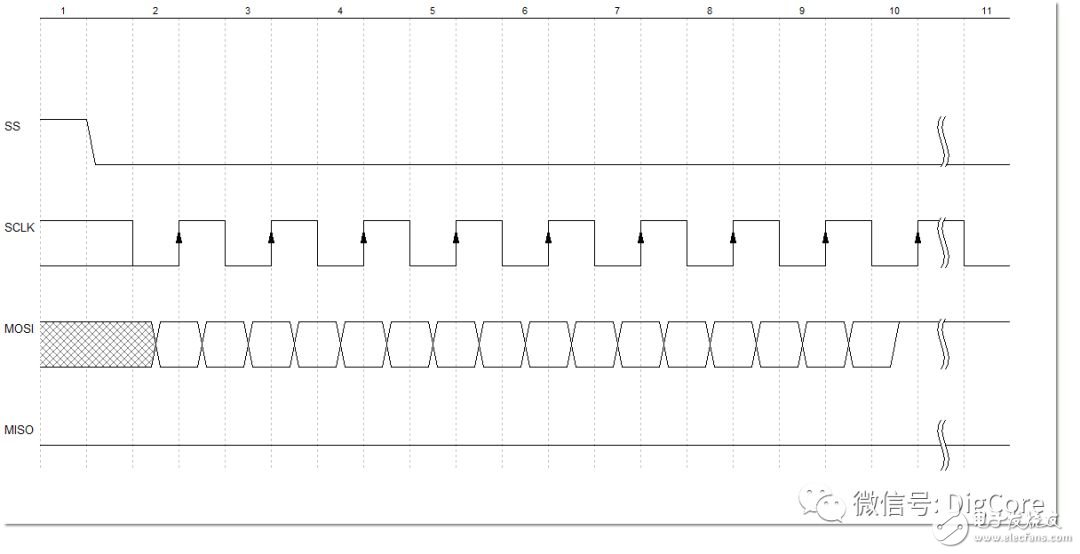

SPI作为同步串行接口,可以认为有两个同步信号,第一个是从机选择SS信号,告知被选中的从机,准备开始进行SPI通信,第二个是同步时钟信号SCLK,收发双方进行数据的交互时,都是基于SCLK的跳变进行逐bit输出和采样的。

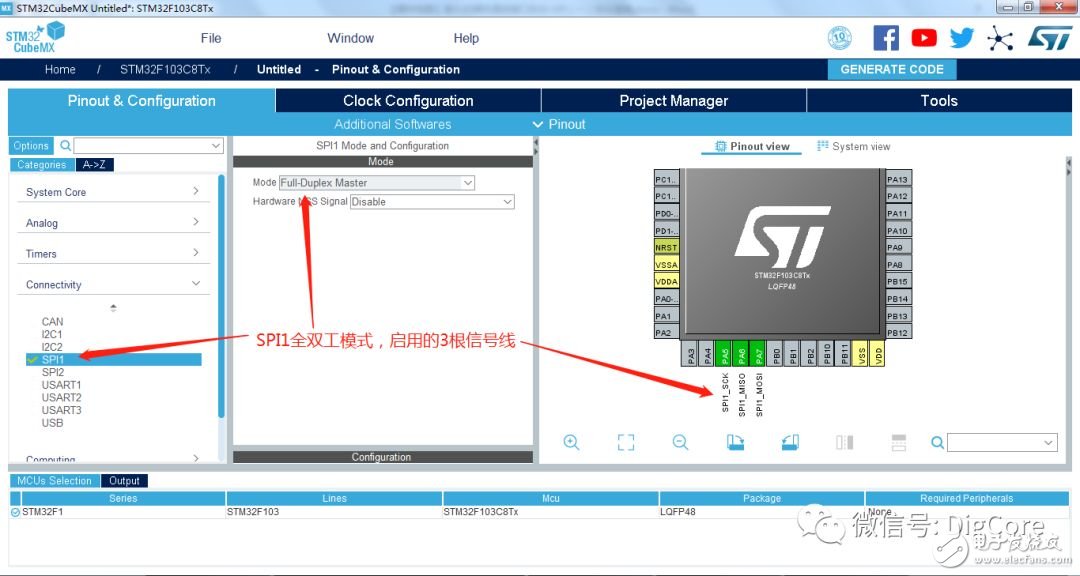

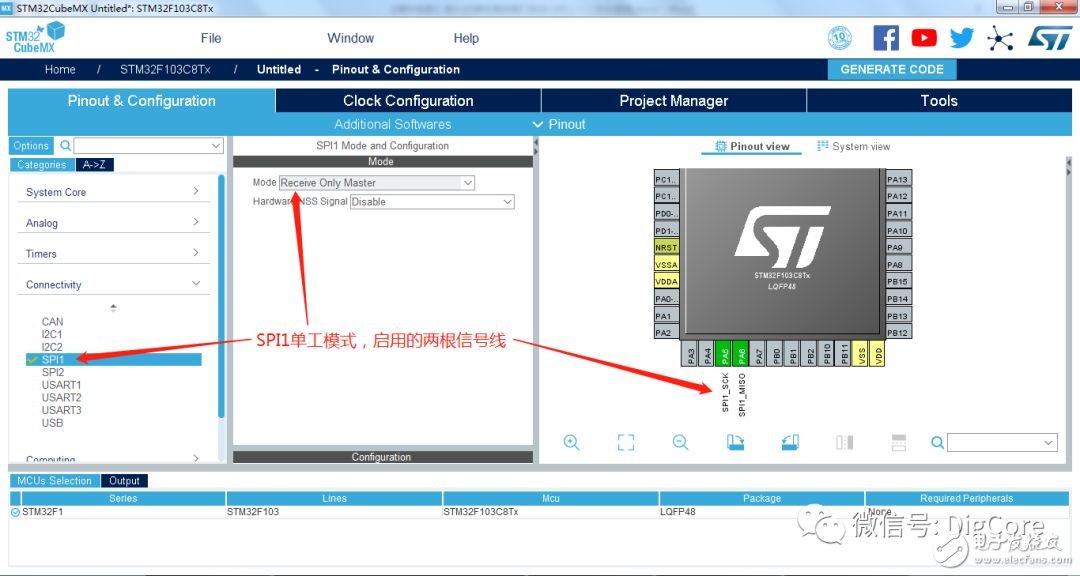

四根信号线并非全部都需要,根据工作模式,可以配置成两线、三线。

在STM32CubeMX工具的配置页面,可以很清楚看到,配置不同的工作模式时,对应被使能的芯片管脚有何不同:

对比发现,全双工的四线和三线的区别是从机选择信号NSS。这种情况一般是因为SPI总线上只有一主一从的通信架构,从机的NSS信号一直接低电平,不需要做从机选择。

信号时序

四线SPI接口的时序一般的总是先拉低从机选择信号线SS,然后输出SCLK,带着数据MOSI,此时MISO为高阻态。大致如下如:

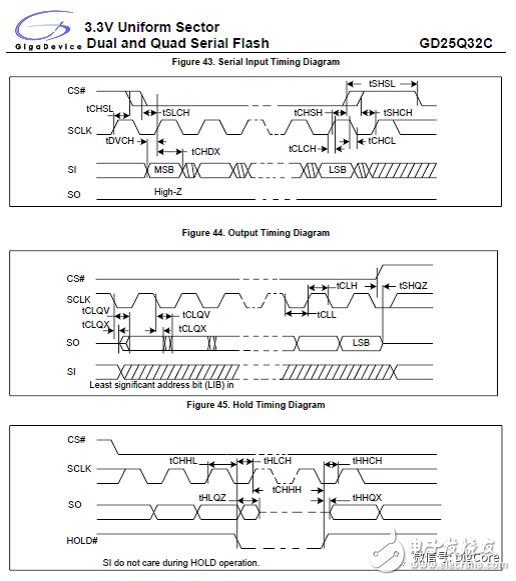

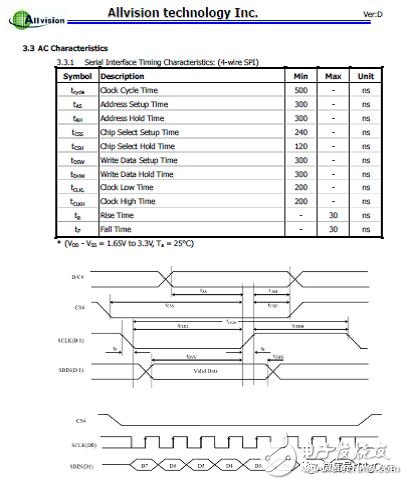

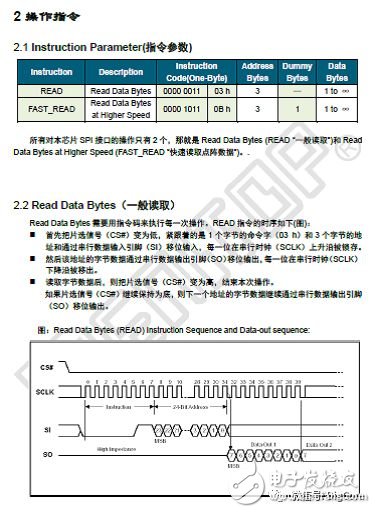

一般有SPI接口的器件,在Spec上都会有对应的时序图,这里分别截取SPI接口FLASH型号为GD25Q32C、SPI接口OLED型号为QG-2832TLBFG04,这两器件的Spec内关于SPI时序部分的介绍,如下两张截图:

对比不难发现,时序图的规范,定义了各个信号线输出电平的顺序和时延,还定义了时钟信号跳变沿与数据信号的“对齐”,这里的“对齐”实际上就是数据的输出和采样。

同样的,这个时序规范了SPI器件所呈现的SPI接口信号线特性,包括:时钟上升、下降沿时长;片选与时钟跳变沿之间的时延;时钟边缘与数据线保持的时长…

这些时序特性,都在明确了SPI主机与其通信时,要求不超出其定义的范围,否则从机器件响应不及时而导致通信异常。

不同的器件,对SPI接口的信号时序要求也会不同。第一张简明的时序图,而基于这样的时序图,SPI接口又可以配置不同的接口配置参数。

接口配置项

一般在开发时,接口的可选配置有:接口模式(实际配置的是单、双工模式选择)、设备主从模式、数据宽度、时钟极性(CPOL:)、时钟相位(CPHA)、时钟速率、数据bit位大小端选择。

接口模式

标准的四线SPI接口,使用的场景是主从机进行数据交互的通信,两方都有数据的收发过程,而在LCD/OLED这样的SPI接口作为从设备的器件中,就不需要数据返回给主机,只需要接收来自主机的控制信息和显示的数据。

基于这样的使用场景,就可以配置成三线的单工通信,即仅需要从机选择SS、时钟SCLK、数据输出MOSI即可。

设备主从模式

这个配置一般需要看芯片是否支持,可将芯片配置成SPI主机或者从机,能更好地集成在项目的系统中。

数据宽度

顾名思义,就是发送数据可以配置成8bit、16bit等,这也是根据芯片而定。

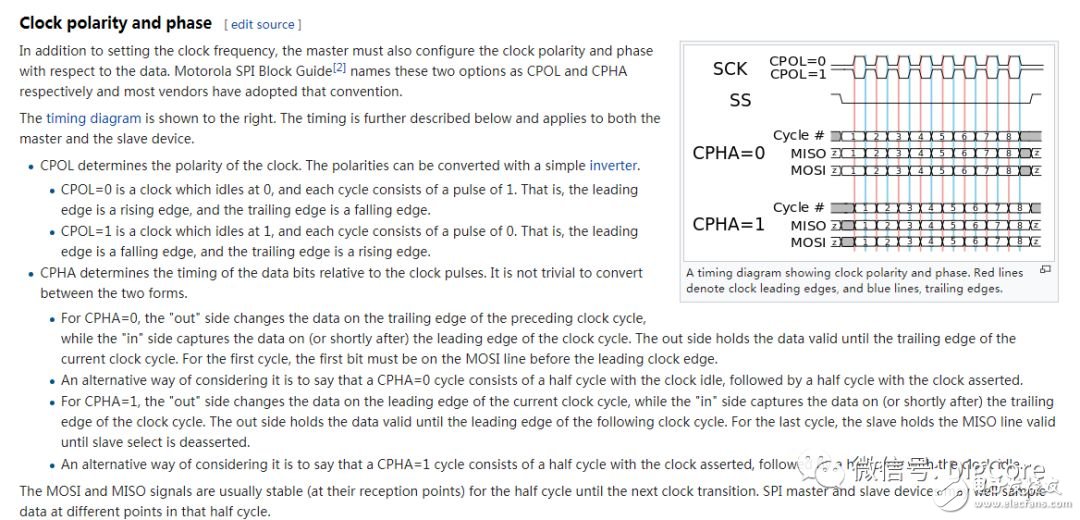

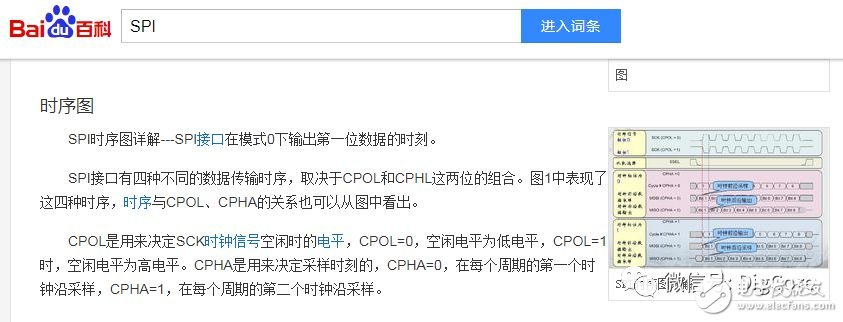

时钟极性、时钟相位

这两者分别是CPOL(Clock Polarity)、CPHA(Clock Phase),极性就是指高低电平,这个定义了SPI总线在空闲状态下,时钟保持高电平还是低电平,因为这个关系到了SPI通信时第一个时钟跳变沿是上升还是下降沿;相位指的是时钟的跳变沿,指定了数据信号的输出和采样如何与时钟对齐。

这两个配置,在Wiki和百度百科上都做了非常清晰的解释,这里截图引用如下:

时钟速率

速率选择定义了时钟信号线在数据传输是的翻转速率,这体现到每个芯片定义的接口时序图中,即可承受的速率范围,如果主机设的速率太快,而从机响应过慢会导致通信失败。

数据bit位大小端选择

数据的发送优先bit可配置,从上篇的UART协议可以知道,UART规定了数据优先发bit0,而这个SPI是可配置优先发送bit的,可设置最低位或者最高位。

从FLASH型号为GD25Q32和OLED型号为QG-2832TLBFG04的时序截图可看到,这两个器件都是优先发MSB,也就是最高位优先。

再对比一款字库芯片型号为GT21L16S2W的读取指令:

可见SPI器件普遍采用MSB的发送优先顺序。

总结SPI通信接口,一主多从的通信架构,标准模式有四根信号线、依靠选择信号SS开始通信、时钟信号SCLK进行逐bit输出和采样、可配置的采样时刻和可选择的优先发出bit。

-

SPI通信协议的基本概念和工作模式2024-09-09 4079

-

SPI通信协议原理是什么2023-11-24 2054

-

一文搞懂SPI通信协议2023-06-06 1763

-

SPI串行外设接口设计实现2023-05-29 2163

-

常用的串口通信协议之SPI协议简析2022-07-07 5004

-

STM32如何模拟SPI通信协议2022-02-17 2095

-

SPI通信协议的相关资料推荐2022-01-26 1139

-

通信协议:SPI2021-12-22 1082

-

SPI 串行外设接口2021-12-20 795

-

STM32——SPI通信协议(W25Q128FLASH的通信)2021-12-02 1022

-

串行外设接口SPI模块简析2021-11-08 1206

-

基于FPGA与MCU通信的SPI协议设计2021-11-05 1056

-

SPI通信协议2018-10-12 2910

-

一文读懂SPI串行外设接口2017-04-27 10740

全部0条评论

快来发表一下你的评论吧 !