基于FPGA的同步复位的3位计数器设计

可编程逻辑

1390人已加入

描述

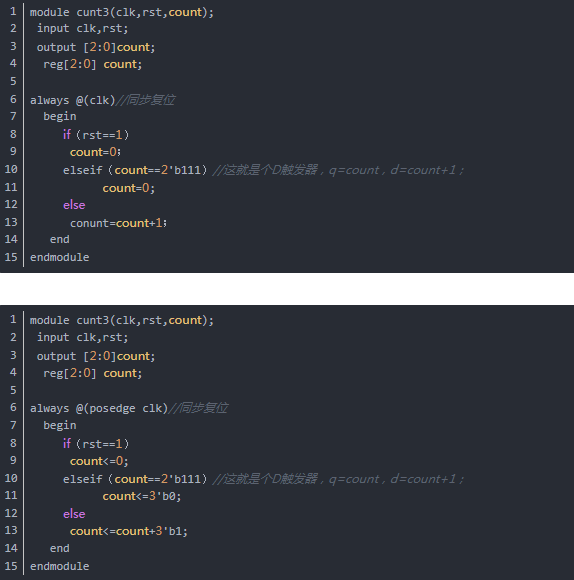

分析:首先,我们可以看到有哪些信号。复位rst 、计数器3位的、时钟信号。(用到2路选择器。复位和不复位)

其次,怎样实现,一个时钟过来,记一次数就是加一次,保存(用到D触发器),满之后为0;

最后,按照以上分析,进行编写程序。

上面是修改过的,由于时序逻辑电路,因此。用非阻塞赋值。q是3位,因此加上3‘b1,

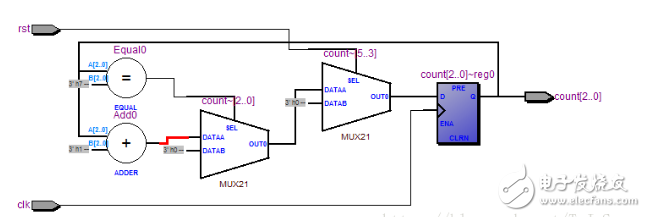

输入代码,选择Processing 》 start 》 Analysis & Elaboration

Tools 》 Netlist viewer 》 RTL viewer

经过以上步骤,则得到以下电路。

从图中可以看出有两个2选1选择器和一个D触发器集合(因为存储的是3位数据,需要3个D触发器),另外还有一个加法器和一个比较器。

因此,可以表明从程序里就可以看要用那些元件,从而能更好的理解程序的用途。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

同步4位计数器数据表2024-05-15 366

-

同步计数器和异步计数器各有什么特点2023-12-15 3135

-

同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?2023-03-25 29407

-

可预置同步4位二进制计数器;同步复位-74HC_HCT163_Q1002023-02-21 537

-

可预置同步BCD十进制计数器;异步复位-74HC1602023-02-20 1053

-

可预置同步4位二进制计数器;同步复位-74LVC1632023-02-16 693

-

可预置同步4位二进制计数器;异步复位-74LVC1612023-02-15 745

-

构建一个4位二进制计数器2022-12-02 6528

-

4位同步计数器2019-06-23 27659

-

利用复位端构成的模6计数器电路2010-01-12 5947

-

第二十五讲 同步计数器2009-03-30 9949

-

12进制计数器2008-07-05 11682

全部0条评论

快来发表一下你的评论吧 !