在FPGA中实现MCU内核的快速运行

描述

有时,微控制器本身可以完全吸收设计的所有功能要求。对于绝大多数嵌入式系统设计而言,编程良好,高度集成的嵌入式处理器是工程师可以使用的最具成本效益,功效最高,速度最快的解决方案。

当原始性能至关重要时,捕获的逻辑专用硬件可实现最高性能。例如,定序器可以比软件中实现的相同逻辑快一个数量级。由于分立逻辑器件占用大量空间和功率,因此添加FPGA是一种可行的替代方案。在许多情况下,FPGA和微控制器的组合是一个很好的解决方案。当微控制器在FPGA的逻辑中实现时,可以实现更密集的解决方案。作为硬编码的宏,或者在每个新设计中被替换和布线的软宏,整个微控制器吸收到FPGA的房子不仅可以产生最高的密度,而且可以产生最大的灵活性,特别是如果你足够勇敢地修改核心以提高性能。本文着眼于在现有FPGA中快速运行的微核。这些可以从各种来源获得,包括开放和封闭,免费和IP许可。

比原始版本更好

可以使用传统架构和专有架构,每种架构都有优势。传统内核与传统微处理器兼容,并提供熟悉的体系结构。您公司生产的产品可以使用已经过测试和验证的代码。当需要下一代产品甚至是新的改进模型时,组织良好且可靠的代码库的可重用性可以节省大量时间。

几种流行的内核已经以原始逻辑形式实现了各种各样的FPGA系列包括诸如Microchip PIC,Intel 8051,Atmel AVR,Motorola 6502,Intel 8080和Zilog Z80微控制器等处理器。一个不那么明显的优点是能够改进初始化建筑。如果时间和资源允许,可以克服缺点,因为您可以修改设计。例如,非常流行的8051架构最初采用有序架构,每条指令需要12个时钟周期。精确的传统实现可以反映初始功能,或者可以实现更现代的风格,减少每条指令的时钟周期数。

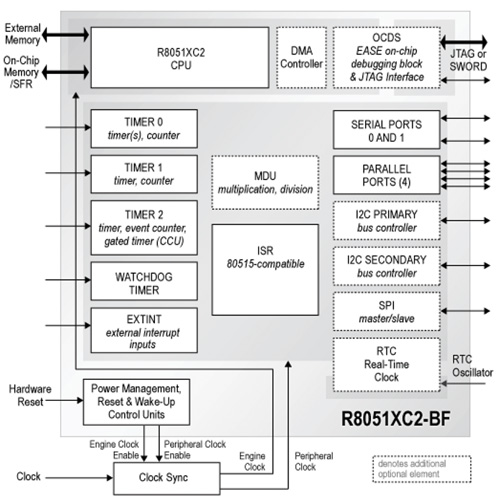

改进的8051 IP内核也可用于跨平台开发。 R8051XC2-BF核心¹可用于ASIC或Xilinx和Altera FPGA;它通过添加第二个数据指针(初始设计的缺点)和JTAG调试接口(图1)改进了初始设计。

图1:传统核心的商业可用实现通常会改进初始的离散设计。这个8051内核每个指令运行一个时钟,并添加JTAG和第二个数据指针。

ARM内核虽然许多设计可以使用8位内核,但现代功能可能需要更高的总线宽度来简化处理。如果您正在操作24位宽的图形数据,则单个32位传输比三个8位传输更有效。

最流行的32位架构也许是ARM®Cortex™,令人惊讶的是,它已成为FPGA实现的流行且受到良好支持的架构。从面积和功耗角度来看,ARM Cortex非常高效。可扩展的架构得到众多工具和开发套件的很好支持,以及外围设备,内存管理,数学和DSP功能的开源代码。

ARM内核的一个很好的特性是它们不属于一个FPGA制造商,可以在不同制造商的设备上实现。这意味着随着设计的发展或需求的变化,您不会被锁定在一个供应商中。另一个好处是,架构可以从更简单,功能更少的Cortex M0扩展到非常高端的多核A8和A9风格。此外,还具有经过赛道验证的驱动程序和堆栈,可用于高端外设,如USB,以太网,Wi-Fi,ZigBee,蓝牙等。

Xilinx系列产品是嵌入式微核的大支持者,而ARM架构也不例外。像XC5VLX50-1FFG676C这样的器件是XilinxVirtex®5系列的一部分,它是一个非常大,密集,高端的FPGA的例子,它可以在芯片上安装一个快速而密集的系统。 550 MHz器件具有440个I/O和超过46,000个逻辑模块,不仅支持ARM内核功能,还支持高达72位宽的存储器宽度,流水线操作,FIFO,具有高达16.4 Mbits内部块存储器的双端口存储器和DSP功能。

Microsemi是另一家提供ARM内核支持的FPGA制造商,ProASIC3系列是一款优秀的目标技术,具有令人印象深刻的低端到高端逻辑,I/O,RAM和门数15,000到3,000,000。一个很好的例子是A3PE3000-FGG484具有341个I/O和516 Kbits的内部RAM。

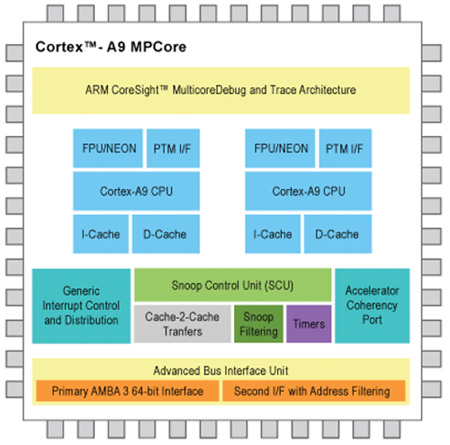

Altera具有可比较的部件,如EP3SL50F780C4N,它同样支持ARM核心处理器,并为DDR,DDR2,DDR3,SDRAM提供内存支持更多,最多24个模块化I/O bank,448 I/O(系列中最多744个)。作为Stratix®III系列的成员,Altera可以访问Altera Mega-Function合作伙伴计划(AMPP),以获取可用的外设,内核和支持。 Altera还通过其Altera MegaCore功能支持多种知识产权(图2)。

图2:高端32位ARM架构是许多FPGA的流行核心。该Altera版本增加了多核调试和跟踪功能,简化了单个FPGA内多个实例化处理器内核的设计。

专有内核

除了行业标准的微控制器内核外,FPGA制造商还提供专有内核,这些内核具有非常高的逻辑效率,可扩展至8至32位的性能水平。这些供应商的关键不是在不需要的功能和外围设备上浪费逻辑;经常缩减,实现了裸机处理单元,以提供基本的可编程性和FPGA内部大型逻辑池的接口。这不仅可以让内核快速运行,而且还可以保持它们足够小,以便在SoC内部创建自己的双核,四核甚至八核处理器。

Xilinx指定Blaze这样的内核,可以同时使用PicoBlaze和MicroBlaze口味。 PicoBlaze是一种8位RISC架构,具有高达240 MHz的性能。它主要设计用于VHDL设计流程,并作为VHDL源文件提供。一旦在13个不同的Xilinx系列中实现,它就不需要外部元件,完全在主机部分内部运行。

支持的系列包括Kinetex-7,Artix-7,Virtex(4,5,6,7,II-Pro) )和Spartan®(3和6)。从资源和复杂性的角度来看,PicoBlaze是Spartan(双关语)。它具有一个16 x字节宽的通用数据寄存器,1K可编程片上程序存储器(在FPGA配置期间自动加载),一个带有CARRY和ZERO指示器标志的字节宽运算逻辑单元(ALU),64字节内部暂存器RAM,256个输入和256个输出端口,便于扩展和增强。另一方面,它具有可预测的性能,每条指令总是两个时钟周期,高达240 MHz(或Virtex-4中的100 MIPS) FPGA)和88 MHz(或Spartan-3 FPGA中的44 MIPS)。 PicoBlaze对Xilinx用户免费提供,并附带汇编程序和VHDL源代码。

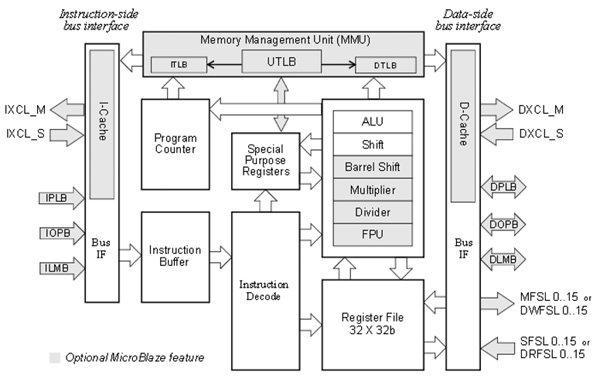

高端是Xilinx MicroBlaze。这是一个32位RISC Harvard架构软核处理器内核,具有32个通用32位寄存器,ALU,针对嵌入式应用优化的丰富指令集,三级MMU/MPU支持等。

灵活性该核心(图3)允许您选择性能优化的五级流水线,使用Kinetix-7系列(例如XC7K70T-1FBG676C)或3级流水线区域优化版本可实现高达317 DMIPS在Xintex-7或Virtex-6和7系列器件(如XC6VLX130T-1FFG784C)上仍然可以达到令人尊敬的264 DMIPS。

图3:用于Xilinx FPGA的专有32位MicroBlaze内核有条件编译指令允许你添加你需要的块,并消除你不保存逻辑和提高密度的块。

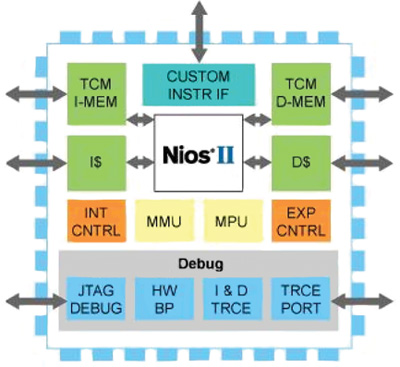

Altera还提供了一个名为NIOS的专有内核,现在是第二代NIOS II版本(图4) 。作为业界使用最广泛的软处理器,它具有功率灵敏度和安全关键(DO-254)兼容性的实时性能。

图4:Altera的第二代NIOS II内核被誉为FPGA中使用最广泛且支持的IP内核,并带来了许多开发和调试功能。

六级流水线NIOS内核可以实现少至600个逻辑单元和特征向量中断控制,紧密内存和DSP耦合,以及添加自定义指令(最多256个)的能力。它可以使用内存管理单元(MMU),并在开源和商业支持的版本中支持嵌入式Linux。

可行的替代方案

您的设计细节将决定您是应该选择硬宏还是软宏。硬宏占用FPGA内部的特定位置和资源,但硬编码宏的特性更好,可以实现更好的性能。

软宏也可以实现良好的性能,特别是如果你足够勇敢修改,改进,或平行他们。一如既往,良好的设计实践将产生最佳结果。总之,当需要尽可能高的密度和/或性能时,选择FPGA内部的软处理器而不是传统的微控制器及其所有支持电路可能在灵活性,效率,性能,功耗和空间方面,这是一个更好的解决方案。

-

FPGA与MCU的应用场景2024-07-29 8468

-

在FPGA中实现MCU内核的快速运行2023-08-14 1658

-

MCU之SWM在KEIL环境中实现代码在RAM中运行2023-03-16 4517

-

AGM MCU+FPGA的相关资料分享2021-11-01 1696

-

AGM MCU+FPGA2021-10-25 979

-

FPGA中LPM_ROM设计快速实现2021-08-04 714

-

用FPGA做的MCU内核的汇编指令集完全解析2020-03-04 3005

-

在Nimbix云加速工作流中实现FPGA开发和运行2018-11-29 2214

-

在Xilinx FPGA上单源SYCL C++实现运行的方法2018-11-20 3825

-

FPGA VI中不同的Xilinx内核生成器IP设计实现与子模板说明2017-11-18 1772

-

51内核在FPGA中的使用2016-11-14 9151

-

TCAM在高速路由查找中的应用及其FPGA实现2015-11-04 1137

-

LOG算子在FPGA中的实现2011-05-16 1264

-

在FPGA中实现高精度快速除法2010-07-17 718

全部0条评论

快来发表一下你的评论吧 !