可编程时钟振荡器系统的应用设计

描述

时钟和时钟振荡器(也称为时钟发生器)几乎是每个电路的一部分,大多数系统的设计都不止一个。事实上,设计中有四个,六个或更多,支持内部电路以及外部I/O和接口并不罕见。它们建立最终载波设置或重新建立并与接收信号载波同步。此外,许多系统都需要能够更改或转换时钟,以满足超过单一终端应用情况的调整要求。

时钟在为各种应用提供服务时提供了广泛的功能和特性,但是还有相当多的命名和功能混淆与重叠的术语,如时钟,振荡器,发生器和合成器等。

固定频率时钟用于处理器,存储器和其他外围设备的调步。同一系列中的一系列类似产品可能需要不同的时钟频率,以支持各种速度选项或功能。这些固定频率时钟也可以用作有线和无线链路中的基本定时参考。一些时钟元件包括晶体或其他定时源,用于产生输出;其他需要用户提供外部晶体。

一些固定频率设备是可编程的,因此可以在多个BOM(物料清单)上使用相同的设备来简化库存,但即使是“可编程”设备也可能存在误解。它们可以是供应商的一次性可编程,OEM生产线上的一次性可编程,电路板上可编程的引脚带,或软件可编程甚至可以“动态”重新编程。此外,还有可编程时钟,可以重新编程有限次数,频率甚至可以改变几次,以适应不同的生产和应用需求。为了增加潜在的复杂性,一些时钟振荡器提供多个同时独立的输出,因此单个晶体和器件可以提供大多数系统所需的多个时钟。

此外,还有合成器使用单晶或主时钟在指定范围内产生任意频率输出。与基本时钟振荡器一样,一些合成器一旦固定就固定,其他合成器可动态设置,以根据需要提供指定频谱中的任何频率(通常是载波)。

在无线系统中,有两组基本时钟:用于设置通道基本时序的固定频率,例如点对点专用链路,以及可根据需要移动频率的时钟支持不同的频道,例如Wi-Fi链路上的跳频。

选择注意事项

考虑到所有时钟选项,确定哪种基本时钟方法是合适的可能是一个挑战。但是,通过专注于主要规范可以简化该过程,因为并非所有时钟配置选项都具有可比较的规范。只有满足这些顶级要求的设备才能在各种配置中考虑。与往常一样,性能的权衡需要根据性能属性的权重进行评估。

最关键的形式是时钟的最大标称频率能力,对于大多数无线应用来说,它将跨越几百个MHz到GHz范围。对于可编程器件,最大值和最小值都很关键;时钟IC通常具有10:1或5:1最大/最小跨度。

另一个重要规格是给定设置下的初始频率误差(容差),以百分比,Hz或百万分率表示。如果时钟不是固定频率设备,则该数量可以根据标称频率而变化。

所有振荡器都会漂移。如果器件包含内部晶体,或者它使用模拟电路调节和缩放外部晶体,它将随温度发生一些漂移;如果它是一个全数字设备,漂移将会更少,尽管仍然会有一些阈值,逻辑门的时序会略有变化。高性能振荡器的温度系数通常以ppm/⁰C表示,其值范围从大约十到几百。当然,最大可接受值取决于应用。

对于频率在使用期间动态切换的振荡器,而不是仅在初始上电时通过用户启动的调谐或模式切换进行更改,关键参数是确定新频率的时间。根据振荡器的架构,对于合成器或基于PLL的设计,或者相对较长的时间,这几乎是瞬时的。即使核心电路没有不连续性(如某些架构那样),如果相关的输出缓冲放大器或驱动器必须在很大范围内摆动,可能会出现建立时间问题。通常,小的频率变化并不具有挑战性,但是广泛的变化可能会有更长的稳定时间;实际上,振荡器必须在整个范围内快速转换的应用很少。

在许多情况下,漂移也是一个考虑因素。具有内部晶体的时钟由于晶体老化而表现出短期和长期漂移,尽管这些术语可能与每个供应商具有不同的定义。有些人将“短期”定义为一年,将“长期”定义为五年,十年甚至二十年。最后,将功耗和封装尺寸因素问题纳入决策,但与基本性能规范相比,这些通常是次要的。一般来说,低功耗器件的规格要低于消耗更多功率的器件,但这是一个工艺,设计和测试的进步意味着权衡利弊的领域。

抖动:最具挑战性的问题有很多原因

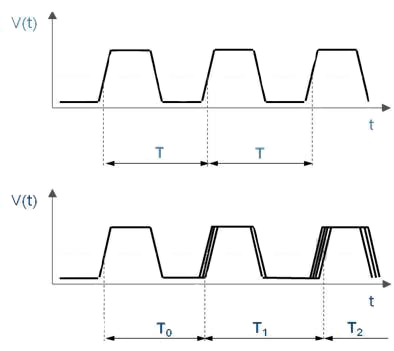

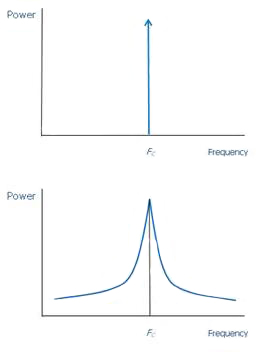

在决定振荡器选项时工程师必须评估的最关键参数中,抖动是最难以表征和匹配的应用。在时域中,抖动表现为“完美”输出的微小变化(图1);在频域中,它表现为相位/频率变化(噪声)和单频信号频谱的扩展(图2)。两种观点都是同样有效的方式来观察相同的物理现象,哪种观点取决于具体情况,适用的标准和系统性能要求。

图1:在时域中,理论上“完美”的时钟信号(顶部)显示了微小的来回变化(底部)被定义为抖动。 (由IDT提供)

图2:在同等合法的频域替代视图中,完美的单频尖峰(顶部)变为频率分量和相关能量的传播(下图)。 [由IDT提供]

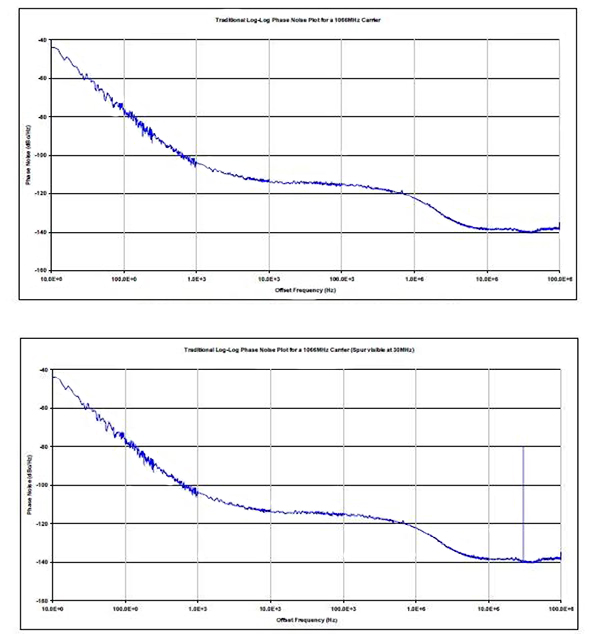

抖动是一个复杂的主题,并且由于几个原因通常难以量化。它通常相对较小,但仍然是系统性能的重要因素;它有许多贡献源,包括内部电路噪声,外部源噪声,元件热噪声,元件缺陷和热致机械变化。作为概率特征,没有单一的正确或简单的方法来定义它;在使用的许多定义中,有许多定义是峰值,均方根,平均值,短期变化和长期平均值等等。抖动也可能在输出上显示为非谐波相关的频率杂散,与基频相距一定距离(图3a和3b)。

图3a和3b:与抖动相关的杂散是不需要的频率分量,与基波无谐波相关;上部迹线是对数 - 对数相位噪声图,显示1066 MHz时钟频域的无杂散抖动;较低的走线是相同的时钟,但与基频相比具有30 dB的30 MHz偏移。

抖动的影响范围可以是A/D采样误差和D/A转换时间,“噪声“在信号上,增加了BER(误码率),增加了符号间干扰,以及许多其他表现形式。通常,时钟抖动的可见影响在系统的其他地方,例如对不可避免的信道噪声的容忍度降低,这会在采样窗口收缩并且ISI眼图关闭时发生。抖动与整体系统性能之间的联系有时难以判断,并且通常由于额外的抖动而使电路的非时钟部分增加到时钟信号本身。振荡器抖动还可以建立相位本底噪声,以dBc/Hz为单位,是一个品质因数(FOM),对于高性能接收器通道或雷达系统等应用非常重要。

匹配时钟发生器时针对应用的抖动规范,最好查看业界为该应用设置的标准(如果有)(例如IEEE 802.11x),阅读与应用相关的应用笔记,并仔细研究数据表及其应用测试条件和脚注。

示例显示了不同的产品

两个时钟振荡器/发生器IC系列展示了这个基本功能如何演变成非常不同的组件。 Silicon Labs Si5xx产品组合非常适合从网络设备,基站,存储区域网络和广播视频系统到数据通信和电信的单板计算机等应用。这些单,双和四I 2 C可编程频率器件的工作频率范围为100 KHz至1.4 GHz,具有低抖动操作特性。例如,Si535提供0.19 ps RMS类型的相位抖动,从而提高了设计余量和系统级性能。与传统的XO不同,Si535使用一个固定晶体来提供宽范围的输出频率,而每个输出频率都需要不同的晶体。这种基于IC的方法允许晶体谐振器提供出色的频率稳定性和可靠性。此外,DSPLL时钟合成可提供卓越的电源噪声抑制,简化了在通信系统中常见的嘈杂环境中生成低抖动时钟的任务。

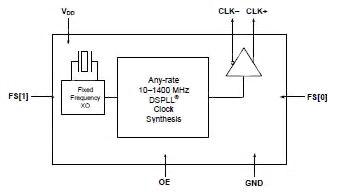

同样,供应商的Si534是一款四频晶体振荡器,可以在10至945 MHz的任何频率和1400 MHz的选定频率下提供单一输出(图4)。它针对通用无线和有线链路,由供应商根据各种用户规范进行配置,包括频率,电源电压(3.3,2.5和1.8 V),输出格式(CMOS,LVPECL,LVDS和CML),以及温度稳定性;请注意,包括抖动在内的规格会因这些设置而异。在这种情况下,用户可以通过小型(5×7 mm)8引线器件封装上的两个控制引脚选择四个可用频率中的哪一个(工厂设置为用户订单)应出现在该器件的输出端,包括内部晶体。

图4:Silicon Labs XO包含一体化晶体;它由供应商按照客户选择的四个输出频率进行编程,然后可以通过两条控制线随时调用四个中的任何一个。

典型的初始精度在25°C时为±1.5 ppm,而第一年漂移为±3 ppm,超过20年的漂移据说最大为±10 ppm。该供应商提供了许多抖动规范,其中包括500 MHz以上输出频率的相位抖动(rms),0.25 psec(典型值)和0.40 psec(最大值),以及622.08 MHz的典型输出相位噪声-146 dBc/Hz(用LVPECL输出)。在四个可能的时钟输出之间切换时的建立时间最长为20毫秒。

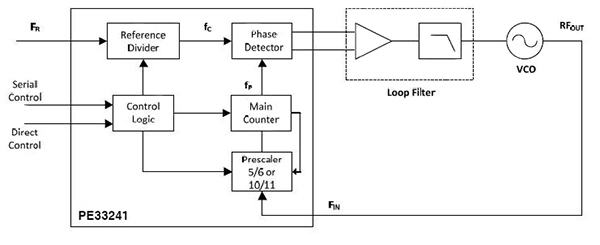

同样值得注意的是Peregrine Semiconductor PE33241针对无线本地环路(WLL);射频产生; L,S和C波段合成器;和通信系统,移动终端,遥测,雷达和便携式无线电中的时钟恢复(图5)。这种用于低相位噪声应用的整数N锁相环(PLL)频率合成器可以使用10/11预分频模数达到5 GHz,使用5/6预分频模数可达到4 GHz(后一模数选择可提供更好的规格) )。建立输出频率的计数器值可由用户通过其串行接口或直接硬连线配置进行编程。这款48引脚7×7 mm QFN器件的相位噪声基底FOM为-230 dBc/Hz。

图5:Peregrine的PE33241半导体根据所选的模数对提供4或5 GHz的用户可选输出;极低相位噪声基底FOM为-230 dBc/Hz,非常适合雷达,遥测和高级移动无线电系统。

该IC的频率范围和高性能意味着在给定的应用程序中评估和正确编程它可能很困难。因此,供应商提供带有USB接口的评估板(指定为EK33241-13),以便在使用外部稳定的低噪声参考源时展示出最佳的相位噪声性能(图6)。在这些GHz频率下,无处不在的FR-4 PC板材料不适合,因此评估板由四层堆叠组成,两层外层为Rogers 4350B(εr= 3.48),两层内层为FR406(ε) r = 4.80)材料。 12密耳(0.30 mm)厚的内层为RF传输线提供接地层,总板厚为62密耳(1.57 mm)。

图6:在GHz频谱中提供低噪声,高性能规格的器件很难评估并集成到整个系统设计中,因此Peregrine提供了一个USB兼容的评估板来完成任务。

-

可编程时钟振荡器用作FPGA系统的时序参考有何优势?2013-08-15 3190

-

利用可编程振荡器增强FPGA应用2014-03-31 3391

-

爱普生可编程石英振荡器都有哪些系列?具有什么使用特点?2017-01-04 4524

-

了解今天的可编程振荡器2009-03-28 668

-

可编程振荡器,什么是可编程振荡器2010-03-22 2935

-

可编程时钟振荡器的电路原理图免费下载2021-03-21 1207

-

AN-585:AD5232-使用数字电位器的可编程振荡器2021-04-18 867

-

AN-580:采用数字电位器的可编程振荡器2021-04-24 805

-

模拟可编程单结晶体管器件振荡器设计2021-06-27 1037

-

带振荡器的可编程延迟定时器-74HC55552023-02-21 535

-

可编程振荡器助力医疗成像提供准确时序,兼容SiTime2024-03-18 1075

-

替代SiTime,可编程振荡器用于视频处理器稳定时钟信号2024-06-28 908

-

国产可编程振荡器可用于对讲机,替代SiTime2024-07-03 950

-

深入解析 MEMS 可编程 LVPECL/LVDS 振荡器 SiT9120 系列2024-08-13 1220

-

YXC高精度的石英可编程压控温补振荡器:YSV531PT系列2025-12-25 197

全部0条评论

快来发表一下你的评论吧 !