通过数据传输满足MCU激进系统的设计

描述

基于MCU的设计面临越来越激进的系统要求。无论是超低功耗,高性能还是两者的难度组合,提供满足当今激进目标的设计都是一项艰巨的任务。基于MCU的设计中最常见的操作之一是数据移动和数据传输功能的有效实现,这对于达到低功耗或高处理目标至关重要。详细了解支持快速高效数据传输的现代MCU中包含的各种功能对于创建最佳MCU设计至关重要。

基础知识

数据移动可以从一个功能块到另一个功能块,或关闭-chip使用标准接口。片上和片外传输通常涉及标准外设或存储器接口。现在许多外围设备都包含更高级别的功能,这些功能可以独立于CPU运行。一个例子是将数据本地缓冲到外设,以便在方便的数据包中完成传输,从而最大限度地减少CPU开销。

使用特殊的数据传输资源可以有效地完成片上数据移动。例如,外设和存储器之间的数据传输可以使用智能直接存储器访问(DMA)功能完成。 CPU只需要参与设置传输参数(例如存储器位置,传输长度和有效外设),并在传输完成时通知。 CPU可以在传输数据时执行其他任务,也可以将其置于低功耗模式以节省功耗。

许多现代MCU都包含先进的片上总线结构,有助于支持多个数据传输同时发生。当多个数据流同时移动时,可以实现最高的数据传输带宽。此外,在这些情况下,与顺序执行数据传输相比,功耗通常要低得多。现代MCU中还包含许多其他功能和功能,可帮助实现高效的数据传输。这里不可能说明所有这些,但我们将回顾一些最常见的功能。一旦了解了这些,通过扩展,将清楚如何使用其他功能来提高设计中的数据传输效率。我们将看看四个关键示例,了解如何提高数据传输效率:智能USB外设如何降低CPU开销,智能DMA如何独立管理复杂数据移动要求,低功耗模式如何在数据传输过程中提高电源效率,以及先进的片上总线矩阵如何支持多个同步数据传输功能。我们还将看到,当这些功能结合使用时,甚至可以实现更高的效率。

智能外设:USB示例

USB是一个很好的示例外设,用于显示数据传输的可能改进。早期的USB实现最大吞吐量仅为1.5 Mb/秒,标准的一些元素基于这种慢速数据。随着标准的更高性能版本的出现以及更广泛的应用程序的定位,USB外设实现需要变得更具创造性。特别是,接近12 Mbit/s全速USB标准的理论最大值需要一些差异化的功能。 Atmel为XMEGA MCU的USB外设实现增加了几项功能,可显着提高效率。这些功能也很好地说明了可以与其他类型的外设一起使用的类似技术,以提高数据传输效率。

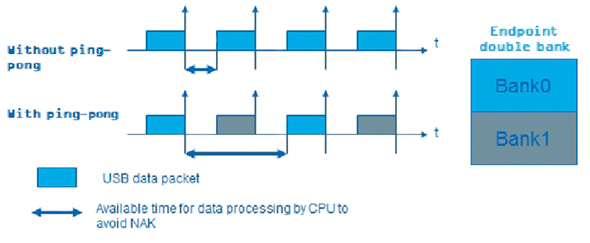

通常,单个内存缓冲区用于外设数据传输。如果数据缓冲区已满,MCU将以NAK(否定确认)消息进行响应。收到NAK后,主机将等待并稍后重试传输。它将继续重试,直到MCU可以成功接收数据。 Atmel XMEGA MCU使用乒乓缓冲区来消除此问题。乒乓缓冲区使用两个存储区进行数据传输。当一个银行满员时,主机可以将数据传输到另一个银行。两个缓冲区之间的交替消除了重试并提高了整体数据带宽。此外,如图1所示,在乒乓配置中使用两个存储体,使MCU有更多时间处理数据。如没有乒乓球的图所示,CPU只能处理传输之间的数据。通过乒乓,CPU可以在传输周期的一部分期间处理数据,并降低NAK被要求“赶上”数据处理要求的可能性。

图1 :乒乓数据缓冲提高了效率(由Atmel提供)。

有助于提高Atmel XMEGA MCU数据传输效率的另一个关键特性是多数据包缓冲传输模式。当通过USB端口传输的数据包超过全速USB的BULK传输模式中允许的最大值(64字节)时,使用此模式。在包含此功能之前,需要在主机上拆分数据包,然后在接收器处合并,从而导致CPU负载增加。多数据包缓冲功能为USB外设添加专用硬件,以便在数据包大小大于最大USB数据包大小时自动执行数据包拆分和合并。请注意,此模式还减少了所需的中断次数,因为只有在整个传输结束时才需要中断CPU。这意味着CPU可以处理其他任务或进入睡眠模式,直到整个传输完成并准备好进行处理。

结合乒乓缓冲和多传输模式可以提高传输带宽5.6 Mb/s(在没有任何特性的基线BULK传输实现中)为8.7 Mbits/s。也许更重要的是,在使用这两种功能的情况下,CPU负载从46%(在基线中)降低到仅9%。这些功能的结合使用可以在性能和功耗方面实现出色的改进,这正是智能外设可为您的设计带来的好处。在下一个设计中寻找关键外围设备的类似功能。有关更多信息,Atmel提供有关XMEGA USB连接的产品培训模块。

使用智能DMA进行高效的数据传输

大多数设计人员熟悉的第一个面向数据传输的特殊功能可能是直接内存访问(DMA)。此块可以自动将数据从源移动到目标。第一代DMA传输功能只不过是一个地址寄存器,它可以与一个小型状态机一起递增,以管理存储器的读写信号。现代DMA控制器包括高级功能,可以从最复杂的数据传输操作中尽可能地卸载CPU。 Renesas RX621 MCU系列DMA实现是一个很好的例子,可以看到一些可用于数据传输功能的更高级功能。

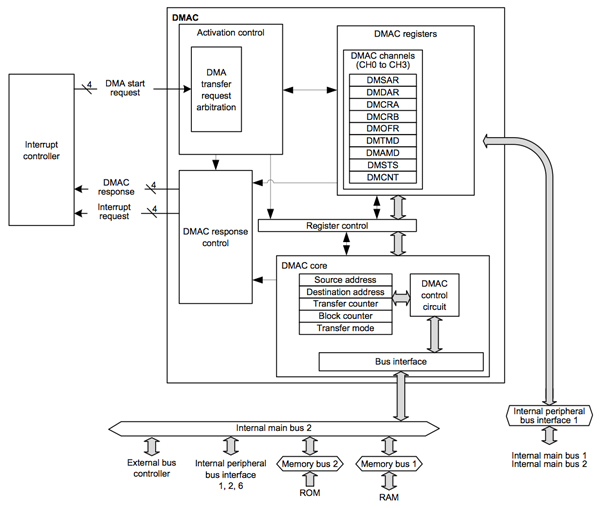

RX621 MCU DMA控制器(图2)可以连接到中断控制器,以便中断驱动数据转移是可能的。例如,智能外设可以缓冲数据,直到数据包可用于传输。它可以向DMA控制器发出中断,并且数据包可以移动到主存储器以供CPU处理。在大量数据包可用之前,CPU可能不需要处理数据,因此DMA控制器可以等到已经传输了足够的数据包以便向CPU发出启动中断。请注意DMA与外设数据缓冲区,较大的主内存缓冲区和集成中断系统的使用如何协同工作以消除CPU数据传输开销。您可以通过将算法与MCU中的自主数据传输资源相匹配来实现显着的效率提升。

图2:Renesas RX621 DMA控制器框图(由Renesas提供)。

RX621 DMA控制器具有四个独立通道和多种寻址模式,无需CPU干预即可支持复杂的数据传输。例如,在DMA传输期间使用偏移量添加会跳过存储器序列中的地址。这允许在目的地地址处自动收集分散的源数据元素。您甚至可以使用偏移添加功能实现复杂的操作,如矩阵翻转(数据元素的X和Y位置交换)。当所有需要的数据连续存储时,这些类型的操作可以为非常有效的CPU处理分段数据。如果CPU需要不按顺序访问数据,则缓存未命中可能会显着降低处理效率。寻找类似的机会来收集数据,以便在数据处理算法的“内部循环”中实现高效的CPU访问。

RX621还包括两个其他DMA功能,可进一步提高数据传输效率,数据传输控制器(DTC)和外部存储器DMA控制器(EXDMA)。 DTC是类似DMA的功能,但数据传输信息(起始地址,传输长度等)作为激活向量存储在主存储器中。这允许支持更复杂的数据传输操作。一旦当前传输完成,可以通过自动移动到新的激活向量来实现传输链。通过管理传输记录中的各种链接,可以定义复杂的数据传输操作,然后根据所需操作的需要将其链接在一起。 CPU开销最小化,因为它只需要在传输启动之前管理链接配置数据的设置和拆除EXDMA子系统专为外部存储器总线传输而设计。它具有两个通道和普通DMA控制器的许多常规功能。另外一种传输模式Cluster Transfer可以有效地用于管理复杂的数据缓冲结构。双地址模式用于有效地同时进行两次数据传输。一次数据传输将数据集从一个位置移动到集群存储区域。第二次传输用于将数据从群集区域移动到不同的存储区域。这种方法可以简化网络数据包和视频帧的数据结构管理,从而消除CPU实现常见的缓冲区管理功能。寻找更专业的DMA控制器功能,因为MCU变得更加注重应用。

使用低功耗模式提高数据传输效率

实例表明,通过消除CPU甚至复杂的数据传输操作中的低级别参与,有很多机会减少CPU开销。这引出了一个问题,“如果不需要实现数据传输操作,CPU应该做什么?”在某些情况下,将CPU操作与数据传输重叠是有效的。通常捕获大量数据然后让CPU执行算法的处理和控制部分。如果可以捕获下一个数据集,则通过使用外设和DMA控制器在CPU对先前数据集进行计算时实现数据传输,有效处理带宽显着增加。如果您发现CPU足够强大,只需要一小部分处理能力,那么将CPU置于低功耗模式可能是有意义的,直到需要进行数据处理。

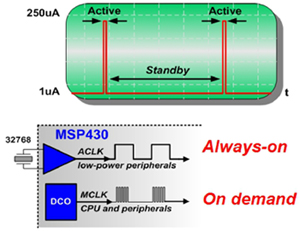

德州仪器MSP430 MCU系列具有多种低功耗模式,可用于在算法的一部分不需要CPU时切断功率。如图3底部所示,低功耗模式下有两个时钟源:按需高速数字控制振荡器(DCO)源时钟,MCLK和始终开启的低速外设时钟,ACLK。在活动模式下,MCU处于最高功率状态。两个时钟都处于活动状态,MCU的功耗约为250μA。在CPU关闭模式下,CPU关闭且时钟均打开,功耗为35μA。在待机模式下,CPU和DCO时钟关闭,而ACLK打开。在此模式下,功耗为0.8μA。最后,在全关模式下,CPU和时钟关闭,功耗仅为0.1μA。通过减少CPU处于活动模式的时间,并且如果待机功率足够低,则可以最小化由图3顶部曲线下面积表示的总功率。

图3:TI MSP430有功功率,待机功耗和快速时钟唤醒时间(由德州仪器提供)。

在Active Power中花费的时间不仅取决于所需的处理时间量,还取决于转换进入和退出低功耗状态所需的时间。在TI MSP430上(有关更多信息,请参阅TI产品培训模块),MCLK可在200 ns内激活,使唤醒时间几乎瞬间完成。这种快速唤醒时间意味着等待时钟变为活动状态所浪费的功率更少,因此可以立即开始处理。快速处理能力,快速唤醒时间和低功耗模式下的低功耗是高效MCU设计的“最佳点”。确保在MCU设计中仔细考虑这些元素。

使用片上总线矩阵进行多个同步数据传输

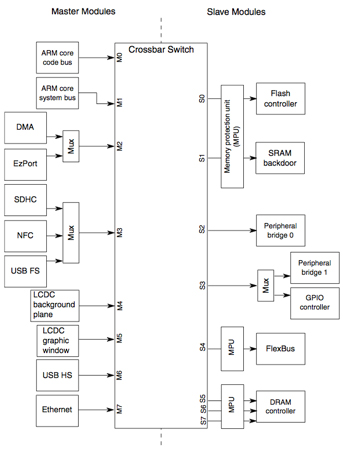

在前面的示例中您可能已经考虑过的一个可能的瓶颈,其中有大量的同时数据传输正在发生,要求多个片上总线有效地承载所有这些数据流量。具有高效多总线实现的MCU的一个例子是飞思卡尔Kinetis K70 MCU。 K70使用纵横开关(如图4所示)连接各种总线主模块和总线从模块。图左侧的八个总线主站可以连接到图右侧的八个从站。请注意,某些主服务器共享端口。例如,DMA和EzPort共享主端口M2。这些主设备永远不会同时处于活动状态,因此共享相同的主端口并不会发生冲突。

在某些多总线实现中,主设备可以连接到哪个从设备存在限制。 Kinetis K70实现了纵横开关,因此每个主设备都可以连接到每个从设备。这支持大量重叠的数据传输。特别是Kinetis K70的一个应用是针对需要大量数据传输的优化,是触摸屏LCD图形用户界面(GUI)。图4中的图表显示LCD控制器背景平面和LCD控制器图形窗口都具有单独的主设备。还有多个DRAM控制器从设备,因此两个LCD主设备都可以访问DRAM中自己的内存缓冲区。这显着降低了管理GUI显示的CPU开销。

图4:飞思卡尔Kinetis K70纵横交换机支持重叠数据传输(由飞思卡尔提供)。

纵横交换机上的其他主机也可以重叠操作以提高效率。例如,以太网主设备可以通过DRAM控制器直接向/从DRAM传输数据,而DMA控制器则管理速度较慢的外设和片上存储器之间的传输。算法可以根据处理要求轻松优化,而不会遇到连接不太良好的总线系统会造成的人为瓶颈。有关更多信息,请参阅飞思卡尔Kinetis产品培训模块。

总结

具有特殊数据传输功能和智能外设的MCU可以实现非常高水平的数据传输效率。但是,由于数据传输是绝大多数MCU设计中最常用的功能,因此了解如何有效地使用这些功能对于实现低功耗和高性能的积极设计目标至关重要。本文中说明的示例可以扩展到各种其他数据传输功能,因此您可以达到设计所需的效率水平。

-

【OK210申请】无线数据传输模块设计2015-07-24 1813

-

无线数据传输模块的实际应用2019-06-18 3995

-

高性能MCU和nRF24L01怎么实现无线数据传输?2019-08-16 2026

-

如何搭建无线数据传输系统?2021-03-09 1744

-

数据传输的通信系统设计2009-06-13 616

-

基于消息中间件的农电数据传输系统2009-08-18 623

-

PCI总线高速数据传输系统设计2009-09-21 930

-

基于ARM的无线数据传输系统设计2010-10-27 524

-

基于FPDP的高速数据传输系统设计2009-12-01 2390

-

Modem数据传输标准2009-12-28 1287

-

基于USB2.0的红外数据传输系统的设计与实现2010-03-13 1907

-

数据传输速率是什么意思2010-03-18 5178

-

基于MSP430和蓝牙技术的数据传输系统2017-08-13 1337

-

WNS无线数据传输模块2017-09-25 1017

-

Esp数据传输系统2022-12-19 635

全部0条评论

快来发表一下你的评论吧 !