USB连接器USB 3.1与USB Type-C的介绍

描述

通用串行总线(USB)是20世纪90年代中期开发的标准,用于标准化计算机和外围设备之间的连接,以便进行通信和提供电力。它取代了各种早期接口,如串行/并行端口,PS/2和便携式设备的独立充电器。

有三种连接器尺寸 - 标准型,迷你型和微型,型号“A” ,“B”,“AB”连接器和相应的插座,以及表1中总结的五种数据传输模式:

USB类型吞吐量方向总电容引脚数1.X 1.5 Mbit/s(低速)

12 Mbit/s(全速)半双工;不可逆《30pF 4 2.0 480 Mbit/s(高速)半双工;不可逆《10pF 4-5 3.0 5 Gbit/s(SuperSpeed)全双工;不可逆《1pF 9 3.1/Gen2 10 Gbit/s(SuperSpeed +)全双工;不可逆《0.1~0.5pF 9 Type-C 10 Gbit/s(SuperSpeed +)全双工;可逆《0.1pF 24

表1:USB数据传输模式。

USB 3.1/Gen 2基本上是USB 3.0,速度加倍,达到10 Gbit/s。它是全双工的,不可逆,因此连接器和插座必须以正确的方向对齐才能插入。它的总电容为0.1~0.5 pF。

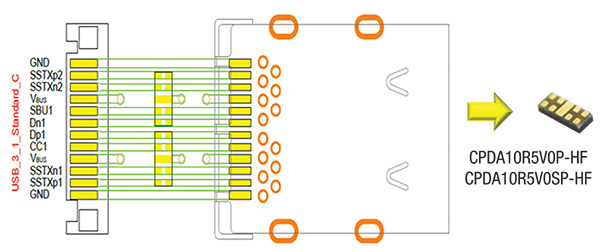

USB Type-C为10 Gbit/s且可逆(类似于Apple的Lightning),具有对称的24针脚,因此连接器将连接到第一个插座上尝试。附加引脚允许使用C型电缆支持数据协议,如DisplayPort 1.3,PCI Express和Base-t以太网。图1显示了USB Type-C电缆的引脚图。

USB Type-C的连接器和插座尺寸较小(类似于Lightning和Micro-USB),更耐用,可承受10,000次插拔。该电缆支持高达100 W的USB供电模式,可以更快地为智能手机和平板电脑充电。目前可容纳USB Type-C线缆的设备包括Apple的2015 MacBook,Google的Chromebook Pixel,诺基亚的N1平板电脑,OnePlus 2和Le Superphone等智能手机,以及LaCie和SanDisk的移动存储设备。

图1:USB Type-C引脚图。

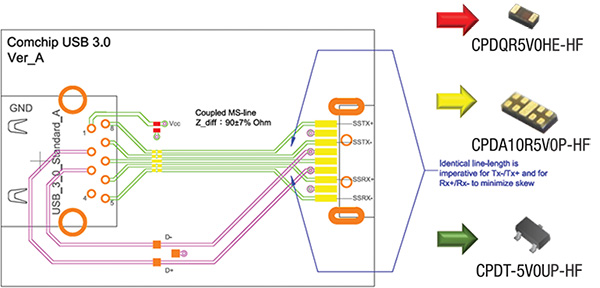

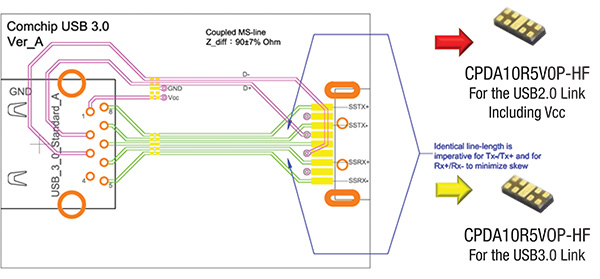

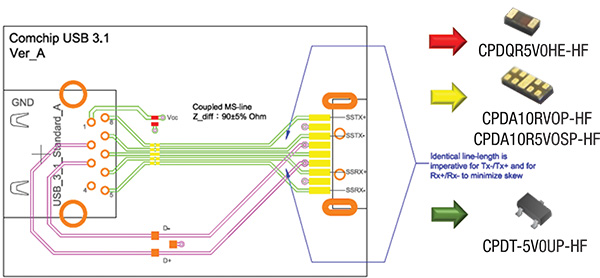

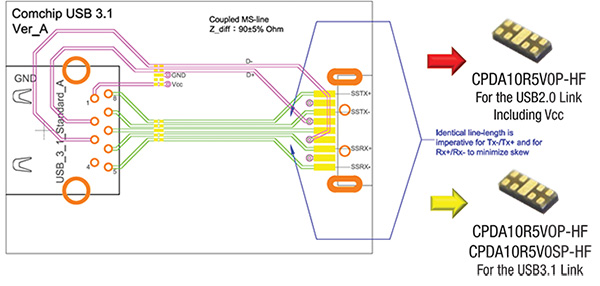

Comchip有许多低电容ESD浪涌抑制器,用于USB端口保护。 USB 3.0的推荐部件列于表2中,建议的PCB布局如图2和图3所示.USB 3.1的建议部件和布局如图4和图5所示.C型的推荐部件列于表3和表3中。建议的流通PCB布局如图6所示。

USB 2.0 D +,D-(USB 2.0和3.0数据线组合成一个)

部件号VRWM IR(Max)VC Cj ESD(接触)封装CPDQR5V0USP-HF 5 V1μA13V 0.6 pF±8 KV 0402

1-Line/Uni CPDQ5V0USP-HF 5 V1μA13V 0.6 pF±8 KV 0402

1-Line/Uni CPDQC5V0USP-HF 5 V1μA13V 0.6 pF±8 KV 0402C

1-Line/Uni CPDU5V0USP-HF 5 V1μA9.8V 0.5 pF±10 KV 0603

1-Line/Uni CPDUC5V0USP-HF 5 V1μA9.8V 0.5 pF±10 KV 0603C

1-Line/Uni CPDT-5V0UP-HF 5 V1μA12V 0.6 pF±10 KV SOT-23

2-Line/Uni

USB 3.0 Tx,Rx

部件号VRWM IR(最大值)VC Cj ESD(接触)封装CPDQC5V0CSP-HF 5 V 100 A 15 V 0.3 pF±8 KV 0402C

1-Line/Bi CPDQC5V0USP-IPHF 5 V 100 nA 12 V 0.3 pF±10 KV 0402C

1线/Uni CPDA10R5V0P-HF 5 V 50 nA 9 V 0.25 pF±18 KV DFN10P

4线/Uni

VBUS 5V

部件号VRWM IR(最大值)VC Cj ESD(联系方式)封装CPDQC5V0R-HF 5 V 90 nA 8 V 24 pF±30 KV 0402C

1-Line/Bi CPDUR5V0R-HF 5 V 90 nA 8 V 24 pF±30 KV 0603

1-Line/Bi CPDUC5V0R-HF 5 V 90 nA 8 V 24 pF±30 KV 0603C

1-Line/Bi CPDQR5V0HE-HF 5 V1μA11V 15 pF±30 KV 0402

1-Line/Bi CPDQC5V0HE-HF 5 V1μA 11 V 15 pF±30 KV 0402C

1-Line/Bi CPDUR5V0HE-HF 5 V1μA11V 15 pF±30 KV 0603

1-Line/Bi

表2:USB 3.0的推荐部件。

图2:USB 3.0建议使用三个组件的PCB布局图。

图3:USB 3.0建议使用两个组件的PCB布局图。

USB 3.1 A型具有与USB 3.0 A类似的ESD要求,所以建议的PCB布局是相同的,除了建议使用更低电容的ESD元件。建议的USB 3.1 PCB布局如图4和图5所示。

图4:USB 3.1建议使用三个组件的PCB布局图。

图5:USB 3.1建议使用两个组件的PCB布局图。

USB Type-C具有10 Gbit/s吞吐量,因此ESD考虑到额外电容和电感对高速差分对的潜在影响,保护至关重要。由于可逆连接器设计,USB Type-C具有更高的ESD保护要求。

在这种情况下,Comchip DFN10P封装的流通设计通过将封装置于高端来简化PCB布局高速差分对,避免复杂的过孔或环路,节省PCB空间。 USB Type-C的推荐部件列于表3中,建议的PCB布局如图6所示。

部件号VRWM IR(最大)VC Cj ESD(接触)封装CPDA10R5V0P-HF 5 V 50 nA 11 V 0.25 pF±14 KV DFN10P

4线/Bi CPDA10R5V0SP-HF 5 V 50 nA 12 V 0.15 pF±14 KV DFN10P

4线/Bi

表3:USB型推荐部件 - C。

图6:USB Type-C建议采用流通设计的PCB布局图。

-

USB 3.1助力USB Type-C高飞2016-01-20 4127

-

简析USB 3.1和Type-C的特点及联系2016-05-09 18597

-

USB3.1接口与Type-C有什么区别2016-01-13 6931

-

USB Type-C和USB 3.1如何区分与选择?2016-12-20 2573

-

如何对USB Type-C连接器进行ESD保护?2018-07-17 10606

-

Microchip首款支持Type-C™的车载USB 3.1 SmartHub,速率可提升10倍2019-02-27 7219

-

USB 3.1和Type-C是什么,他们有何关系2019-12-18 6435

-

USB Type-C连接器和电缆组件简介2022-04-27 13724

-

USB Type-C 多路复用USB 3.1 应用2022-07-27 7429

-

USB Type-C连接器的使用特点2023-05-23 8098

-

来咯!USB Type-A/B/C接口连接器产品知识介绍2021-12-24 5254

-

type-c和USB-c有什么区别 type-c和USB-c接口原理2023-09-01 38395

-

激光焊接技术在Type-C USB连接器的应用2025-03-19 914

-

USB Type-C连接器解决方案2025-05-19 1856

-

MCP22301 USB Type-C™ PD 3.1控制器技术解析与应用指南2025-09-30 743

全部0条评论

快来发表一下你的评论吧 !