SoC FPGA与MCU的优势对比,应如何选择

描述

MCU对应用优势的挑战已经开始。具有片上固定功能处理子系统(即片上系统(SoC)FPGA)的现场可编程逻辑器件(FPGA)最近已成为高端处理应用的潜在竞争者。这提出了一个问题:随着应用性能要求的不断提高,SoC FPGA将成为更广泛的应用中的挑战者,还是MCU会发展为更好地与SoC FPGA竞争?如果您正在考虑采用新设计,那么现在最适合您的方法是MCU还是SoC FPGA?

本文将快速回顾SoC FPGA与MCU相比的一些主要优缺点。它还将探讨最近的一些MCU创新,使其更加灵活,能够更好地应对SoC FPGA提供的一些关键优势。有了这些信息,您将能够在下一次设计中更好地在MCU和SoC FPGA之间进行选择。

SoC FPGA将新的灵活性与熟悉的处理系统相结合

SoC FPGA结合两个世界中更好的。对于初学者来说,SoC FPGA提供了一个熟悉的处理系统--CPU - 来执行熟悉的顺序处理算法。实际上,许多SoC FPGA已经融合在普适的ARM处理器架构上,构成了其“固定功能”处理子系统的基础。这充分利用了ARM兼容工具,知识产权核心(IP核)和支持技术的广泛生态系统,使开发成为一个非常熟悉的过程。

SoC FPGA还为顺序处理提供了灵活的可编程替代方案。可编程结构可以实现您所需的任何硬件功能,以增强处理子系统中的顺序处理能力。可编程结构本质上是并行的,因为多个硬件模块可以同时操作,或者在逻辑复制的情况下并行操作,或者以流水线方式操作,其中算法被分成多个阶段以便处理重叠。与顺序方法相比,这两种方法都可以产生巨大的吞吐量增益。

当可以使用并行或流水线技术在硬件中实现的算法的一部分需要高性能时,SoC FPGA特别有用(或组合)技术。让我们看一个示例器件,以便更好地了解它在实际系统中的工作原理。

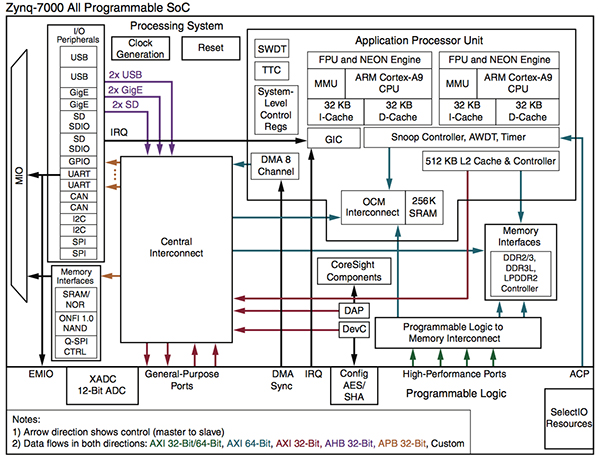

Xilinx Zynq-7000 SoC FPGA框图如下图1所示。该图的上半部分显示了芯片内包含的所有固定功能模块。这些模块实现了完整的双核ARM处理器应用处理单元以及大量支持互连总线,外设,存储器和片外接口。可编程逻辑部分显示在图的最底部,可通过各种系统级接口访问。该组织对SoC FPGA的可编程逻辑方面进行了新的改进,因为即使没有可编程逻辑,固定功能元件也可以工作。这意味着处理器系统可以“启动”然后配置可编程逻辑。以前的非SoC方法要求首先配置可编程逻辑,然后处理器才能启动。通过颠倒这个序列,可编程逻辑成为处理器的资源,并且可以更容易地与硬件开发并行地开发代码。

图1:Xilinx Zynq SoC FPGA框图。 (由赛灵思提供)

事实上,代码开发人员可以将SoC中的可编程逻辑视为一种硬件资源,用于加速在处理器上实现时速度过慢的代码段。一个设计团队成员可能将他们的活动集中在创建程序员请求的硬件加速上,或者程序员可能自己实现硬件。无论哪种方式,算法都成为可用的多种实现选项的开发重点。

当有多个面向性能的算法同时进行时,SoC方法似乎效果最好。 SoC FPGA取得巨大成功的一个应用领域是复杂的图像处理。这些算法通常可以流水线化和/或并行化,使其成为FPGA加速的理想选择。如果处理器还需要处理片上和片外的高带宽流量(可能具有高速串行接口和大型片外缓冲存储器),则从处理器卸载低级任务的额外硬件支持也可能需要支付大红利

对SoC FPGA的多核响应

还有其他方法可以为图像处理等应用实现并行和流水线实现。 MCU供应商采取的一种方法是在芯片上实现多个处理引擎(多核),以允许设计人员分解复杂的算法。当每个处理器的体系结构相同时,可以很容易地采用复杂的算法并将其分解为各自在不同但功能相同的处理器上执行的部分。

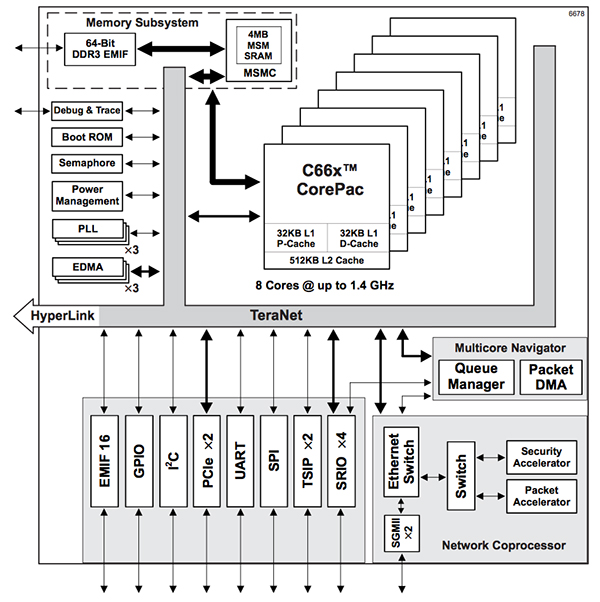

作为示例,德州仪器提供TMS320C66x多核固定和浮点数字信号处理器(DSP)具有8个DSP处理器以及网络协处理器和多核导航器,可简化使用硬件队列的数据传输(图2)。 DSP内核为各种复杂算法(如音频,视频,分析,工业自动化和媒体处理)提供极高的处理能力。

图2:德州仪器(TI)多核DSP框图。 (德州仪器公司提供)

多核架构的代码开发与使用SoC FPGA的代码开发有些类似,不同之处在于硬件加速是由DSP内核而不是可编程结构完成的。当一个核心无法足够快地实现算法时,只需将另一个核心放在其上即可。继续这样做,直到你用完核心或达到你的性能目标。可能需要进行调整和优化以获得最后的功耗/性能效率,但是一些更高级的工具可以通过提供有助于优化过程的性能和功耗配置文件来提供帮助。

双核MCU

多核方法不需要仅用于最高性能的应用。通常,SoC FPGA可以在性能较低的应用中找到,在这些应用中需要优化功耗和处理能力。由于可编程结构可用于实现部分算法,因此实现所需的总功率可能远远低于高端DSP或多核解决方案。

MCU制造商也发现了这一趋势,通过将双核处理器放在单个设备上进行响应。在某些情况下,使用高性能处理器和低性能处理器。这允许高性能处理器实现算法的更复杂部分和低性能处理器,以处理不太复杂的管理任务。较低性能的处理器可以在大多数时间处于活动状态,使用的功率低于高性能核心。 (请注意,多核系统可以使用类似的方法,只使用动态达到目标性能级别所需的核心数。这实现起来有点复杂,但如果算法需要,最终会非常有效各种性能水平在短时间内变化很大。)

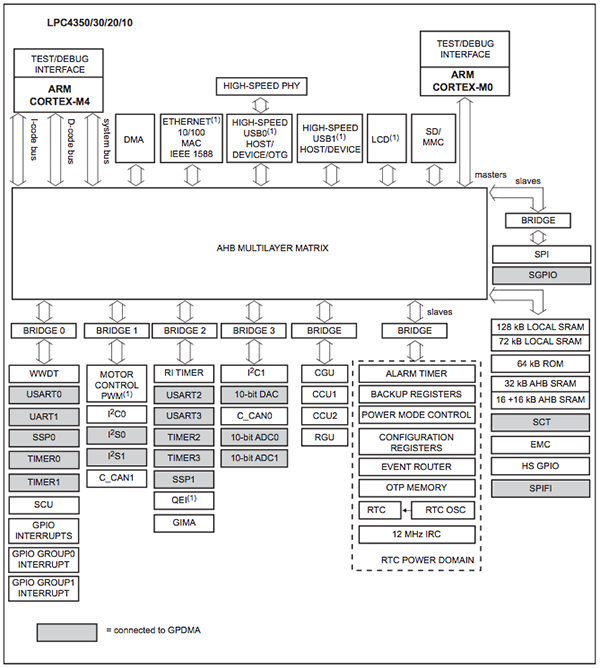

利用高性能和低性能处理器的双核MCU的一个例子是恩智浦半导体LPC4350 。如图3所示,它下面有一个ARM Cortex-M4和一个Cortex-M0。 M4用于高性能任务,而M0可用于通用管理功能。实际上,如果不需要M4子部分甚至可以断电,并且在处理请求需要时通电。这种方法适用于仅需要定期但需要快速响应处理数据的算法。作为一个例子,安全摄像机上的图像处理在图像变化时会非常沉重,但在图像静止时则不需要。

图3:恩智浦双核MCU框图。 (恩智浦提供)

即便是低端也是可编程的

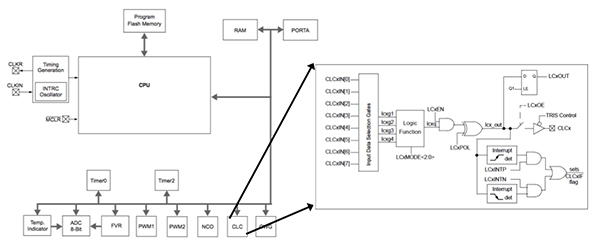

不要以为只有高端和中端MCU才能增加新的灵活性以提高灵活性。即使是低端MCU也在增加可编程功能,可能不是对SoC FPGA的响应,而是作为一种在可编程逻辑器件已经存在数十年的情况下“片上”拉出少量外部逻辑的方法。 Microchip PIC10F320增加了可编程逻辑,位于可配置逻辑单元(CLC)模块中。 PIC10F320的框图以及更详细的CLC视图如图4所示.CLC可以根据器件输入,内部时钟,内部外设和寄存器位实现各种简单的逻辑功能。 CLC甚至可以在低功耗模式下工作,使其成为唤醒事件的便捷来源,以便在不需要处理MCU时节省最大功率。

图4:具有可编程逻辑框图的Microchip MCU。 (由Microchip提供)

CLC在PIC10F320上特别有用,因为它只有几个引脚。充分利用这些引脚并消除一些外部逻辑可以对电路板空间要求产生很大影响。即使在PAL和CPLD的早期阶段,可编程逻辑提供的一大优势。现在,随着低端MCU将可编程逻辑放在芯片上,我们可能会看到更少的MCU旁边的低端PLD。这不是一个新的转折!

总之,MCU和SoC FPGA解决了类似的应用问题,并开始争夺应用优势。目前,挑战主要在应用领域的最高端,但最近的创新可能会扩大MCU与可编程设备之间的应用重叠。

-

SoC FPGA与MCU主要优势和劣势对比2022-08-03 6415

-

ARM、MCU、DSP、FPGA、SoC的区别是什么2021-12-09 7792

-

CPU/MCU/FPGA/SoC芯片异同点是什么2021-11-29 5380

-

arm/asic/dsp/fpga/mcu/soc的特点是什么?2021-11-11 1990

-

FPGA相对于MCU的主要优势在哪2021-11-08 9454

-

CPU/MCU/FPGA/SoC芯片的区别2021-11-01 4034

-

DSP/MCU/ARM/CPLD/FPGA对比分析哪个好?2021-10-22 1694

-

与传统模式的芯片设计进行对比FPGA芯片有哪些优势2021-09-14 1625

-

ARM、MCU、DSP、FPGA、SOC该怎么选择?资料下载2021-04-18 1079

-

对于eFPGA与FPGA SoC之间的对比分析和异同2019-09-04 5058

-

SoC FPGA有哪些作用?2019-08-26 3202

-

MCU和SoC的FPGA?这是您的应用程序的最佳解决方案吗?2017-05-17 877

-

ARM、MCU、DSP、FPGA、SOC各是什么?区别是什么?2017-04-13 3587

-

ASIC和FPGA的优势与劣势2011-03-31 6067

全部0条评论

快来发表一下你的评论吧 !