如何为嵌入式系统选择最低功耗的微控制器

描述

设计低功耗MCU并不容易,也没有为您的特定嵌入式设计选择合适的MCU。许多特定于应用的注意事项都会起到作用,这使得比较MCU规格表具有挑战性。本文分析了在分析竞争性MCU替代品的电源效率时应考虑的关键因素。节约能源有利于环境,更容易在钱包上使用。提高能效的无数好处已被充分证明:降低消费者的电费,降低公用事业的负担,降低电子产品的拥有成本,减少垃圾填埋场丢弃的废旧电池。

随着电子设备的使用渗透几乎我们生活的每个方面,降低功耗必须从半导体层面开始。在芯片级设计的节能技术具有深远的影响。对于作为当今大多数电子设备背后的智能引擎的微控制器(MCU)而言尤其如此。从系统架构的角度来看,确定哪些MCU真正“低功耗”的挑战需要设计人员浏览各种半导体供应商提出的无数要求。由于供应商使用的指标不同(通常是令人困惑的),这不是一项简单的任务。

让我们仔细研究在分析竞争性MCU备选方案的功效时应考虑的关键因素。

在基本级别,MCU功耗可以定义为以下总和:

总功耗=活动模式功率+待机(休眠)模式功率

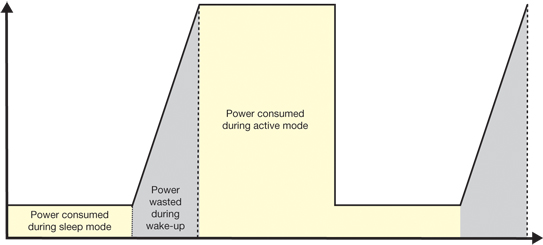

但是,要记住的另一个重要指标是MCU从待机状态转换到活动状态所需的时间。由于MCU在所有数字和模拟组件完全稳定且可操作之前无法进行任何有用的处理,因此在计算总功耗时添加此(浪费)功率非常重要:

总功耗=活动模式功率+待机(睡眠)模式电源+唤醒功率

图1.

由于每个应用程序都不同,系统设计人员倾向于比其他应用程序更重视这些元素。例如,某些应用,例如水表,大部分时间都处于待机状态,因此很明显,它们的长占空比需要非常低的待机功耗。其他应用程序(如数据记录器)经常进入和退出活动状态,因此限制唤醒转换模式所花费的时间至关重要。然而,开发引人注目的MCU解决方案的供应商不会试图猜测这些指标中哪一个是最重要的,而是将从头开始设计一个解决方案,专注于最小化该等式的每个部分。要实现这一目标,需要强大的混合信号专业知识,以解决在模拟和数字域中最小化功耗所必需的架构级和电路级挑战。对这些变量进行简短讨论将有助于突出系统设计人员在尝试为其应用选择最佳MCU解决方案时需要注意的问题类型。

Active Mode Current

对于CMOS逻辑门,动态功耗可以使用以下众所周知的公式重写:

有源模式功率= C x V2 xf

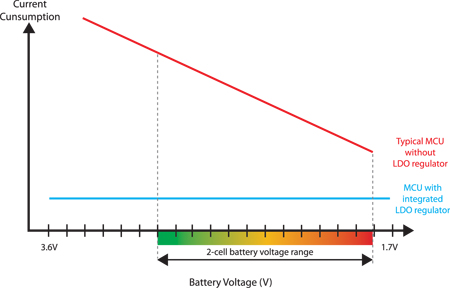

其中C是负载电容,V是电源电压,f是开关频率。 BR》电容项是所用设计和处理技术的函数,频率项是应用程序处理要求的函数。但是,如前面的等式所示,电源电压对MCU消耗的总功率有不成比例的影响。因此,通过向MCU电路提供低得多的稳定电源电压,为MCU设计增加电压调节可以显着节省功耗模式。开关型转换器可能是一种可能的解决方案,但它们最适合需要大电压转换比的稳压器环境。但是,对于平均电压转换率较小(电池寿命结束时接近1:1)的电池类应用,更好的解决方案是添加片上低压差(LDO)线性稳压器因为它可以提供可接受的效率,而且复杂性和成本低于开关解决方案。为了说明使用LDO稳压器的好处,重新阐述CMOS动态功率公式是有帮助的:

有源模式功率= C x V2 xf

= V x(C x V xf)

= V x I,其中动态电流I = C x V xf

通常将动态电流归一化为1MHz的频率和特定的电源电压。例如,最近推出的一款超低功耗MCU在1.8 V时的动态电流消耗为每MHz160μA。如果没有电源调节,该指标将增加到(160)x(3.2/1.8)=284μA/MHz时电源电压为3.2 V.使用LDO时,电池电流将在整个电源范围内保持固定为每MHz160μA。

可以看出,这种先进的电源架构可用于维持恒定的有功电流完整的工作电压范围,可以帮助系统设计人员大幅节省功耗。因此,从系统设计人员的角度来看,确定在整个工作电压范围内工作时的MCU电流消耗非常重要 - 而不仅仅是MCU供应商通常引用的1.8 V最低工作条件。引用一个过于乐观的电流数字,假设任何低于典型的电压供应,并不能准确反映应用在现实世界中的使用方式。例如,在2 x AA/AAA和纽扣电池应用中,电池最常接近3 V初始电压工作,因此引用的1.8 V规格可能是欺骗性的,因为从这个角度来看,大多数MCU都会消耗掉功耗比通常引用的功率多50%。

图2.

此外,由于功耗与开关频率成正比,因此系统设计人员必须将引用的电流数归一化到电流/MHz。通过结合这两个因素,可以根据以下指标对MCU进行并排比较:

电流消耗/MHz @ 3 V

当真正有意义的值是指令时钟速度时,一些供应商会试图通过将“MHz”等同于系统时钟速度来混淆问题。这是欺骗性的,因为系统时钟速度可以以其实际指令速度的两倍(或更多)运行,从而使其有效功耗加倍(或更多)。因此,确保所有内容都符合指令时钟速度是很重要的。通过这样做,并通过使用典型的电源电压,可以正确地推导出实际的有源模式电流消耗预算。

待机(休眠)电流

实现最大能效(和电池寿命)转化为确保每个MCU任务在尽可能短的时间内以最小可能电压消耗最小可能电流,以便器件将大部分时间用于非常低功耗的睡眠模式。在一些应用中,睡眠模式电流是对整体能量消耗负有最大责任的参数。然而,经常被忽视的是MCU可实现的绝对最小睡眠电流主要受其漏电流的限制。例如,输入泄漏电流规格为100 nA的20输入设备在睡眠模式下可能消耗高达2μA的功率。

泄漏电流受多种因素的影响,但最重要的因素是使用的基础流程技术。在某些情况下,供应商会选择使用0.25或0.35微米工艺技术来降低由泄漏引起的睡眠电流,但这种选择是以更高的有功电流为代价的。在其他情况下,MCU供应商选择使用0.18微米或更小的工艺技术来降低有源模式电流,但这是以更高漏电流为代价的。围绕这一难题的独特解决方案是应用混合信号专业知识来实施先进的电源管理单元(PMU),专门用于限制泄漏并实现超低睡眠电流,无论使用何种基础工艺技术。使用0.25微米或更小的工艺技术,最小化睡眠模式电流需要削减数字核心的功率。在睡眠模式下工作的模块,如电源管理电路,I/O焊盘单元和RTC,必须使用未调节的电源工作,以避免在LDO中烧毁额外的电流。切断数字核心逻辑的电源也可以防止其断态泄漏对睡眠模式电流产生影响;但是,MCU必须在休眠模式下保留RAM内容和所有寄存器的状态,以便代码执行可以从中断处继续。这种保存可以通过一些非常低电流,睡眠模式,锁存偏置方案或通过使用特殊的保持锁存器来执行,该保持锁存器可以将状态保持在睡眠模式而没有显着的泄漏。 MCU还需要某种形式的连续电源电压监控(即“掉电检测”),以便在电源电压低于最小保持电压的情况下复位器件,这可能会破坏状态。

从系统设计人员的角度来看因此,重要的是要检查潜在的漏电流规范,以确定哪些MCU供应商已经应用其混合信号专业知识来解决这一复杂问题。设计人员还应该考虑大多数供应商提供许多不同的待机电流选项的事实。大多数供应商将突出显示其绝对最低睡眠模式电流,这通常对应于实时时钟消耗的电流和禁用掉电检测器。一些供应商会更进一步,并引用关闭模式电流,该电流不会保留存储器并需要复位才能唤醒,这通常不是一个非常实用的模式。因此,由于大多数应用程序都需要完整的RAM和寄存器保留,因此系统设计人员必须根据以下指标进行并排比较:

待机/睡眠模式电流与实时时钟和掉电禁用(具有RAM保持)

待机/睡眠模式电流,实时时钟禁用和掉电启用

待机/睡眠模式电流与实时时钟然后,系统设计人员可以根据应用程序的占空比计算总体待机模式功率预算时使用正确的值。

唤醒能量

如前所述,在使用睡眠模式的系统中,可能会浪费大量功率来唤醒MCU并准备采集或处理数据。实际上,在某些应用中,MCU在退出待机状态时通常会使用与设备完全处理数据时一样多的能量。因此,设计一个MCU以在极短的时间内唤醒和稳定非常重要,以便最大限度地减少在能量浪费状态下花费的时间。

MCU应该能够退出睡眠模式来自外部触发事件或内部计时器。最灵活的周期性唤醒源是一个实时时钟,能够从外部晶体振荡器(用于需要精确定时的应用)或低频内部振荡器运行,无需在低精度应用中使用晶体。避免使用慢启动晶体振荡器作为高速系统时钟;一个准确的,快速启动的片上振荡器是更好的选择。

此外,由于许多产品定期唤醒以使用片上ADC对输入进行采样,因此为数字电路提供足够的时间非常重要唤醒和模拟电路稳定开始进行有效测量。模拟模块的启动行为会对在活动模式下花费的时间量产生重大影响;使用外部去耦电容的稳压器或基准电压源可能需要几毫秒才能稳定下来。有时,MCU供应商只会引用数字电路的唤醒时间,而忽略了模拟电路稳定所需的时间。因此,系统设计人员必须分析数字和模拟电路的整体唤醒和建立时间,以分析这种浪费能源的真实成本。

其他注意事项

当然还有其他注意事项进一步降低系统功耗的方法。例如,通常使用2 x AA/AAA电池配置,因为MCU通常通常可以在低至1.8 V的电压下运行,有时只能降低功能(无ADC;降低指令时钟速度)。降低功耗(和环境影响)的创新方法是将设计转换为单个电池配置,其中电池可以一直运行直至其使用寿命(0.9 V)。为实现这一目标,MCU必须集成高度优化的DC-DC转换器,该转换器可以在电池的最低可用电压下工作,在碱性化学情况下为0.9 V.这种方法还可以节省供应商和/或降低功耗的另一种方法是使用高度集成的MCU,包括ADC,DAC和其他外设,因为MCU可以根据应用的需要控制启用和禁用这些外设。例如,某些MCU提供具有突发模式的专用低功耗ADC,可在CPU关闭时进行模拟测量,以进一步降低功耗。

-

STM32U575/585微控制器的超低功耗特点2022-07-29 3400

-

如何为嵌入式应用选择合适的微控制器2018-12-21 2430

-

基于微控制器的选择解读超低功耗意义2019-07-22 1897

-

超低功耗C8051F91x/0x微控制器的功能2019-07-29 2706

-

选择低功耗微控制器开发,避免资源受限规则2019-12-27 3156

-

微控制器功耗管理模式:降低功耗的方式2020-02-06 5599

-

STM32L5超低功耗微控制器2020-06-30 1529

-

基于微控制器的现代嵌入式系统2021-07-30 1099

-

什么是微控制器MCU2022-10-29 14193

-

时间触发嵌入式系统设计模式(使用8051微控制器开发可靠应用2008-10-28 3142

-

基于M CORE微控制器的嵌入式系统2009-10-09 798

-

Silicon Labs推出业界最低功耗微控制器系列2009-12-15 1624

-

什么是低功耗微控制器?2017-07-24 991

-

低功耗设计基础:如何为嵌入式系统选择最佳低功耗MCU2017-08-04 928

-

如何为STM32WB系列微控制器构建蓝牙®低功耗网状网络应用2022-11-21 519

全部0条评论

快来发表一下你的评论吧 !