上电顺序知多少?论上电顺序的重要性

电子说

描述

工作中第一次感受到上电顺序的重要性还是在罗礼电脑,我那个时候还是一名PE,也就是产品工程师,负责产线的制程分析改善和不良品维修。有一天早上,刚刚到办公室,生产线就发生了紧急事件,有一个测试工位连续烧了三块主板,这可不得了,那个年代一块Intel-440BX的主板要买1300块,我那时一个月工资也才1300块啊。

Figure 1 被烧毁的南桥芯片

我把三块烧毁的板子拿过来分析,发现三块板子的南桥芯片也就是上图中的82371芯片都有明显的被烧焦的痕迹,芯片表面烧的面目全非,看着有点毛骨悚然,当时的照片我没有拍下来(那时候没有智能手机^_^),但是情形和图2基本一样。

Figure 2 芯片的烧毁痕迹

排查这类问题的过程其实和警察查案子类似,我们也查“人证”和“物证”:

01先“查人”

三块板子烧毁都是在同一个测试工位,也就是说由同一个测试人员产生,其他相同的测试工位没有发生这样的事件,我们发现此站工位的作业员比较瘦小,每次插拔ATX Power Cable时,由于胳膊力气小,需要左右两边连续做上下晃动,才能拔出或插入,有点像是利用省力杠杆的原理,而其它工位的作业员则是直接一次性垂直上下插入和拔出。

Figure 3 ATX 电源连接器

02再“查物”

也就是芯片,三块板子烧毁的芯片位置都是南桥芯片。我们从南桥芯片82371的Datasheet里面获得了上电顺序的要求:

“

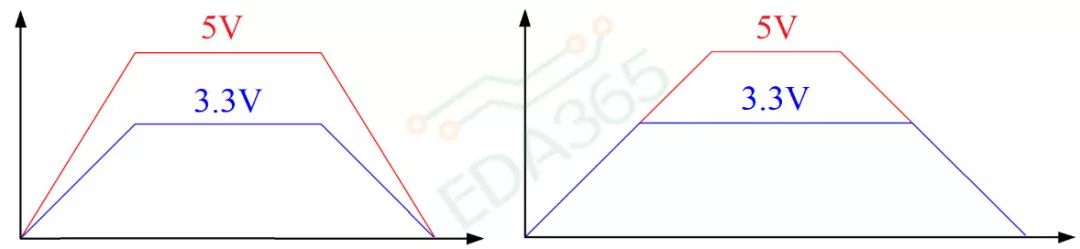

1) 上电 – 5V要比3.3V先上电,或者二者同时

2) 下电 – 5V要比3.3V后掉电,或者二者同时

Figure 4 82371上电和下电顺序要求

原因分析:

此工位的作业员在插拔ATX电源的时候,由于胳膊的左右晃动造成南桥芯片的上电/下电顺序被破坏,导致烧毁。我们更换了作业员,并且进行作业指导培训后就再也没有出现过芯片烧毁的情况。

虽然我们没有做过实际的测试,但是很多大牛的文章里面都在描述,芯片的上电顺序不满足的话比较危险,要么发生即时故障,要么影响芯片的长期稳定性,我们来列举几个可能发生的情况:

01

Bus contention

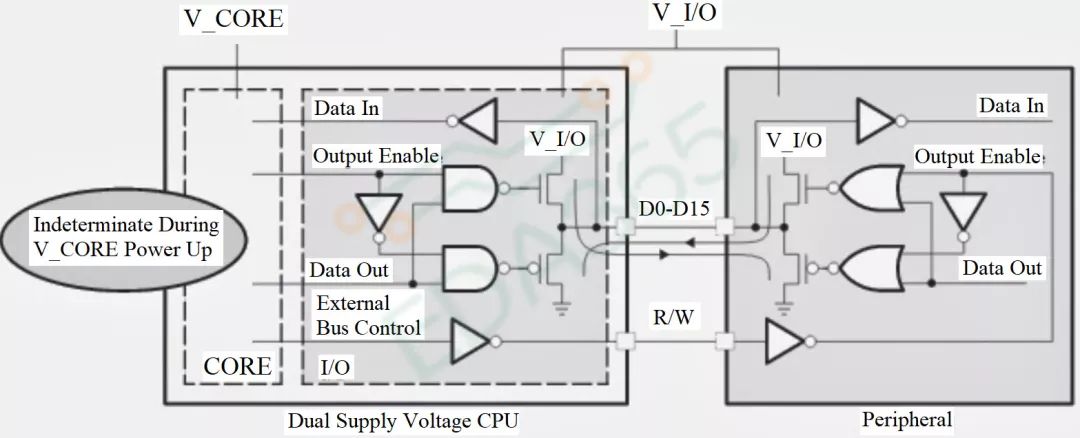

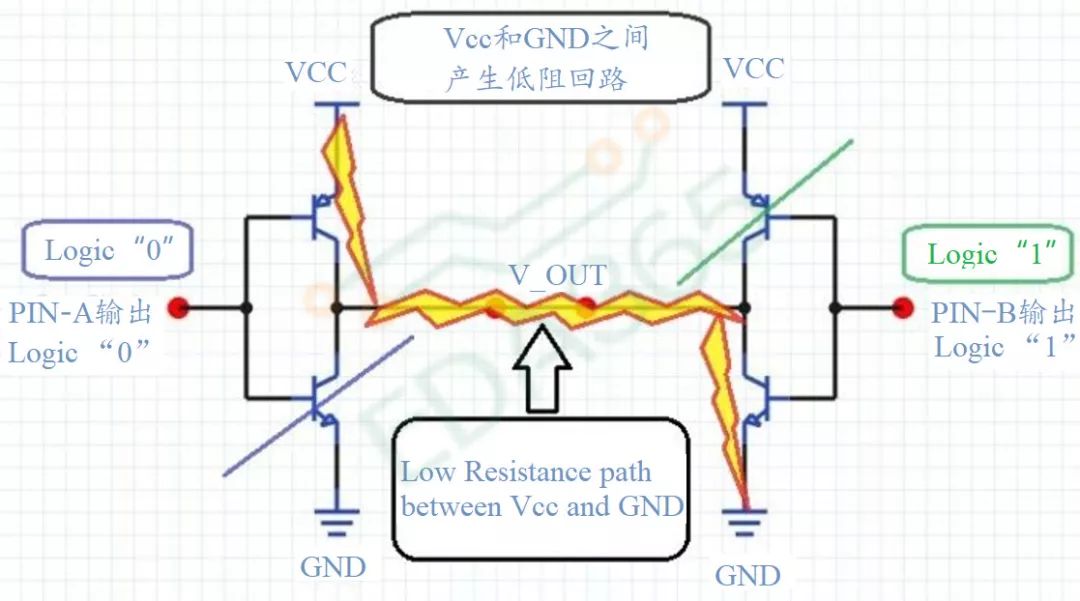

如图5所示,左边的CPU有两路电源,即V_CORE和V_IO,右边的芯片和CPU共用V_IO,两颗芯片之间通过双向数据总线接口相连,也就是所谓的“Bidirectional Data bus”,在这个系统里面,我们需要V_CORE先上电,然后V_I/O再上电,否则的话很容易出现CPU和I/O同时往数据线上发送数据,产生图6的情况,此时我们看到在VCC和GND之间产生了一个低阻回路,很容易损坏甚至烧毁芯片。

Figure 5 系统有一颗双电源的芯片

Figure 6 Bus Contention产生的低阻回路

需要提一下,图5的上电顺序(先V_CORE-后V_IO)不是绝对的,有的CPU要求先V_IO后V_CORE,根据接口类型,工艺,设计厂家的不同,上电/下电顺序要求也不一样。

02

Latch-up

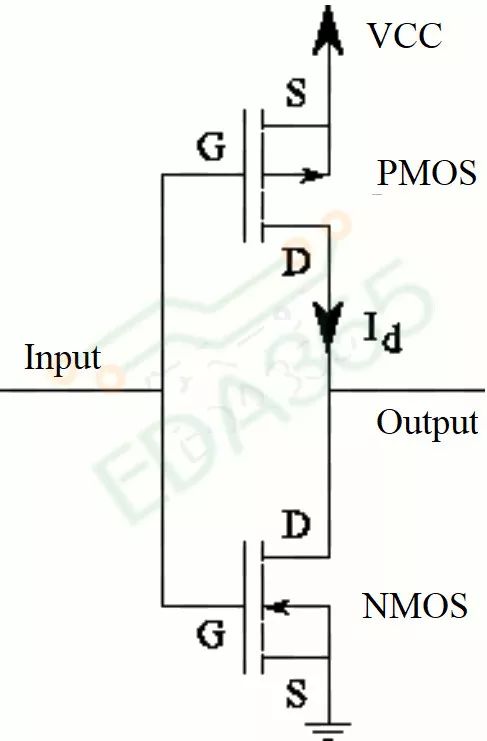

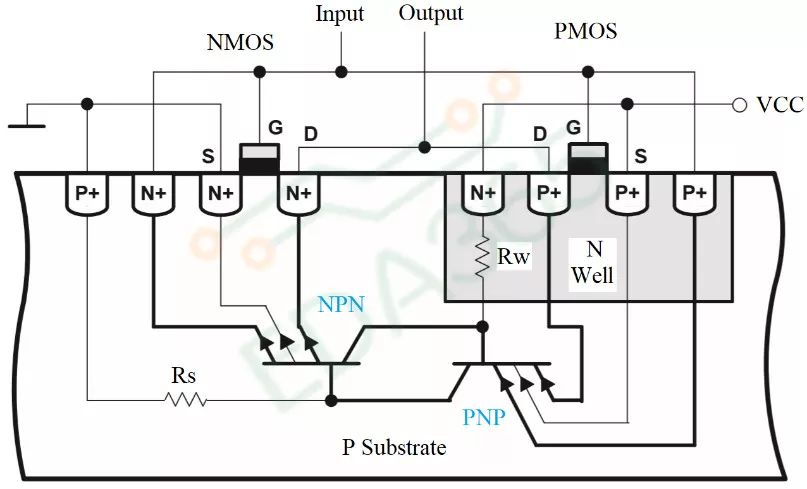

Latch-up的中文名叫闩锁,有很多文章也都提及这个概念,我们先来简单描述一下CMOS电路的常用一个基本电路单元如下图(a),(b)图是相对应的芯片物理连接。

(a)

(b)

Figure 7 Latch up示意图

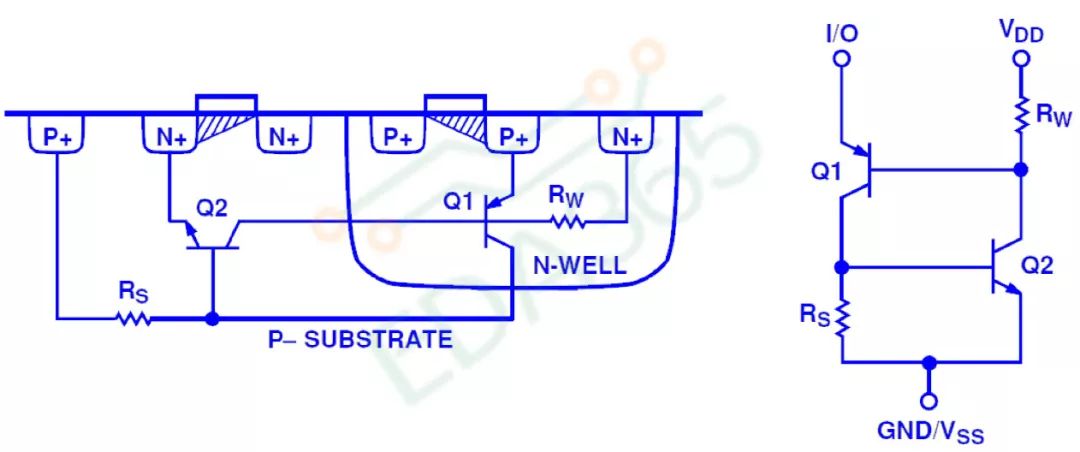

我们发现多了两个器件,也就是我们看到的NPN和PNP, 它们是怎么形成的呢?我们从图中看到是来自不同的MOSFET的P和N之形成了杂散的PNP和NPN,我们把这些管子叫做SCR ( Silicon-Controlled Rectifier ), 为了更加清楚的描述SCR,我们用另外一张简图来表示:

Figure 8 SCR

根据图8,我们看到SCR是一个带有正反馈的不稳定结构,正常情况下SCR是不导通激活的,但是凡事都有例外,我们来看看如果下面这种情况:

“

1) Q2的Base上面有正向外部电流扰动注入,Q2导通;

2) Q2导通,使得Q1的Base电压降低,促进Q1导通;

3) Q1导通,使得Q2的Base电压抬高,Q2进一步导通;

4) Q1和Q2都进入饱和导通状态,电源和地低阻建立。

案例总结:

随着芯片的集成度越来越高,所需要的电压种类也越多,对上电顺序的需求也越来越复杂,我们在设计时需要仔细阅读Datasheet里面的关于Power sequence的需求,这样设计出来的产品才能更加稳定,有时候我们有侥幸心理,觉得上电顺序无关紧要,事实上运气好在研发阶段可能确实不会有什么问题,但是到了后期量产和交付客户使用,会发生什么事情就不可控了,尤其是消费电子产品,林子大了什么鸟都有啊。

-

DAC828的上电顺序错了会怎么样?2025-02-10 308

-

请问不按照手册中的上电顺序ADS1274能正常工作吗?2025-01-16 297

-

ADS1278怎么设计上电顺序的电路啊?2025-01-15 352

-

DAC7731如何实现这个上电顺序呢?2024-11-27 254

-

为什么要测试芯片上下电功能?芯片上电和下电功能测试的重要性2023-11-10 2838

-

如何控制FPGA各电源的上电顺序呢?2023-03-27 3522

-

s5pv210上电顺序是怎么控制的2022-07-20 2428

-

Zynq的电源上电顺序2020-01-01 13907

-

STHV748上电和断电电压顺序是什么?2019-08-13 1427

-

请问ADSP-BF522的外围内核上电顺序是什么2019-03-08 1716

-

请问AD9243上电顺序有什么要求吗2018-11-05 2211

-

请教关于C6678上电顺序问题2018-08-07 2410

-

Altera FPGA的上电顺序2017-05-18 7944

全部0条评论

快来发表一下你的评论吧 !