如何在考虑信号完整性的情况下进行高速的PCB设计

EMC/EMI设计

描述

引言

信号完整性是指电路系统中信号的质量。如果在要求的时间内,信号能够不失真地从源端传送到接收端,就称该信号是完整的。随着半导体工艺的迅猛发展、IC开关输出速度的提高,信号完整性问题(包括信号过冲与下冲、振铃、反射、串扰、地弹等)已成为高速PCB设计必须关注的问题之一。通常,数字逻辑电路的频率达到或超过50 MHz,而且工作在这个频率上的电路占整个系统的1/3以上,就可以称其为高速电路。实际上,与信号本身的频率相比,信号边沿的谐波频率更高,信号快速变化的跳变(上升沿与下降沿)引发了信号传输的非预期效果。这也是信号完整性问题的根源所在。因此,如何在高速PCB设计过程中充分考虑信号完整性因素,并采取有效的控制措施,提高电路设计质量,是必须考虑的问题。

借助功能强大的Cadence公司SPEECTRAQuest仿真软件,利用IBIS模型,对高速信号进行信号完整性仿真分析是一种高效可行的分析方法,可以发现信号完整性问题,根据仿真结果在信号完整性相关问题上做出优化的设计,从而达到提高设计质量,缩短设计周期的目的。

1 应用设计实例

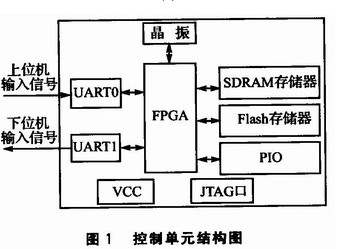

本文设计的控制单元在整个系统中的功能是将地面接收装置接收到的编码信号传回给主站数据处理中心。具体工作过程是,首先存储上位机数据,然后通过误码率测试与计算,选择一条误码率最低的路径作为数据传输路径,最后将存储的上位机数据通过该路径传输到主站数据处理中心进行处理。经过综合考虑,选用了Altera公司的Cyclone II-2C8作为核心芯片,以及外部扩展的SDRAM、Flash、各种输入/输出电路和MAX232接口芯片等,并结合Nios II软核处理器开发套件实现。该控制单元结构如图1所示。

CycloneII-2C8的时钟频率高达150 MHz以上,由于FPGA内部数据存储区比较小,所以用SDRAM扩展了外部数据存储空间。SDRAM采用了Hy-nix公司的HY57V651610/SO,时钟频率达到75 MHz以上。因此,必须考虑由于信号频率过高引起的信号完整性问题。选择了功能强大的Cad-ence设计软件,它将原理图设计、PCB Layout、高速仿真分析集于一体,可以解决在设计的各个环节中所存在的与电气性能相关的问题,大大提高了设计的成功率。

2 关键信号拓扑结构和仿真

此系统中频率较高的部分为FPGA和SDRAM,FPGA的时钟频率可达150 MHz以上,SDRAM可达75MHz以上。因为FPGA的内部高频对其他器件没有影响,而FPGA与SDRAM之间的连接为无缝连接,信号完整性的好坏直接影响着FPGA能否对SDRAM进行正确的读和写。PCB设计中,采用Cadence软件的高速仿真工具SPECCTRAQuest,并利用器件的 IBIS模型来分析信号完整性,对阻抗匹配以及拓扑结构进行优化设计,以保证系统正常工作。本文只对信号反射和串扰进行详细的讲解,其他仿真与此类似。

2.1 反射

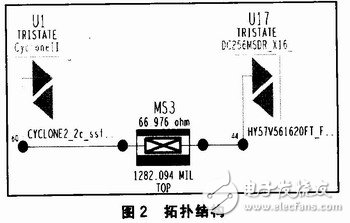

发射端为HY57V561620的44引脚,接收端为Cyclone II的60引脚,激励为66 MHz的方波。图2为拓扑结构,图3为仿真波形。

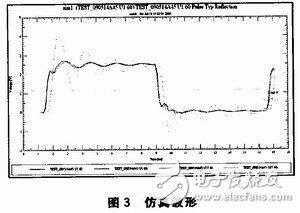

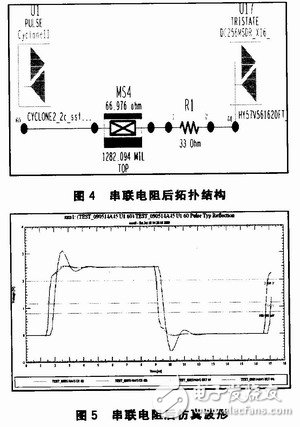

由仿真波形可以看出,由信号反射引起了波形畸变,产生了明显的振铃现象。振铃现象的存在,使信号多次跨越电平逻辑门限从而导致逻辑功能紊乱。减小振铃噪声的一种有效手段是在电路中串联一个小电阻,该电阻为电路提供了阻尼,能显著减小振铃幅度,缩短振铃震荡时间,同时几乎不影响电路速度。在工程使用上,该电阻通常为33 Ω。串联电阻后的拓扑结构和仿真波形如图4和图5所示。

串联电阻后振铃现象得到了很好的解决,实际上这个解决方法叫阻抗匹配,阻抗在信号完整性问题中占据着极其重要的地位。

2.2 串扰

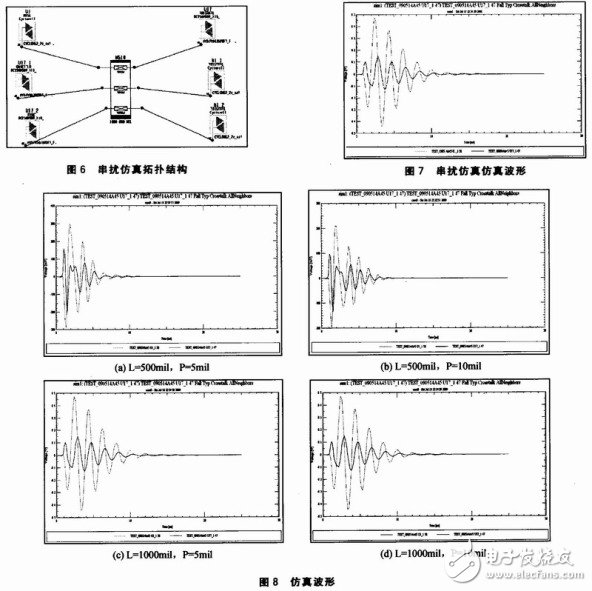

提取SD_DQlO(连接Cyclone II的59引脚和HY57V561620的45引脚),SD_DQll(连接Cyclone II的58引脚和HY57V561620的47引脚),SD_DQ-l2(连接CycloneII的57引脚和HY57V561620的48引脚)这三个网络来做它们之间的串扰仿真。其中,SD_DQll作为被攻击网络,SD_DQlO和SD_D-Ql2作为攻击网络。它们的拓扑结构和仿真波形如图6、图 7所示(传输线的并行耦合长度L=1000 mil,间距P=5 mil)。

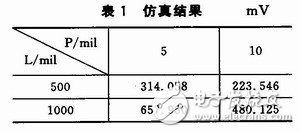

仿真波形如图8所示。由图7可以看出串扰对于被攻击网络的影响还是很大的,串扰值Crosstalk=657.95 mV串扰的大小与传输线的并行耦合长度L和间距P有关,耦合长度越短,间距越大,串扰就越小。仿真结果如表1所列。

因此,制作PCB时,在允许的情况下要尽可能减小不同性质信号线之间的并行长度,加宽它们之间的间距,改变某些线的线宽和高度。当然,影响串扰的因素还有许多,比如电流流向、干扰源信号频率上升时间等,应综合考虑。

结语

在本次控制单元高速PCB设计中,运用功能强大的Cadence软件,从制作原理图、PCB布局到高速仿真分析,取得了较好的效果。依据 SPEECTRAQuest仿真分析所得到的合理的拓扑结构和布局布线,使电路板工作正常。这种设计方式大大缩短了硬件调试时间,提高了工作效率,节约了设计成本。

- 相关推荐

- 热点推荐

- PCB设计

-

分析高速数字PCB设计信号完整性解决方法2024-01-11 1291

-

高速电路信号完整性分析与设计—PCB设计12022-02-10 1190

-

PCB设计中要考虑电源信号的完整性吗2021-12-27 1294

-

如何解决高速数字PCB设计信号完整性的问题?2021-03-29 1893

-

基于信号完整性的高速PCB设计流程解析2019-10-11 2498

-

[经验] 如何在考虑信号完整性的情况下进行高速的PCB设计?2019-09-25 2245

-

如何在考虑信号完整性的情况下进行高速的PCB设计?2019-09-16 4552

-

基于信号完整性分析的高速数字PCB板的设计开发2018-08-29 2062

-

PCB信号完整性有哪几步_如何确保PCB设计信号完整性2018-05-23 11751

-

基于信号完整性分析的PCB设计解析2017-12-04 1767

-

高速PCB电路板的信号完整性设计2017-11-08 1535

-

基于信号完整性分析的高速PCB设计2015-01-07 2673

-

高速PCB设计的信号完整性问题2012-10-17 3189

-

基于信号完整性分析的高速数字PCB的设计方法2008-06-14 5799

全部0条评论

快来发表一下你的评论吧 !