单片机p0口的工作原理解析

控制/MCU

描述

学习ARM嵌入式的时候,发现自己对以前学过的数模器件的知识遗忘了不少,按照我的进度本来应该继续学习ARM微处理器控制的课程,但想着后来势必还会遇到相同的问题所以就准备中断一下,杀回来把汇编和一些电路知识再总结一下,查漏补缺。如果有写的不合理的地方,还请多多指教。

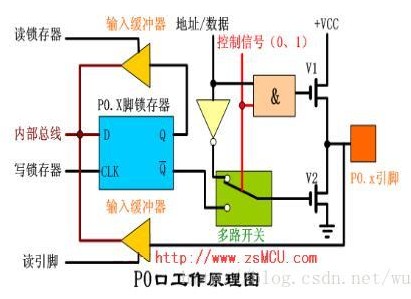

言归正传,先来一幅图片来引入今天要讲述的三个知识点:

锁存器(由一个D触发器构成)

D:数据输入端;

CP/CLK:时序信号输入端;

Q:输出端;

~Q:反向输出端;

工作原理:

当D端输入数据信号,CP/CLK端没有时序信号时,Q和~Q端将不会有信号输出;

当D端输入数据信号,CP/CLK端有时序信号时,Q和~Q端有信号输出;

当D端和CP/CLK端同时有信号输入后突然撤掉CP/CLK信号时,D的值将会被保存到(“锁”)在器件内,此时Q和~Q端并没有信号输出,等下一个时序再次输入到CP/CLK端,Q和~Q将会正常输出D端传送的信号;

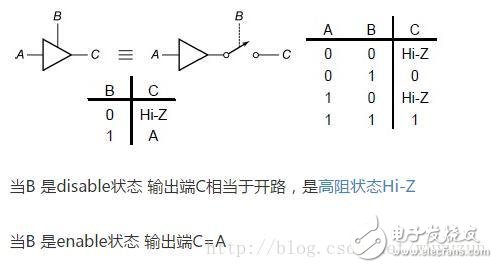

三态缓冲器(三态门)

三态:输出端的高电平,低电平,高阻态;

这里小哥偷个懒,百度一哥们儿给的解释,图文并茂想必更加清晰;

这里给各位初学者提个醒:连个三态缓冲器的输出端并不是说输出到了锁存器的D端借口上,而是输出到了单片机内部总线上,至于怎么传的那是后话;

输出驱动器

看图可知管脚的输出是靠两个MOS组成的推挽式结构,而且两个MOS管一次只能导通一个;

多路开关

首先,P0管口是复用管口,由于多路开关的存在是的P0口既可以用作普通I/O口,也可以用作外部拓展时传输数据和地址信号的总线功能;

P0口做低八位地址总线和数据总线,P2做高八位地址总线;

这里解释一下:不同的单片机结构不同,比如8031系列单片机内部没有程序储存器ROM,这就是的必须外置ROM,这是就必须牺牲管脚去外接ROM;

-

单片机P0口的片外数据存储器扩展设计技巧2013-10-11 5702

-

51单片机的P0口的工作原理2011-02-24 10561

-

单片机P0口2014-07-17 3436

-

P0端口的结构及工作原理2021-02-04 2494

-

MCS-51单片机P0口扩展技术研究2009-03-18 1715

-

p0口为什么接上拉电阻2018-08-22 57429

-

51单片机P0口的特性及使用方法解析2018-12-14 40356

-

51单片机的P0和P1、P2、P3的区别与IO口直接输入输出实例详细说明2019-09-19 27144

-

51单片机P0口的工作原理和分时复用的详细讲解2019-09-03 5388

-

单片机P0口的AD0-7到底是什么意思2019-07-11 3138

-

51单片机的P0口驱动能力到底怎么样详细总结说明2019-10-10 4629

-

51单片机对P0口为什么要加上上拉电阻2020-12-08 10641

-

单片机 P0口、P1口 寄存器和引脚的不同2021-12-01 1712

-

单片机p0口的工作原理解析2022-02-10 511

-

51单片机P0口该不该接上拉电阻2022-10-11 6113

全部0条评论

快来发表一下你的评论吧 !