如何实现AD芯片和高速FIFO存储器以及MCU之间的接口电路

接口/总线/驱动

描述

1.引言

在高速数据采集系统中,AD芯片的工作速度通常是很高的,可以达到几兆甚至几十兆,而微控制器MCU的工作速度相对较低,并且其往往具有多个任务,所以不能采用AD转换一次MCU读取一次数据的工作方式。因此,需要在AD芯片与MCU之间加入数据缓冲器,以便临时存储AD转换的数据,当数据量到达一定深度后,再由MCU一并取走。数据缓冲器可以有多种选择,例如RAM、SRAM等等,而FIFO(First In First Out)存储器凭借其操作简单、可靠性好等特点,被广泛的应用于数据采集系统中,成为了连接MCU与AD芯片的桥梁。

为了使MCU、AD芯片以及高速FIFO存储器能够协调工作,就需要设计好这三者之间的接口电路。本文正是针对这个问题,选用CPLD实现了三者之间的接口电路。

2.芯片介绍

2.1 模数转换芯片ADS8323

ADS8323是TI公司近年推出的一款高性能模数转换芯片,其主要特点如下:

(1)高速高精度:16位的AD芯片,其最高采样速率可达500kSPS;

(2)低功耗:当处于500kSPS的采样率时,其功耗也只有85mW;

(3)并行接口设计:它可以一次性将16位采样结果输出,也可8位分两次输出。

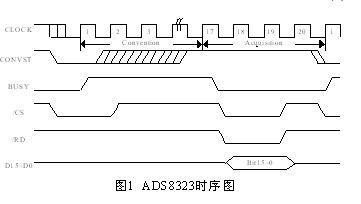

ADS8323需要外接时钟信号,时钟频率范围从25kHZ(1.25kSPS)到10MHZ(500kSPS),其内部的所有动作均与时钟信号同步。工作过程如下:将/CONVST置成低,即可启动转换;在转换过程中,BUSY始终为高;当转换结果被锁存在输出寄存器之后,BUSY变低,此时便可通过将/RD和/CS信号置低读取转换结果。其时序如图1所示。

2.2 高速FIFO——CY7C4231

FIFO芯片是一种具有存储功能的逻辑芯片,它具有两个特点:数据进出有序,输出输入口独立。其内部的读指针和写指针按照先进先出的原则实现数据的存入和读取。

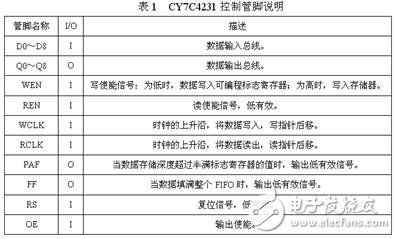

CY7C4231是CYPRESS公司推出了一款高速FIFO芯片。芯片的存储空间是2K×9 bit,读写时间最小是10ns。其主要的控制管脚功能如表1所示。

3.接口电路的CPLD实现

通过上面的介绍,可以大致归纳出接口电路需要实现的主要功能如下:

(1)将A/D转换结果存入FIFO,包括AD芯片的转换过程控制和FIFO的写入过程控制;

(2)MCU读取FIFO中数据,包括FIFO的状态查询或着中断请求、FIFO的读出过程控制。

CPLD由于其速度快、体积小、功耗低、编程灵活、可反复修改逻辑等特点,受到了越来越多的关注。而利用EDA工具进行设计、综合和验证,加速了设计过程,降低了开发风险,缩短了开发周期,提高了效率。本文采用了Altera公司的QuartusII作为设计工具,以EPM7128系列的CPLD芯片实现了上述的接口电路。其总体设计如图2所示。

其中,地址译码模块负责对MCU的地址总线进行译码,产生地址选通信号;控制信号模块负责产生一些总的控制信号,如系统启动信号CtrlBegin、整个电路的复位信号reset等等;FIFO状态查询模块负责向MCU提供当前FIFO的状态特征,以便查询,如半满、半空、全满、全空等状态;中断申请模块可根据FIFO的状态自动产生中断请求信号。AD转换控制与FIFO写控制模块、FIFO读控制模块是整个接口电路的核心单元,下面分别加以介绍。

3.1 AD转换控制与FIFO写控制模块

根据ADS8323与FIFO的使用说明,该模块的工作过程如下:在系统启动信号CtrlBegin有效之后,启动AD转换信号(/CONVST置低);在转换过程中,将数据缓冲区(由CPLD内部实现的一个16Bit的存储器)中的前一次转换结果写入FIFO中,具体来说,首先使低8位数据使能信号LowOE置高,低8位数据被放到数据总线上,然后产生低8位FIFO的写时钟信号FIFO1_WCLK,这样转换结果的低8位就被存入低8位FIFO中,按同样的过程再把转换结果的高8位存入高8位FIFO中;在转换结束后(BUSY为低),将AD的读使能信号/RD置低,于是本次AD的转换结果被写入数据缓冲区;完成一次操作之后,再启动AD转换信号,开始下一次转换过程,周而复始,直到系统启动信号CtrlBegin无效。

该模块可由状态机加以实现。在设计中,我们采用Verilog HDL语言编写,其仿真波形如图3所示。

3.2 FIFO读控制模块

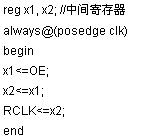

当FIFO中的数据达到一定深度之后,MCU就需要通过该模块向FIFO读取数据。该模块主要产生四个信号,即低8位FIFO的RCLK和OE(定义为RCLK1和OE1)、高8位FIFO的RCLK和OE(定义为RCLK2和OE2)。以往的设计方案是采用两个独立的读地址分别作为RCLK和OE,这种方式虽然操作简单,但需要两个读周期才能完成一次读操作,这样大大降低了工作效率。本文采用一个读地址作为OE信号,再利用对OE的延时信号作为RCLK信号,这样只要RCLK信号的产生介于两次OE之间,就能实现用一个读周期完成一次读操作,这样便大大提高了MCU的工作效率。延时模块由Verilog HDL语言实现,其代码如下:

仿真波形如图4所示。

4.结束语

本文采用CPLD实现了AD芯片、高速FIFO存储器以及MCU之间的接口电路。实验表明,该电路工作稳定可靠,且通用性强,易于移植到其它数据采集系统中。同时,QuartusII等嵌入式技术的使用,简化了开发流程,提高了设计效率。目前,该电路已成功应用于某数据采集系统中。

-

基于NIOS II的SOPC中存储器型外设接口的设计2018-12-07 2849

-

采用CPLD实现ADS8323与高速FIFO接口电路2019-05-23 1570

-

高速SDRAM存储器接口电路设计2019-06-03 1830

-

基于FIFO存储器实现AD转换器与ARM的接口设计2020-12-28 1468

-

基于PCI接口芯片外扩FIFO的FPGA实现2010-01-06 720

-

FIFO存储电路的设计与实现2010-05-04 522

-

FPGA设计的高速FIFO电路技术2010-05-27 3081

-

高速SDRAM存储器接口电路设计(Altera FPGA开发板)2012-08-15 3655

-

高速模数转换器与TMS320C6000DSP接口的FIFO实现2017-05-31 1207

-

设计和调试高速存储器接口的高效设计流程模型介绍2018-01-12 1759

-

fifo存储器芯片型号有哪些2018-04-08 26518

-

Stratix III FPGA的特点及如何实现和高速DDR3存储器的接口2018-06-22 4627

-

基于Verilog HDL语言与双体存储器的交替读写机制实现32X8 FIFO设计2018-12-30 4533

-

TMS320C67系列DSP的EMIF与异步FIFO存储器的接口设计详细资料介绍2019-07-31 1757

-

基于FIFO存储器实现高速AD转换器与ARM处理器的接口设计2019-11-05 3119

全部0条评论

快来发表一下你的评论吧 !