嵌入式系统的深度低功耗应用和优化实现的资料说明

电子说

描述

低功耗系统设计需要注意很多非传统性因素,从硅片工艺技术,直到在微控制器嵌入平台上运行的软件。在系统级做仔细检查可揭示出决定微控制器能效的三个主要参数:有源模式功耗、待机功耗以及工作周期,后者决定了两种状态上所花时间的比率,而这个比率则取决于软件的行为。

低功耗待机状态可以使一只微控制器看似非常高能效,但只有考虑了影响到有源功耗的所有因素后,才能证明其最终性能。

低功耗待机状态可以使一只微控制器看似非常高能效,但只有考虑了影响到有源功耗的所有因素后,才能证明其最终性能。鉴于这个和其它原因,工艺技术、IC架构以及软件结构之间的权衡就是一些决策问题,有一些微妙和有时无法预期的结果。一个MCU中各功能块相互结合的方式,对整体能效有显著的影响。即使硬件实现上看似微小的改变,也可能致使一个系统生命周期内的总能耗发生巨大的波动。

低功耗应用

举例来说,读表与报警系统,通常一节电池要供10年电。某只传感器读取功耗的少许增加(在产品的生命周期中,这种读数动作要发生上亿次),就可能使产品的实际现场寿命减少数年时间。一只简单的烟雾警报器,每秒要探测一次空气中的烟尘粒子,在其生命周期内完成3.15亿次读取。

一只简单烟雾报警器的活动比率(或工作周期)还相对算低的。每只传感器读数时可能花费时间不到数百毫秒就能完成,大部分时间花在当MCU唤醒ADC以及其它敏感模拟元件时的校准和安定上,以使它们达到一个稳定的工作点。在本例中,工作周期是设计的关键,这个设计在约99.88%的时间中是处于不活动状态。

传统的烟雾警报器还算比较简单。考虑一个更复杂的RF设计,它有一个传感器网格,将读数结果转发给一个主控应用。传感器需要从一个主结点聆听活动情况,这样一方面可以通告说自己仍然在网格网络中,或者将最新捕捉的信息发送给路由器。不过,增加活动可能并不影响整个工作周期;相反,采用更高性能的器件,可以在每次激活期间完成更多功能。由于更先进架构与半导体技术,使得处理速度的增加成为可能,较快器件可以提供更高的能效,而较慢器件则要运行更长周期。重点在于了解工艺技术、MCU架构,以及软件实现之间的交互作用。

硅选择

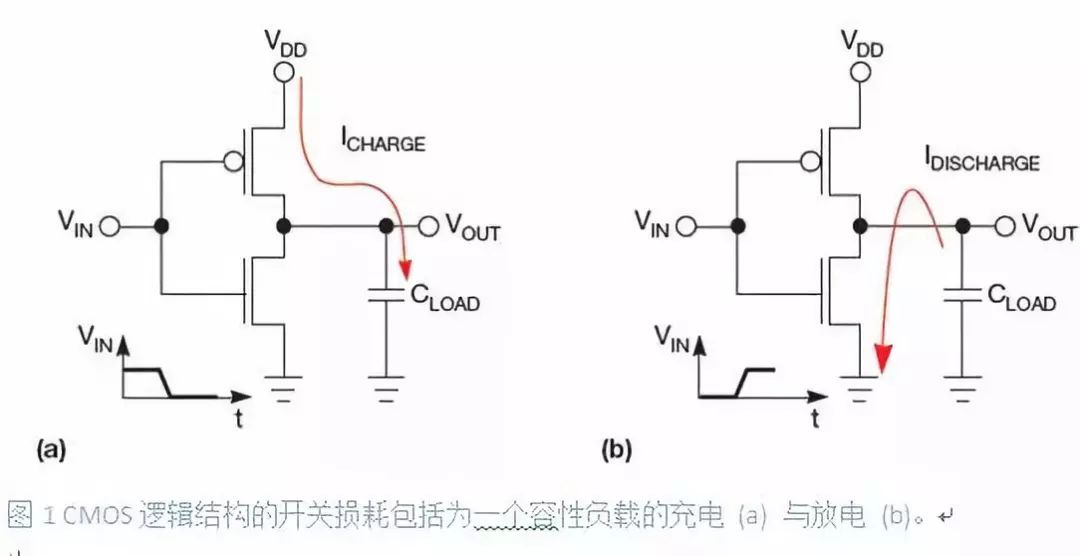

CMOS能耗数据。 几乎所有MCU的实现都使用了CMOS技术(图1)。任何激活态下逻辑电路的功耗都可以用公式CV2f表示,其中C是器件内开关电路路径的总电容,V是电源电压,而f是工作频率。电压和电容都是所采用工艺技术的因素。过去三十年以来,CMOS逻辑的芯片工作电压已经从12V降到不足2V,原因是晶体管尺寸的缩小。鉴于电压在有源功耗的公式中是一个二次项,因此电压的降低有明显的作用。

尽管电容项是线性的,但摩尔定律的缩小也非常有利于降低其整体水平。对于一个给定的逻辑功能,更先进的工艺可提供较低电容,从而获得较前代更低的功耗。另外,先进的设计技术能够实现时钟门控,这样只有完成实际任务的电路才工作,从而降低了总体开关频率。

与其它技术相比,CMOS显著降低了浪费的能量;但是,泄漏电流仍然存在。与有源功耗相反,泄漏功耗会随摩尔定律尺度的缩小而增加,在任何低功耗应用中都要考虑它的因素,因为对于一个低工作周期系统,大部分时间是处于非激活状态。但对有源功耗,电路设计就对实际泄漏有重要影响。与时钟门控类似,电源门控可以大大改善泄漏的效应,使更先进工艺结点成为低工作周期系统的较好选择,尽管理论上较老工艺技术能够提供更低的泄漏数值。

适合的工艺技术。对每组特性集合都存在着一种适当的工艺技术。答案并非简单地取决于一种有最低理论泄漏值的工艺技术,因为器件在睡眠模式下花费的时间很多。在睡眠模式下,可以关闭MCU中大部分的电源,从公式中拿掉泄漏成份。当电路活动时,泄漏是一个较大的问题,但先进晶体管的优势在于能以高得多的效率切换,从而可以轻易地抵消这个问题。

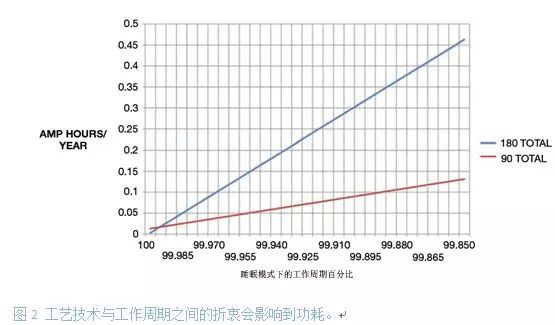

举例来说,90 nm工艺的泄漏电流要比专用的低功耗180 nm工艺高出大约五倍。有源模式功耗要低四倍,但其基数是一个大得多的数值。

例如一个180 nm MCU,其有源耗电为40 mA,深度睡眠模式耗电为60 nA,与这些功率水平相比,90 nm实现的功率水平能够将有源耗电降至10 mA,但睡眠模式电流较高,为300 nA。对90 nm实现来说,MCU必须在0.0008%的时间里为活动状态,才能获得更高的总体能效。换句话说,如果系统每天只活动工作1秒,则90 nm版的能效大约是其180 nm对手的1.5倍。结论是,在选择工艺尺度时,关键在于了解应用的工作周期(图2)。

一旦选择好了合适的工作技术,IC设计者就可以选择进一步优化能源性能。当时钟门控最初问世时,它只在一个相对粗糙的水平上使用。时钟门控增加了一个系统的复杂性,因为电路设计者需要知道在任何确定的时间时,哪个逻辑路径需要时钟信号。

时钟分配。大多数MCU实现都采用一种层次式结构,将时钟信号和相应的电压水平分配到IC的各个部分。各个功能单元(如指令处理块与外设)被划分为组,每组都馈给一个独立的时钟树和电源网络。一个分频器或复用器从一个公共时钟源获得每一组的时钟信号。同样,如果这些组需要不同的电压(这种方案日益普遍),则一组功率晶体管和稳压器会为每组外设提供电压。

为尽量减少设计的复杂性,MCU采用了一种相对简单的时钟门控方法,只要一组中的功率单项均未激活,则会关断整个时钟树。不过,这种方法会向那些在活动组中不工作的逻辑送入时钟。例如,如果当前指令是一个分支指令,CPU核心中的加法单元也会收到一个时钟。如前所述,时钟信号在加法器中触发的转换会使功耗增加CV2f倍。

设计工具与技术的进步已能够使时钟门控的粒度增加到某个点,如果外设或功率单元在该周期内不工作,就不会收到时钟信号。

电压缩放提供了更进一步的节能潜力,它能在必要时,为特定一组功能单元提供一个较低的电压。为一组功率单元或外设提供适当电压的关键在于片上稳压器或dc/dc转换器的实现,以及监控电路的使用,确保IC工作在所需要的电压下。

电源的考虑。片上稳压器为系统设计者提供了更高的灵活性,从而能从一只电池榨取更多电能。例如,片上开关降压转换器(如Silicon Labs公司的SiM3L1xx MCU产品)可以从一只3.6V工业电池获得输入,以高于80%的效率将其转换为1.2V。很多MCU没有这种特性,而是采用线性元件降压到合适电平,会有大量的消耗。在高级的实现中,当电池放电到某个水平,转换器无法做转换工作时,降压稳压器可以关闭。因此,电源可以在设备的整个生命周期上做到优化能效,一切均在软件控制下。

软件的决策

软件的决策

性能的缩放。高能效嵌入应用的实现有赖于软件的设计,软件要以最适当的方式使用硬件资源。什么样才是适合,这不仅取决于应用,而且要看硬件实现。同样,硬件越灵活(包括CPU、时钟、电压和存储器使用),开发者可以获得的节能潜力也越大。能感知硬件的软件工具为嵌入系统工程师提供了更高的认知度,使他们能够更多地了解到哪种更高节能是可实现的。

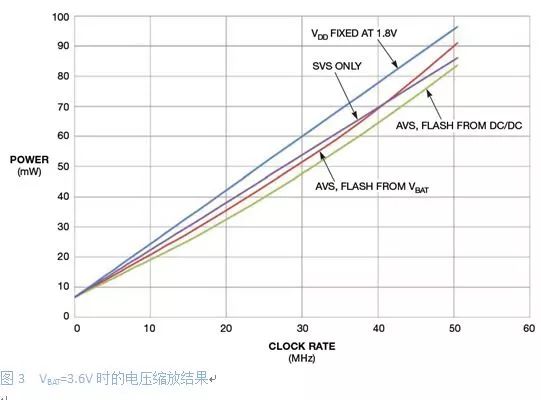

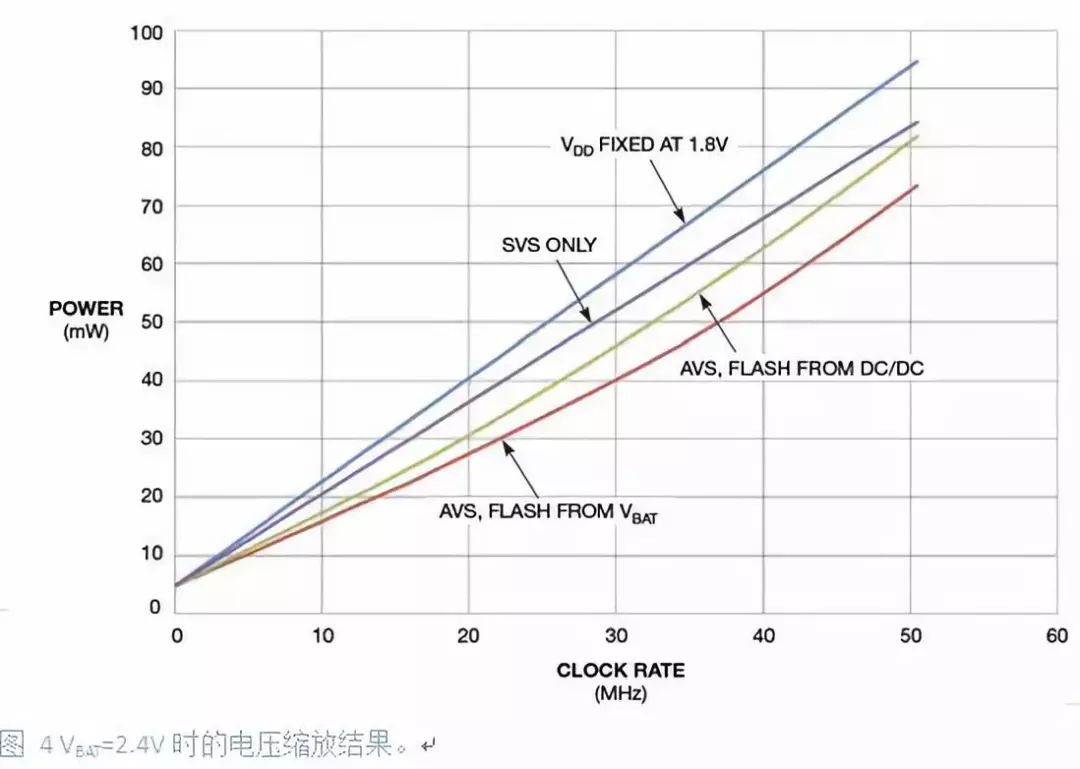

一种选择是采用动态电压缩放,如图3和图4所示。使该技术得以实现的是片上dc/dc转换器与性能监控电路,当应用不需要以最高速度执行指令时,它们提供了降低电压的能力。在这些情况下,系统就工作在较低的功耗下。最终的益处是一个输入电压的函数,可以在产品的生命周期内变化。图中显示了无电压缩放(VDD固定)、SVS(静态电压缩放),以及AVS(动态电压缩放)之间的相对差别。

AVS有一个有意思的地方,这就是AVS策略可以根据系统输入电压而改变。在本例中,当输入为3.6V时,用一个高效的内部dc/dc转换器为内部逻辑以及闪存供电,效率更高。但随着在产品生命周期内的电池放电,输入电压跌落,用输入电压为闪存子系统直接供电就成了更高效的方法,因为内部逻辑可以工作在较闪存更低的电压下。例如,Silicon Labs公司的SiM3L1xx系列MCU就有一个灵活的电源架构,有六个独立和可变的电源域,能够实现这种动态的优化。

增加硬件块(如DMA)可以进一步改变对能耗的折衷。

通常来说,CMOS逻辑电路工作得较慢,因为它们电压低。如果应用可以容忍较低的性能,则较低电压可以因能耗中的二次项而获得大的节能效果,例如常有这种情况,要处理的通信协议,其提交数据的速度不高于某种标准频率。泄漏为电压缩放提供了下限。如果每次运行花费时间太长,则泄漏就开始占据能耗方程的主要地位,从而增加了总能耗。因此,执行一个功能越快越好,然后就使处理器回到睡眠模式,尽量减少泄漏成份。

考虑一个需要完成相当多数字信号处理的无线传感器应用,例如玻璃破碎探测器。在本例中,应用会通过一个快速富利叶变换来分析由音频传感器拾取的振动,其特性频率来自于玻璃的碎裂。FFT比较复杂,因此,如要降低电压而以较低频率执行这个变换,就会大大增加泄漏,

即使是采用较老的工艺技术。本例的最佳方案是以接近最高频率运行这个变换,然后返回睡眠模式,直到要向主结点报告任何结果时。

不过,无线协议代码会产生不同的要求。射频协议要求事件有固定的时序。在这些情况下,协议可能要完全由硬件处理。这就使降低处理器核心电压有了更大的意义。因此,需要做分组组装与传输的代码要运行在适合于无线协议的速度。

增加硬件块(如智能DMA)可以进一步改变能耗的折衷情况。很多DMA控制器都需要处理器的频繁干预,如原生ARM Cortex-M3处理器所提供的DMA控制器。但更多智能DMA控制器能支持一种排队与链接的组合,处理器就可以计算报头、加密数据、分组组装,然后以适当的间隔,将数据的传送工作转交给缓冲存储区,供射频前端使用。在射频链路激活的大多数时间内,处理器可以睡眠,节省大量能源。

存储器使用。对于现代32 bit MCU,软件工程师在存储器块的使用方式上有高度自由。通常MCU会提供一组存储器,包括长期保存代码和数据的非易失存储器,以及存放临时数据的SRAM。多数情况下,访问闪存的功耗要高于SRAM。对于正常使用情况,闪存读取次数是SRAM读取数的三倍。闪存写入消耗的功率更多(需要将整块擦除,然后用一个相对高电压脉冲的漫长序列重新写入)。但对于大多数应用来说,闪存写入操作并不频繁,实际上不会影响到平均功耗。

闪存功耗的一个更进一步因素是如何分配来自处理器的存取。每个闪存块都包含多个页面,每个页面的大小最多可达4k字节。要支持存取,每个页面都必须加电;未被使用的页面则可以维持在低功耗状态。如果一个定期存取的代码段要跨两个闪存页,而不是全在一个页面上,则读取指令相关的能耗就会增加。将跨不同页面的频繁存取代码与数据在内存中重新分配,就可以在一只电池的放电寿命期间节省不小的能量,而不必修改物理硬件。

通常有意义的是复制功能,它更多地使用片上SRAM而不是闪存,无论是读还是写,虽然这种方法看似是对存储容量的低效使用。电池长寿命的优点可以轻易抵消掉更多的内存消耗。

代码优化。能量优化亦可以颠覆传统的代码效率概念。几十年来,嵌入系统工程师很注重针对存储器大小来优化代码,除非性能是压倒一切的指标。能量优化提供了另一种全新的度量标准集。一个重要的考虑是采用32 bit平台上已经普遍提供的片上缓存。

对代码大小的优化能够在缓存中保存更多的可执行代码,从而提高了速度和节省了能耗。不过,函数调用与分支(可重新使用公共代码,从而减少应用的尺寸)会在同列缓存的代码段之间造成不可预期的冲突。这样当需要从主内存中获取指令时,会造成浪费的“缓存颠覆”,以及多闪存页激活。

在产品生命周期内要频繁工作的那些代码,可以充分压缩到能装入缓存中,而不做分支或调用函数,这是有意义的。考虑一个烟雾报警器:即使报警器每周触发一次(也许源于厨房活动所产生的过多烟气),也仅是报警器十年寿命中3.15亿次事件中的520个。绝大部分时间中,代码只要读一下传感器值,然后发现其未超阈值,就让处理器核心返回睡眠状态,等待系统定时器的唤醒。

在警报器获取的所有传感器读数中,只有不到0.0002%的情况才会执行警报生成代码。余下99.9998%的代码执行都是核心传感器读取循环;确保这个代码直接在一个缓存列中执行,就成为最低能量使用的关键。其它代码由于运行得极少,可以使用更传统的技术做优化。

能效工具。对于MCU平台的能效最大化,工具的支持十分重要。要将不同函数分配到闪存的不同页,就需要这样一种链接器,它能够知道目标MCU的存储器详图。链接器可以获得开发人员的输入结果,看这个块是否被分配在了跨页边界上,并生成已经过非易性存储最高能效优化的二进制码。

一般来说,这个代码也用于确保函数与数据的放置方式,即最常执行的部分不会跨多个缓存列。如果MCU供应商提供了这类工具,则实现这种级别的细节要容易得多,因为他们了解每个目标平台的存储器布局与功率需求。而第三方供应商实现这工具则要困难得多。

MCU供应商还详细地了解不同外设与片上总线的组织方式。这一知识可以用于工具中,指导工程师做出不浪费功率的选择。

提示

在工艺技术、IC架构以及软件结构之间的权衡决策,可以得到微妙而有时是无法预期的结果。

电源门控可以减轻泄漏效应,使更先进的工艺结点成为低工作周期系统的较好选择。

片上稳压器为设计人员提供了更多灵活性,能够从一只电池中榨取更多的电荷,而片上dc/dc转换器与性能监控电路则能实现动态的电压缩放。

能感知硬件的软件工具为嵌入系统工程师提供了更多认知能力,从而实现更高的节能。

-

低功耗嵌入式设计的提示和技巧2022-12-28 1251

-

嵌入式低功耗电源管理框架的设计资料分享2021-12-21 1346

-

嵌入式linux功耗优化,嵌入式Linux功耗管理技术设计与实现2021-11-02 656

-

嵌入式Linux的低功耗策略2021-11-01 1046

-

在嵌入式系统中如何实现低功耗设计2020-03-27 2350

-

对于嵌入式系统该如何实现低功耗设计2020-01-27 2843

-

低功耗嵌入式系统该怎么设计?2019-09-02 2041

-

嵌入式系统的组成及其低功耗的设计2017-12-06 899

-

基于μC/OS-II嵌入式系统丌发中低功耗系统的设计2017-11-06 825

-

基于嵌入式DSP系统的低功耗优化设计2016-08-20 1969

-

嵌入式系统中的低功耗设计2014-01-21 3784

-

超低功耗嵌入式系统设计技巧2012-08-18 2295

-

嵌入式系统设计中的低功耗技术2011-10-12 1597

-

基于μCOS-II嵌入式系统的低功耗开发2009-12-23 1063

全部0条评论

快来发表一下你的评论吧 !