数据通信的两种基本方式并行通信与串行通信原理解析

接口/总线/驱动

描述

数据通信的基本方式可分为并行通信与串行通信两种:

并行通信:是指利用多条数据传输线将一个资料的各位同时传送。它的特点是传输速度快,适用于短距离通信,但要求通讯速率较高的应用场合。

串行通信:是指利用一条传输线将资料一位位地顺序传送。特点是通信线路简单,利用简单的线缆就可实现通信,降低成本,适用于远距离通信,但传输速度慢的应用场合。

一、异步通信及其协议

异步通信以一个字符为传输单位,通信中两个字符间的时间间隔是不固定的,然而在同一个字符中的两个相邻位代码间的时间间隔是固定的。

通信协议(通信规程):是指通信双方约定的一些规则。在使用异步串口传送一个字符的信息时,对资料格式有如下约定:规定有空闲位、起始位、资料位、奇偶校验位、停止位。

异步通讯的时序,如图5-1。

其中各位的意义如下:

起始位:先发出一个逻辑”0”信号,表示传输字符的开始。

资料位:紧接着起始位之后。资料位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。从最低位开始传送,靠时钟定位。

奇偶校验位:资料位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送的正确性。

停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。

空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

波特率:是衡量资料传送速率的指针。表示每秒钟传送的二进制位数。例如资料传送速率为120字符/秒,而每一个字符为10位,则其传送的波特率为10×120=1200字符/秒=1200波特。

注:异步通信是按字符传输的,接收设备在收到起始信号之后只要在一个字符的传输时间内能和发送设备保持同步就能正确接收。下一个字符起始位的到来又使同步重新校准(依靠检测起始位来实现发送与接收方的时钟自同步的)。

二、资料传送方式

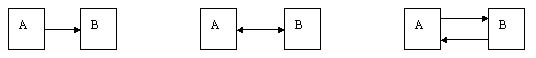

根据资料传送方向的不同有以下三种方式。如图5-2所示。

(1)单工方式 (2)半双工方式 (3)全双工方式

图5-2 资料传送方式

1、单工方式

资料始终是从A设备发向B设备。

2、 半双工方式

资料能从A设备传送到B设备,也能从B设备传送到A设备。在任何时候资料都不能同时在两个方向上传送,即每次只能有一个设备发送,另一个设备接收。但是通讯双方依照一定的通讯协议来轮流地进行发送和接收。

3、 全双工方式

允许通信双方同时进行发送和接收。这时,A设备在发送的同时也可以接收,B设备亦同。全双工方式相当于把两个方向相反的单工方式组合在一起,因此它需要两条数据传输线。在计算机串行通讯中主要使用半双工和全双工方式。

三、信号传输方式

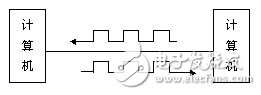

1、基带传输方式

在传输线路上直接传输不加调制的二进制信号,如图所示。它要求传送线的频带较宽,传输的数字信号是矩形波。

基带传输方式仅适宜于近距离和速度较低的通信。

2、频带传输方式

传输经过调制的模拟信号

在长距离通信时,发送方要用调制器把数字信号转换成模拟信号,接收方则用解调器将接收到的模拟信号再转换成数字信号,这就是信号的调制解调。

实现调制和解调任务的装置称为调制解调器(MODEM)。采用频带传输时,通信双方各接一个调制解调器,将数字信号寄载在模拟信号(载波)上加以传输。因此,这种传输方式也称为载波传输方式。这时的通信线路可以是电话交换网,也可以是专用线。

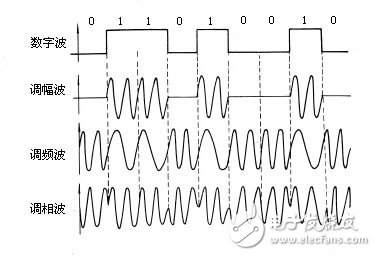

常用的调制方式有三种:

调幅、调频和调相,分别如下图所示。

四、串行接口标准

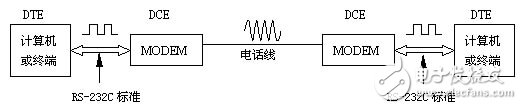

串行接口标准:指的是计算机或终端(资料终端设备DTE)的串行接口电路与调制解调器MODEM等(数据通信设备DCE)之间的连接标准。

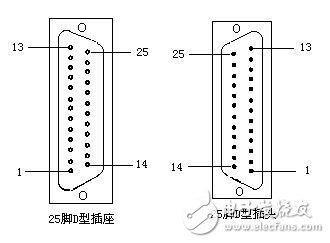

RS-232C标准

RS-232C是一种标准接口,D型插座,采用25芯引脚或9芯引脚的连接器,如图5-5所示。

图5-5

微型计算机之间的串行通信就是按照RS-232C标准设计的接口电路实现的。如果使用一根电话线进行通信,那幺计算机和MODEM之间的联机就是根据RS-232C标准连接的。其连接及通信原理如图5-6所示

图5-6

RS232信号定义

RS-232C标准规定接口有25根联机。只有以下9个信号经常使用。

引脚和功能分别如下:

1. TXD(第2脚):发送资料线,输出。发送资料到MODEM。

2. RXD(第3脚):接收资料线,输入。接收资料到计算机或终端。

3. (第4脚):请求发送,输出。计算机通过此引脚通知MODEM,要求发送资料。

4. (第5脚):允许发送,输入。发出 作为对 的回答,计算机才可以进行发送资料。

5. (第6脚):资料装置就绪(即MODEM准备好),输入。表示调制解调器可以使用,该信号有时直接接到电源上,这样当设备连通时即有效。

6. CD(第8脚):载波检测(接收线信号测定器),输入。表示MODEM已与电话线路连接好。

7. 如果通信线路是交换电话的一部分,则至少还需如下两个信号:

8. RI(第22脚):振铃指示,输入。MODEM若接到交换台送来的振铃呼叫信号,就发出该信号来通知计算机或终端。

9. (第20脚):资料终端就绪,输出。计算机收到RI信号以后,就发出 信号到MODEM作为回答,以控制它的转换设备,建立通信链路。

10. GND(第7脚):信号地

逻辑电平

RS-232C标准采用EIA电平,规定:

“1”的逻辑电平在-3V~-15v之间

“0”的逻辑电平在+3V~+15V之间。

由于EIA电平与TTL电平完全不同,必须进行相应的电平转换,MCl488完成TTL电平到EIA电平的转换,MCl489完成EIA电平到ITL电平的转换。还有MAX232可以同时完成TTL-》EIA和EIA-》TTL的电平转换。

除了RS-232C标准以外,还有一些其它的通用的异步串行接口标准,如:

RS-423A标准

为了克服RS-232C的缺点,提高传送速率,增加通信距离,又考虑到与RS-232C的兼容性,美国电子工业协会在1987年提出了RS-423A标准。该标准的主要优点是在接收端采用了差分输入。而差分输入对共模干扰信号有较高的抑制作用,这样就提高了通信的可靠性。RS-423A用-6v表示逻辑“1”,用+6v表示逻辑“0”,可以直接与RS-232C相接。采用RS-423A标准以获得比RS-232C更佳的通信效果。图5-7是RS423A的连接示意图。

图5-7

RS-422A标准

RS-422A总线采用平衡输出的发送器,差分输入的接收器。如图5-8所示。

图5-8

RS-422A的输出信号线间的电压为±2v,接收器的识别电压为±0.2v。共模范围±25v。在高速传送信号时,应该考虑到通信线路的阻抗匹配,一般在接收端加终端电阻以吸收掉反射波。电阻网络也应该是平衡的,如图5-9所示。

图5-9 为RS-422A平衡输出差分输示意图

RS-485标准

RS-485适用于收发双方共享一对线进行通信,也适用于多个点之间共享一对线路进行总线方式联网,但通信只能是半双工的,线路如图5-10所示。

图5-10

典型的RS232到RS422/485转换芯片有:MAX481/483/485/487/488/489/490/491,SN75175/176/184等等,它们均只需单一+5v电源供电即可工作(芯片内部采用电荷泵方式升压)。具体使用方法可查阅有关技术手册。

五、S3C2410内置的UART控制器

S3C2410内部具有3个独立的UART控制器,每个控制器都可以工作在Interrupt(中断)模式或DMA(直接内存访问)模式,也就是说UART控制器可以CPU与UART控制器传送资料的时候产生中断或DMA请求。并且每个UART均具有16字节的FIFO(先入先出寄存器),支持的最高波特率可达到230.4Kbps

图5-11是S3C2410内部UART控制器的结构图

图5-11

UART的操作

UART的操作分为以下几个部分,分别是:资料发送、资料接收、产生中断、产生波特率、Loopback模式、红外模式以及自动流控模式。

资料发送

发送的资料帧格式是可以编程设置的。它包含了起始位、5~8个资料位、可选的奇偶校验位以及1~2位停止位。这些都是通过UART的控制寄存器 ULCONn 来设置的。

资料接收

同发送一样,接收的资料帧格式也是可以进行编程设置的。此外,还具备了检测溢出出错、奇偶校验出错、帧出错等出错检测,并且每种错误都可以置相应的错误标志。

自动流控模式

S3C2410的UART0和UART1都可以通过各自的nRTS和nCTS信号来实现自动流控。

在自动流控(AFC)模式下nRTS取决于接收端的状态,而nCTS控制了发送断的操作。具体地说:只有当nCTS有效时(表明接收方的FIFO已经准备就绪来接收资料了),UART才会将FIFO中的资料发送出去。在UART接收资料之前,只要当接收FIFO有至少2-byte空余的时候,nRTS就会被置为有效。图5-12是UART 自动流控模式的连接方式

图5-12

中断/DMA请求产生

S3C2410的每个UART都有7种状态,分别是:溢出覆盖(Overrun)错误、奇偶校验错误、帧出错、断线错误、接收就绪、发送缓冲空闲、发送移位器空闲。它们在UART状态寄存器 UTRSTATn / UERSTATn 中有相应的标志位。

波特率发生器

每个UART控制器都有各自的波特率发生器来产生发送和接收资料所用的序列时钟,波特率发生器的时钟源可以CPU内部的系统时钟,也可以从CPU的 UCLK 管脚由外部取得时钟信号,并且可以通过 UCONn 选择各自的时钟源。

波特率产生的具体计算方法如下:

当选择CPU内部时钟时:

UBRDIVn=(int)(PCLK/(bps*16))-1,bps为所需要的波特率值,PCLK为CPU内部外设总线(APB)的工作时钟。

当需要得到更精确的波特率时,可以选择由 UCLK 引入的外部时钟来生成。

UBRDIVn=(int)(UCLK/(bps*16))-1

LoopBack操作模式

S3C2410 CPU的UART提供了一种测试模式,也就是这里所说的LoopBack模式。在设计系统的具体应用时,为了判断通讯故障是由于外部的数据链路上的问题,还是CPU内驱动程序或CPU本身的问题,这就需要采用LoopBack模式来进行测试。在LoopBack模式中,资料发送端TXD在UART内部就从逻辑上与接收端RXD连在一起,并可以来验证资料的收发是否正常。

UART控制寄存器

下面将针对UART的各个控制寄存器逐一进行讲解,以期对UART的操作和设置能有更进一步的了解。

ULCONn (UART Line Control Register)见图5-13

图5-13

Word Length :资料位长度

Number of Stop Bit :停止位数

Parity Mode :奇偶校验位类型

Infra-Red Mode :UART/红外模式选择(当以UART模式工作时,需设为“0”)

UCONn (UART Control Register)见图5-14

Receive Mode :选择接收模式。如果是采用DMA模式的话,还需要指定说使用的DMA信道。

Transmit Mode :同上。

Send Break Signal :选择是否在传1帧资料中途发送Break信号。

Loopback Mode :选择是否将UART置于Loopback测试模式。

Rx Error Status Interrupt Enable :选择是否使能当发生接收异常时,是否产生接收错误中断。

Rx Time Out Enable :是否使能接收超时中断。

Rx Interrupt Type :选择接收中断类型。

选择0:Pulse(脉冲式/边沿式中断。非FIFO模式时,一旦接收缓冲区中有资料,即产生一个中断;为FIFO模式时,一旦当FIFO中的资料达到一定的触发水平后,即产生一个中断)

选择1:Level(电平模式中断。非FIFO模式时,只要接收缓冲区中有资料,即产生中断;为FIFO模式时,只要FIFO中的资料达到触发水平后,即产生中断)

Tx Interrupt Type :类同于Rx Interrupt Type

Clock Selection :选择UART波特率发生器的时钟源。

图5-14

UFCONn (UART FIFO Conrtol Register)见图5-15

FIFO Enable :FIFO使能选择。

Rx FIFO Reset :选择当复位接收FIFO时是否自动清除FIFO中的内容。

Tx FIFO Reset :选择当复位发送FIFO时是否自动清除FIFO中的内容。

Rx FIFO Trigger Level :选择接收FIFO的触发水平。

Tx FIFO Trigger Level :选择发送FIFO的触发水平。

图5-15

UMCONn (UART Modem Control Register)见图5-16

Request to Send :如果在AFC模式下,该位将由UART控制器自动设置;否则的话就必须由用户的软件来控制。

Auto Flow Control :选择是否使能自动流控(AFC)。

图5-16

UTRSTATn (UART TX/RX Status Register)见图5-17

Receive buffer data ready :当接收缓冲寄存器从UART接收端口接收到有效资料时将自动置“1”。反之为“0”则表示缓冲器中没有资料。

Transmit buffer empty :当发送缓冲寄存器中为空,自动置“1”;反之表明缓冲器中正有资料等待发送。

Transmitter empty :当发送缓冲器中已经没有有效资料时,自动置“1”;反之表明尚有资料未发送。

图5-17

UERSTATn (UART Error Status Register)见图5-18

Overrun Error :为“1”,表明发生Overrun错误。

Frame Error :为“1”。表明发生Frame(帧)错误。

图5-18

UFSTATn :(UART FIFO Status Register)见图5-19

Rx FIFO Count :接收FIFO中当前存放的字节数。

Tx FIFO Count :发送FIFO中当前存放的字节数。

Rx FIFO Full :为“1“表明接收FIFO已满。

Tx FIFO Full :为“1“表明发送FIFO已满。

图5-19

UMSTATn :(UART FIFO Status Register)见图5-20

Clear to Send :为“0”表示CTS无效;为“1”表示CTS有效。

Delta CTS :指示自从上次CPU访问该位后,nCTS的状态有无发生改变。

为“0”则说明不曾改变;反之表明nCTS信号已经变化了。

图5-20

UTXHn 和 URXHn 分别是UART发送和接收资料寄存器

这两个寄存器存放着发送和接收的资料,当然只有一个字节8位资料。需要注意的是在发生溢出错误的时候,接收的资料必须要被读出来,否则会引发下次溢出错误

UBRDIVn :(UART Baud Rate Divisor Register)见图5-21

图5-21

关于UART波特率的计算方法,在前面的内容中已经有详细的阐述,此处不做多余说明。

小结:读写状态寄存器UTRSTAT 以及错误状态寄存UERSTAT,可以反映芯片目前的读写状态以及错误类型。FIFO 状态寄存器UFSTAT 和MODEM 状态寄存器UMSTAT,通过前者可以读出目前FIFO 是否满以及其中的字节数;通过后者可以读出目前MODEM 的CTS状态。

-

串行通信和并行通信的区别是什么2025-07-22 3317

-

数据通信网关是什么?数据通信网关的功能作用2024-05-29 2609

-

数据通信的基本概念2023-05-05 4961

-

计算机串行通信基础2022-02-16 1532

-

51学习第七天(一)--计算机串口通信基础--通信方式分类--串行通信特点/分类/传输方向--传输速率与传输距离--并行通信特点2021-12-20 1286

-

并行与串行通信机器的通信方式有哪几种2021-12-08 1415

-

数据通信介绍2021-08-20 1607

-

并行通信和串行通信的区别2021-07-27 2132

-

数据通信,数据通信原理是什么?2010-03-17 6587

-

无线移动数据通信,无线移动数据通信是什么意思2010-03-13 3277

-

基于Matlab环境的串行数据通信2009-09-03 786

-

数据通信基础课件2009-06-27 6684

-

什么是数据通信2009-06-14 4539

-

数据通信基础2009-04-28 834

全部0条评论

快来发表一下你的评论吧 !