在高速的AD转换中 FPGA承担着不可替代的作用

可编程逻辑

描述

AD转换,也叫模数转换,是将模拟信号转换为数字信号。目前包括电脑CPU,ARM,FPGA,处理的信号都只能是数字信号,所以数据信号在进入处理芯片前必须要进行AD转换。

在高速的AD转换中,FPGA以其高速的处理能力,并行的运行结构,丰富的IO资源,往往承担者不可替代的作用。

下面给出一个实际的设计方案。

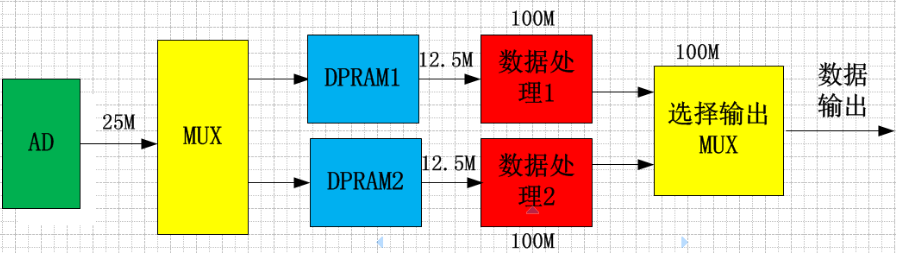

AD芯片的时钟为25M,FPGA内部系统时钟频率为100M,FPGA内部处理AD数据的处理模块需要8个时钟周期才能处理完一个数据。

根据上述给出的条件,我们可以知道。按正常思路设计方案,肯定会造成AD数据的丢失,为什么会丢失数据,试想一下,FPGA处理一个数据需要8个时钟周期,才能采集下一个数据,这样算下来AD需要的时钟是12.5M,而给定的AD时钟是25M,所以肯定会漏掉数据。

根据分析,可以采用乒乓操作通过缓存降低数据采样率。

乒乓操作如下图:

具体乒乓操作为什么能够降低数据速率,这里将不做详细介绍。

以上方案可以满足上述处理AD数据的需求。

紧接着继续增加需求条件,要求数据处理需要连续,不能打乱顺序,前面数据的处理会影响后续数据处理。这样乒乓操作将不适合,具体原因,读者可以自己想一下(乒乓操作会以数据块打乱数据顺序)。

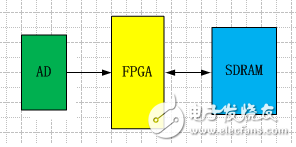

根据上述条件,设计方案需要修改。可以外加存储器,FPGA片上存储器资源有限。

添加SDRAM提高存储速度和存储量。

继续添加需求,如果AD数据连续不断,那么势必是造成SDRAM溢出。那么上述设计方案也不可采取了。

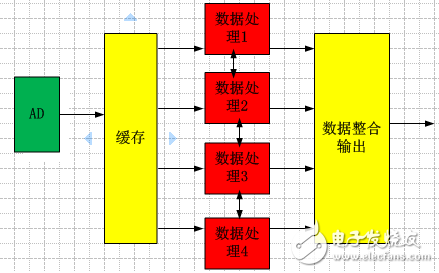

最后根据条件,数据需要连续处理,后面数据的处理要根据前面数据的处理状态决定,而且数据连续不断。

为了满足时序要求,并且不能遗漏数据,重新对方案进行设计。

将数据处理模块分成几个小的处理模块。不仅降低数据处理速率,同时个处理模块之间相互联系,后续数据处理能够知道前面数据处理的状态。最终将处理后的数据顺序输出即可。

-

基于FPGA的高速AD转换2012-08-06 10066

-

FPGA能否继续在SoC类应用中替代ASIC?2021-04-08 1765

-

FPGA在无线应用中的作用2021-05-25 1553

-

基于FPGA的高速图像预处理系统设计2008-11-20 1095

-

TCAM在高速路由查找中的应用及其FPGA实现2015-11-04 1146

-

在自动驾驶汽车商业化过程中,高精地图的作用不可替代2018-10-11 2439

-

2018年社会热点事件回顾 安防发挥了不可替代的作用2018-12-24 1845

-

华为用案例分析5G在各行各业中承担的作用2020-08-18 7283

-

连接器的外壳具体承担了哪些作用2022-11-24 2175

-

锂电池生产工艺中变频器承担着什么作用2023-01-17 1492

-

示波器探头在高速信号测量中的作用2024-05-30 1500

-

FPGA高速收发器的特点和应用2024-08-05 1668

-

变频器中的变压器有什么作用2024-08-10 4019

-

土压力计在闸坝工程中起到什么作用2025-01-16 633

-

晶台高速光耦在电源驱动中的应用2025-11-25 230

全部0条评论

快来发表一下你的评论吧 !