浅谈Zynq7000 FPGA引脚功能有哪些

可编程逻辑

描述

很多人做了很久的FPGA,知道怎么去给信号分配引脚,却对这些引脚的功能及其资源限制知之甚少;在第一章里对Zynq7000系列的系统框架进行了分析和论述,对Zynq7000系列的基本资源和概念有了大致的认识,然而要很好地进行硬件设计,还必须了解芯片的引脚特性,以确定其是否符合我们的选型要求,这些要求包括GTX引脚数目、select IO引脚数目、select IO引脚的资源配置情况、PS IO的数目及类型等。

1. Zynq7000系列引脚分类

Zynq7000系列引脚的分类是确定的,而各类引脚的数目则因芯片封装的不同而不同,(为了便于理解,本文所列引脚数目皆以XQ7Z045 FFG900封装为例,文章其他部分不再做出说明)其主要类型如下:

Configuration Pins In Bank 0

1.2. Power/Ground Pins

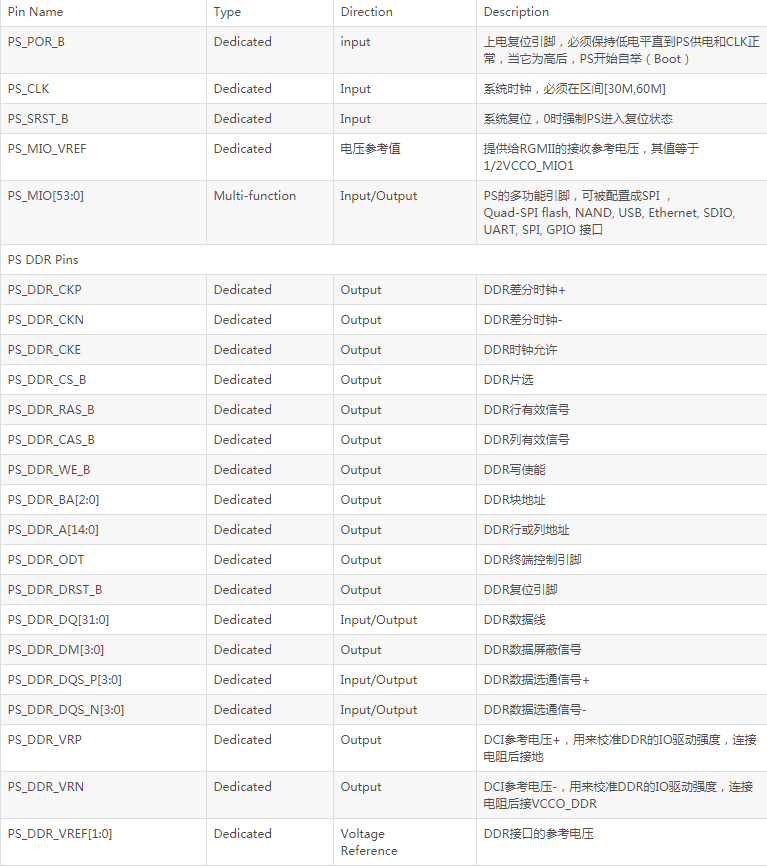

1.3. PS IO Pins

1.4. XADC Pins

1.5. Multi-gigabit Serial Transceiver Pins (GTXE2 and GTPE2)

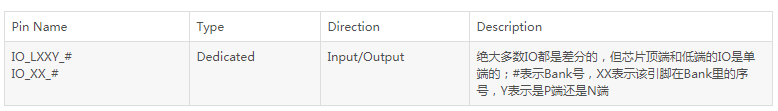

1.6. Select IO

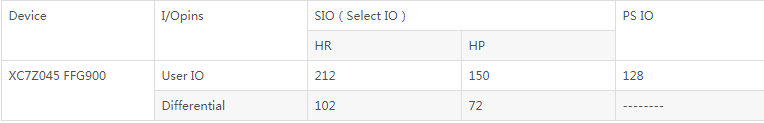

XC7Z045 FFG900芯片里Select IO的差分情况如下所示:

HR:High Range,其电压范围1.2và3.3V 延时资源只有IDELAY2;HP:High performance,其电压1.8V,延时资源既有IDELAY2也有ODELAY2;

需要注意的是,很多Select IO是多功能引脚(Multi-function),它们既可以当做普通IO来用,又可以当做特殊引脚如时钟引脚来用,特殊功能说明如下:

-

ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念2021-05-12 19942

-

zynq7000 BSP无法在u-boot加载运行,为什么?2024-09-13 908

-

zynq7000 BSP无法在u-boot加载运行怎么解决?2024-09-27 875

-

dac3174与xilinx zynq7000系列连接,fpga的案例参考代码有没有?2024-11-25 373

-

【Z-turn Board试用体验】+板上资源Zynq7000启动流程的学习2015-05-27 9499

-

【Z-turn Board试用体验】+Zynq7000启动流程介绍2015-07-22 5473

-

分享黑金ZYNQ7000系列视频教程2016-11-14 22970

-

在zynq7000上实现300M以上的接收数据并转发2018-05-14 5876

-

ZYNQ7000搭建嵌入式Linux操作系统2021-12-17 1422

-

在zynq7000上使用rtt移植SD卡驱动和文件系统出现报错2022-03-30 2542

-

Zynq7000系列之芯片引脚功能综述2017-02-09 6494

-

第二章 Zynq7000芯片的简介2017-02-28 1608

-

Xilinx Zynq-7000系列安全配置策略2017-11-17 10731

-

ZYNQ的启动流程2022-05-07 8602

-

基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南2024-12-10 981

全部0条评论

快来发表一下你的评论吧 !