Xilinx FPGA的电源设计详解

可编程逻辑

描述

本篇主要介绍Xilinx FPGA的电源设计,主要包括电源种类、电压要求、功耗需求,上下电时序要求,常见的电源实现方案等。

1、电压种类及要求

随着FPGA的发展,其电压类型越来越丰富,主要包括以下几种类型:

Processor System电压,主要给Zynq系列SoC中的ARM供电,包括VCC_PSINTFP、VCC_PSINTLP、VCC_PSAUX、VCC_PSINTFP_DDR、VCC_PSADC、VCC_PSPLL、VPS_MGTRAVCC、VPS_MGTRAVTT、VCCO_PSDDR、VCC_PSDDR_PLL、VCCO_PSIO、VCC_PSBATT等;

FPGA Logic电压,主要给FPGA逻辑部分供电,包括VCCINT、VCCINT_IO、VCCBRAM、VCCAUX、VCCO、VCCAUX_IO、VBATT等;

GTx Transceiver电压,主要给FPGA部分的GTx高速收发器供电,包括VCCINT_GT、VMGTAVCC、VMGTAVTT、VMGTVCCAUX、VMGTAVTTRCAL;

System Monitor电压,主要给FPGA部分的ADC供电,包括VCCADC、VREFP;

High Bandwidth Memory电压,包括VCC_HBM、VCC_IO_HBM、VCCAUX_HBM;

VCU电压,只有Zynq UltraScale+ MPSoC系列带图像处理内核的器件才有,包括VCCINT_VCU;

RF电压,只有Zynq UltraScale+ RFSoC系列才有,包括VADC_AVCC、VADC_AVCCAUX、VDAC_AVCC、VDAC_AVCCAUX、VDAC_AVTT、VCCINT_AMS、VCCSDFEC;

以上各种电压的供电对象不同,对精度的要求也不一样,针对不同架构的FPGA,其对电压的精度要求也不一样,其纹波范围从2%到5%不等,但整体要求都比较高,而电流要求却越来越大,比如VCCINT最大能到几十安。同时各种电压值不同,有的可以合并,有的却不能合并,同时还需要时序上的控制。

针对Zynq UltraScale+ MPSoC(ZU+ MPSoC)、Zynq UltraScale+ RFSoC(ZU+ RFSoC)、Zynq 7000(Z7)、UltraScale +(US+包括VU+和KU+)、UltraScale(US包括VU和KU)、7系列等,对每一类型电压及要求电压值、精度罗列如下表:

| 电压类型 | ZU+ MPSoC | ZU+ RFSoC | Z7 | US+ | US | 7 Series | |

| Logic | VCCINT |

0.85(3%) 0.72(3%) 0.9(3%) |

0.85(3%) 0.72(3%) |

1.0(3%) 0.95(3%) |

0.85(3%) 0.72(3%) 0.9(3%) |

0.95(3%) 0.9(2.2%)KU 1.0(3%) |

1.0(3%) 0.9(3%) 0.95(2%) AKV三个系列不同 |

| VCCINT_IO |

0.85(3%) 0.9(3%) |

0.85(3%) | × |

0.85(3%) 0.9(3%) |

0.95(3%) 0.9(2.2%)KU 1.0(3%) |

× | |

| VCCBRAM |

0.85(3%) 0.9(3%) |

0.85(3%) |

1.0(3%) 0.95(3%) |

0.85(3%) 0.9(3%) |

0.95(3%) 1.0(3%) |

1.0(3%) 0.9(3%) 0.95(3%) AKV三个系列不同 |

|

| VCCAUX | 1.8(3%) | 1.8(3%) | 1.8(5%) | 1.8(3%) | 1.8(5%) | ||

| VCCO | √ | √ | √ | √ | √ | √ | |

| VCCAUX_IO | 1.8(3%) | 1.8(3%) |

1.8(5%) 2.0(3%) |

1.8(3%) |

1.8(5%) 2.0(3%) A7没有 |

||

| VBATT | √ | √ | √ | √ | |||

| GTx | VCCINT_GT | × | × | × |

0.85(3%) 0.9(3%) 只有VU+才有 |

× | × |

| VMGTAVCC | 0.9(3%) | 0.9(3%) |

1.0(0.97~1.08) 1.05(1.02~1.08) |

0.9(3%) |

1.0(3%) 1.03(3%)VU |

1.0(0.97~1.08) 1.05(1.02~1.08) |

|

| VMGTAVTT | 1.2(3%) | 1.2(3%) | 1.2(2.5%) | 1.2(3%) |

1.2(2.5%) 1.23(2.4%)VU |

1.2(2.5%) | |

| VMGTVCCAUX | 1.8(3%) | 1.8(3%) | 1.8(2.7%) | 1.8(3%) | 1.8(2.7%) | 1.8(2.7%) | |

| VMGTAVTTRCAL | 1.2(3%) | 1.2(3%) | 1.2(2.5%) | 1.2(3%) |

1.2(2.5%) 1.23(2.4%)VU |

1.2(2.5%) | |

| System Monitor | VCCADC | 1.8(3%) | 1.8(3%) | 1.8(5%) | 1.8(3%) | 1.8(5%) | |

| VREFP | 1.25(4%) | 1.25(4%) | 1.25(4%) | 1.25(4%) | 1.25(4%) | ||

| Processor System | VCC_PSINTFP |

0.85(5%) 0.9(3%) |

0.85(5%) | VCC_PSINT(1.0(5%)) | |||

| VCC_PSINTLP |

0.85(5%) 0.9(3%) |

0.85(5%) | |||||

| VCC_PSAUX | 1.8(5%) | 1.8(5%) | 1.8(5%) | ||||

| VCC_PSINTFP_DDR |

0.85(5%) 0.9(3%) |

0.85(5%) | × | ||||

| VCC_PSADC | 1.8(5%) | 1.8(5%) | × | ||||

| VCC_PSPLL | 1.2(3%) | 1.2(3%) | 1.8(5%) | ||||

| VPS_MGTRAVCC | 0.85(3%) | 0.85(3%) | × | ||||

| VPS_MGTRAVTT | 1.8(3%) | 1.8(3%) | × | ||||

| VCCO_PSDDR | DDR I/O | DDR I/O | DDR I/O | ||||

| VCC_PSDDR_PLL | 1.8(5%) | 1.8(5%) | × | ||||

| VCCO_PSIO | MIO | MIO | MIO | ||||

| VCC_PSBATT | √ | √ | × | ||||

| HBM | VCC_HBM | 1.2(3%)VU+ | |||||

| VCC_IO_HBM | 1.2(3%)VU+ | ||||||

| VCCAUX_HBM | 2.5(3%)VU+ | ||||||

| VCU | VCCINT_VCU | 0.9(3%) | |||||

| RF | VADC_AVCC | 0.925(3%) | |||||

| VADC_AVCCAUX | 1.8(3%) | ||||||

| VDAC_AVCC | 0.925(3%) | ||||||

| VDAC_AVCCAUX | 1.8(3%) | ||||||

| VDAC_AVTT |

2.5(3%) 3.0(3%) |

||||||

| VCCINT_AMS | 0.85(3%) | ||||||

| VCCSDFEC | 0.85(3%) |

2、功耗

FPGA的功耗包括所用逻辑单元数/BRAM数等内部资源、工作时钟频率、切换速率、布线和I/O功耗等。对于I/O功耗,影响因素包括输出类型、工作时钟频率、以及输出的信号翻转数量以及输出负载等。实际功耗取决于特定的系统设计。本部分内容主要针对FPGA logic部分的功耗,而对于Zynq系列,由于其操作系统不同、应用不同,无法进行详细计算,但可以通过软件进行粗略评估。

整个FPGA设计的总功耗由三部分功耗组成:芯片静态功耗、设计静态功耗、设计动态功耗。

芯片静态功耗:FPGA在上电完成后还未配置时的功耗,主要是晶体管的泄露电流所消耗的功耗。

设计静态功耗:当FPGA配置完成后,当设计还未启动时,需要维持I/O的静态电流,时钟管理和其它部分电路的静态功耗。

设计动态功耗:FPGA内设计正常启动后,设计的功耗;这部分功耗的多少主要取决于芯片所用电平,以及FPGA内部逻辑和布线资源的占用情况等。

2.1、待机功耗(芯片静态功耗)

由于漏电流的存在,器件在待机时也会消耗能量。待机功耗随芯片DIE的大小、温度以及工艺的变化而变化。可以利用器件特征参数来模拟待机功耗,并定义为两类:典型功耗和最大功耗。

2.2、IO功耗(设计静态功耗)

I/O功耗是VCCO功耗,主要来自器件输出引脚连接的外部负载电容、阻抗模式输出驱动电路以及外部匹配网络(如果有)的充放电电流。

如前所述,FPGA内部要实际消耗一部分VCCO功耗,外部匹配电阻网络以及输出电容负载消耗了另一部分能量。设计人员在规划散热方案时,应考虑VCCO的内部功耗。作为VCCO电源输出功率的一部分,设计人员也应考虑外部功耗的组成。

2.3、动态功耗(设计动态功耗)

内部节点改变逻辑状态时(例如,从逻辑0变到逻辑1)会形成器件内部动态功耗,因为它需要能量对逻辑阵列和互联网络的内部电容进行充放电。内核动态功耗包括逻辑单元功耗和导线功耗。LE功耗来自内部节点电容充放电以及内部电阻单元的电流损耗。导线功耗来自每个LE驱动外部导线电容时的充放电电流。内核动态功耗主要来自以下结构单元:

LUT

RAM模块

DSP Slice

锁相环(PLL)

时钟树网络

GTx收发器

IP使用情况

IO使用情况

2.4、功耗设计

前两部分的功耗取决于FPGA芯片及硬件设计本身,很难有较大的改善。可以优化的是第3部分功耗:设计动态功耗,这部分功耗占总功耗的90%以上,因此降低设计动态功耗是降低整个系统功耗的关键因素。

Tjmax>θJA*PD+TA

其中Tjmax表示FPGA芯片的最高结温(maximum junction temperature);θJA表示FPGA与周围大气环境的结区热阻抗(Junction to ambient thermalresistance),单位是℃/W;PD表示FPGA总功耗(power dissipation),单位是W;TA表示周围环境温度。

以XC7K325T-2FFG900I系列芯片为例,θJA=9.7℃/W,在TA=55℃的环境中,想要结温Tjmax不超过100°C的情况下,可以推算FPGA的总功耗为:

PD

因此实际功耗只要超过此值就需要进行优化处理,优化处理的方法主要有两种:一是降低θJA:热阻抗取决于芯片与环境的热传导效率,可通过加散热片或者风扇减小热阻抗;二是减小PD:通过优化FPGA设计,降低总功耗。下面就针对这两部分进行介绍。

2.4.1、降低θJA

此部分详见之前的文章《可靠性设计之降额设计》。

2.4.1、减小PD

2.4.1.1、功耗估计

Xilinx FPGA的功耗评估常见的有几种方案:Xilinx自己的XPE(可以在xilinx官网上下载到:http://www.xilinx.com/power,它是一个基于excel的工具)、TI的WEBENCH(貌似只有FPGA部分,没有ARM部分)、Vivado软件、开发板实测评估等,这几种方案都可以根据自己的外设进行定制,方便灵活。

在低功耗设计之前,需要先进行功耗评估。XPE主要是在项目初期,处于系统设计,RTL代码并未完善阶段功耗估计时使用。在设计完成综合实现后,则可以使用vivado自带的功耗分析工具进行精确计算功耗。打开综合实现后的设计,点击report power即可得到功耗分析的结果。

此部分可以参见之前的文章《Zynq UltraScale+系列之“电源”》。

2.4.1.2、功耗优化

关于FPGA低功耗设计,可从两方面着手:一是算法优化;二是FPGA资源使用效率优化。

算法优化

算法优化可分为两个层次说明:实现结构和实现方法。首先肯定需要设计一种最优化的算法实现结构,设计一种最优化的结构,使资源占用达到最少,当然功耗也能降到最低,但是还需要保证性能,使FPGA设计在面积和速度上都能兼顾。比如在选择采用流水线结构还是状态机结构时,流水线结构同一时间所有的状态都在持续工作,而状态机结构只有一个状态是使能的,显而易见流水线结构的功耗更多,但其数据吞吐率和系统性能更优,因此需要合理选其一,使系统能在面积和速度之间得到平衡。

另一个层面是具体的实现方法,设计中所有吸收功耗的信号当中,时钟是罪魁祸首。虽然时钟可能运行在100MHz,但从该时钟派生出的信号却通常运行在主时钟频率的较小分量(比如12%~15%)。此外,时钟的扇出一般也比较高。这两个因素显示,为了降低功耗,应当认真研究时钟。首先,如果设计的某个部分可以处于非活动状态,则可以考虑禁止时钟树翻转,而不是使用时钟使能。时钟使能将阻止寄存器不必要的翻转,但时钟树仍然会翻转,消耗功率。其次,隔离时钟以使用最少数量的信号区。不使用的时钟树信号区不会翻转,从而减轻该时钟网络的负载。

资源使用效率优化

资源使用效率优化是使用FPGA内部的一些资源(如BRAM,DSP slice)时,可以优化功耗的方法。FPGA动态功耗主要体现为存储器、内部逻辑、时钟、I/O等的功耗。

其中存储器是功耗大户,如xilinx FPGA中的存储器单元Block RAM,因此主要介绍对BRAM的一些功耗优化方法。

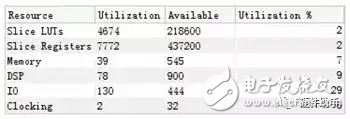

下图中虽然BRAM只使用了7%,但是其功耗0.614W占了总设计的42%,因此优化BRAM的功耗能有效地减小FPGA的动态功耗。

下面介绍一下优化BRAM功耗的方法:

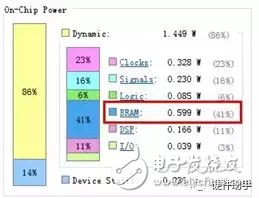

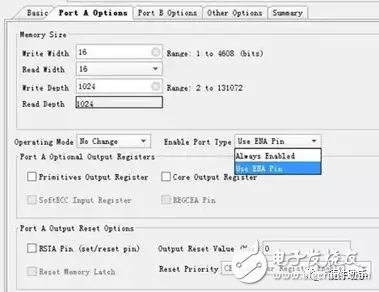

使用“NO CHANGE”模式:在BRAM配置成True Dual Port时,需要选择端口的操作模式:“Write First”,“Read First” or “NO CHANGE”,避免读操作和写操作产生冲突,如图6所示;其中“NO CHANGE”表示BRAM不添加额外的逻辑防止读写冲突,因此能减少功耗,但是设计者需要保证程序运行时不会发生读写冲突。

设置成“NO CHANGE”后BRAM的功耗从0.614W降到了0.599W,因为只使用了7%的BRAM,如果设计中使用了大量的BRAM,效果能更加明显。

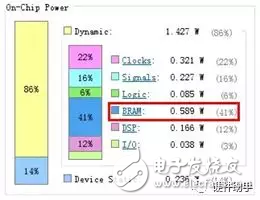

控制“EN”信号:BRAM的端口中有clock enable信号,在端口设置中可以将其使能,模块例化时将其与读/写信号连接在一起,如此优化可以使BRAM在没有读/写操作时停止工作,节省不必要的功耗。

控制“EN”信号优化后BRAM功耗降到了0.589W。

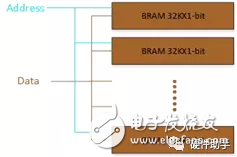

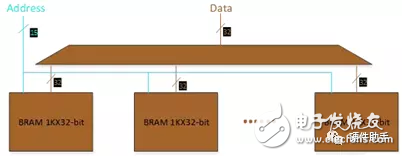

拼深度:当设计中使用了大量的存储器时,需要多块BRAM拼接而成,如需要深度32K,宽度32-bit,32K*32Bit的存储量,但是单块BRAM如何配置是个问题。7 series FPGA中是36Kb 的BRAM,其中一般使用32Kb容量,因此可以配置成32K*1-bit或者1K*32-bit,多块BRAM拼接时,下图中前者是“拼宽度”,后者是“拼深度”。两种结构在工作时,“拼宽度”结构所有的BRAM需要同时进行读写操作;而“拼深度”结构只需要其中一块BRAM进行读写,因此在需要低功耗的情况下采用“拼深度”结构。但需要特别注意的是:“拼深度”结构需要额外的数据选择逻辑,增加了逻辑层数,为了降低功耗即牺牲了面积又牺牲了性能。

3、上下电时序

3.1、上电时序

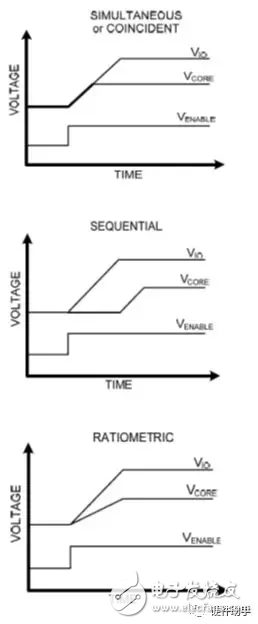

FPGA通常需要多路供电电压,并且要求一定的上电/断电顺序。顺序上电有助于限制上电期间的浪涌电流。如果忽视器件的供电顺序要求,可能导致器件损坏或闩锁,造成FPGA器件故障。有三种类型的上电时序:同步跟踪、顺序跟踪和比率跟踪。

针对各个系列的FPGA芯片,其内部各功能模块的上电时序一般是相互独立的,各个功能模块内部是有先后顺序的要求。详细可参看各个器件的data sheet,其中会有详细的先后顺序约束。

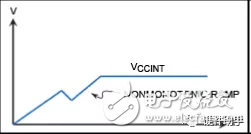

3.2、上升单调性

启动过程中,电源电压保持单调爬升非常重要,只有这样才能确保器件成功开启。一般的FPGA给出了严格的电压单调上升要求,即电源电压应该连续上升至所设置的稳压值,中间不应发生跌落。如果电源不能提供足够的输出功率,则会造成跌落。

3.3、上电时间

大多数FPGA规定了启动电压上升速率的最小值和最大值,电源通过在启动过程中逐渐增大限流值实现软启动。软启动减缓了电源电压的上升速率,也降低了注入FPGA的峰值浪涌电流。一般的电源可利用连接在引脚的软启动电容设置软启动时间。

3.4、掉电时序

断电时序也是需要控制的,标准的时序是把上电时序倒过来。

3.5、特殊情况的时序控制

经常会有FPGA和ARM等其他CPU互连的情况,为了不损坏器件,此时FPGA和ARM的上电时序既要满足自身的上电时序要求,也要满足对方的上电时序要求,这种情况可以进行如下处理:

当FPGA和ARM各自使用自己的配置文件时:由于ARM处于复位状态时IO为输入状态,而FPGA需要完成配置后才能确定其IO的状态,因此ARM和FPGA可以各自进行各自的上电时序,当ARM的上电时序完成后处于复位状态,这样IO为输入状态,当FPGA上电完成后进行配置,配置完成后给ARM一个配置完成信号,此信号去释放ARM的复位,设置对应的IO状态,就不会出现IO冲突了,也不会影响FPGA启动时序,也不会导致FPGA接口出现闩锁效应。

当FPGA是使用ARM给配置文件时,不会出现IO冲突的情况,因为FPGA释放复位,进行配置之前,IO是高阻态,FPGA没有配置文件,不会去设置IO状态。

4、电源方案

目前针对FPGA的常用电源解决方法包括使用单路LDO、单路DC/DC、单颗Power Module、PMIC等。

4.1、LDO

如果电路板空间有保证,低输出噪声很重要,或者系统要求对输入和瞬态现象快速响应,就应该采用LDO。LDO提供了中低输出电流。输入电容通常会切断输入至LDO的阻抗和噪声。LDO还要求在输出端有一个电容器,以处理系统瞬态响应并提供稳定性。

4.2、SMPS

当设计效率非常关键且系统要求大输出电流时,开关电源具有优势。开关电源提供比LDO更高的效率,但其开关特性使其对噪声更敏感。与LDO不同,开关电源需要使用电感器,而且可能需要变压器进行DC-DC转换,对PCB空间需求较大。

4.3、Power Module

Power Module可以省去自己搭建外围电路,且厂家设计的模块一般比自己设计的性能会更好(效率更高、纹波更小),但电源模块一般是在电流需求比较大的情况下会选择。

4.4、PMIC

由于FPGA的广泛应用,目前针对FPGA的专用PMIC越来越多,从输出电压、通道数、输出电流等方面都能很好的满足特定FPGA芯片的需求,同时PCB占用面积、设计便捷性、价格等方面都比较有优势。ZU+ MPSoC系列可参见之前的文章《Zynq UltraScale+系列之“电源”》,其他系列类似,详细可以参见TI、Infineon、ADI(含凌特)等厂家官网,有相关FPGA系列芯片对应的解决方案。

以上就是针对Xilinx FPGA的电源介绍,主要包括了电源的种类、电压要求、功耗分析、上下电时序、电源实现方式等。

-

XILINX FPGA IP之Clocking Wizard详解2023-06-12 9391

-

Xilinx FPGA的电源设计和实现方案2022-10-17 12408

-

采用TPS650250的Xilinx Spartan 6 FPGA电源参考设计2022-09-06 1225

-

用于Xilinx FPGA Zynq7的电源解决方案2022-09-05 983

-

简化Xilinx FPGA的电源系统设计2022-08-05 1860

-

Xilinx FPGA电源TI解决方案(1)2018-08-22 4616

-

Xilinx FPGA电源TI解决方案(2)2018-08-21 3505

-

适用于Xilinx新型FPGA的电源解决方案(3)2018-08-20 3786

-

Xilinx+ISE使用详解2018-01-12 10911

-

Xilinx系列FPGA芯片IP核详解2017-06-06 31352

-

Maxim为三款Xilinx FPGA参考设计提供电源管理方案2017-02-10 1443

-

Maxim成为下一代Xilinx UltraScale FPGA电源方案供应商2014-09-11 1600

-

TI将数字电源管理应用于Xilinx FPGA设计2009-10-30 739

全部0条评论

快来发表一下你的评论吧 !