M24LR64-R:13.56 MHz双接口EEPROM开发方案

可编程逻辑

1390人已加入

描述

关键词: eeprom , M24LR64-R , 接口

ST公司的M24LR64-R是无线存储器,具有口令保护的64kbits EEPROM以及400kHz I2C串行总线和13.56MHz ISO 15693 RF协议的双接口的64kbits EEPROM,可实现智能手机的近场通信(NFC)。单电源1.8V~5.5V工作,64kbits EEPROM分成I2C模式的8192B和RF模式的2048bits×32bits,无接触接口和ISO 15693与ISO 18000-3 mode 1兼容,载波频率13.56MHz±7kHz,广泛用于工业和消费类电子产品。文章介绍了M24LR64-R的主要特性,方框图,M24LR64-R单片和多组合参考设计以及双接口EEPROM开发套件主要特性。

2011-12-12 20:20:43 上传

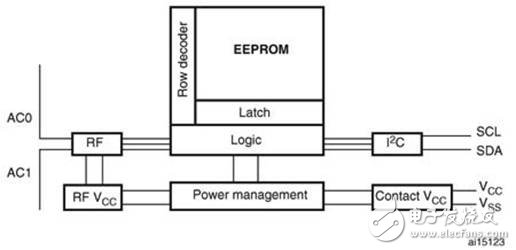

器件M24LR64-R是一款双接口,电可擦除可编程存储器(EEPROM)。它具有一个I2C接口,可从通过VCC电源对其进行操作。它也是一种非接触式内存,由接收到的载波电磁波供电。

图1 M24LR64-R方框图

2011-12-12 20:20:43 上传

下载附件 (7.09 KB)图2 ANT1-M24LR-A参考设计框图

M24LR64-R在I2C模式下为8192位×8位,在ISO15693和ISO18000-3模式,1RF时,为2048×32位。I2C采用两线串行接口,包括双向数据线与时钟线。该器件内置了一个符合I2C总线定义的4位器件类型识别码(1010)。

该器件作为I2C协议的从机,所有的内存操作由串行时钟进行同步。读写操作都是由一个启动条件启动,该条件由总线主机产生。启动条件之后是器件选择码与读/写码(R/W),并由应答位(acknowledge bit)终止。

当数据写入内存时,该器件在总线主机的8位传输后,在第九位传输期间,插入一个应答位(acknowledge bit)。当总线主机读取数据时,总线主机以同样的方式确认收到数据字节。在写入信号的Ack与读取信号的NoAck后,数据传输被停止条件中止。在ISO15693/ISO18000-3模式的1 RF模式中,M24LR64-R是由13.56MHz载波的电磁波进行访问的,其传入的数据是由接收到的信号调幅进行解调的(ASK:幅移键控)。收到的ASK波是10%或100%调制的,采用1/256脉冲编码模式时,数据传输速率为1.6 kbits/s,或者采用1/4脉冲编码模式时,数据传输速率为26 kbits/s。

M24LR64-R的负载变化产生的传出数据采用曼彻斯特编码(Manchester coding),其有一个或两个频率在423 kHz~484 kHz之间的副载波频率。数据由M24LR64-R传送(6.6 kbits/s的低数据率模式和26kbit/s的高数据率模式)。M24LR64-R还支持速率为53kbits/s高数据传输率模式,其副载波频率为423kHz。M24LR64-R的射频功率和信号接口与ISO15693和ISO18000-3模式1建议一致。

M24LR64-R 主要特性

I2C接口

•两线I2C串行接口支持400kHz协议

•单电源电压:

- 1.8 V ~ 5.5 V

•字节和页写入(最多为4个字节)

•随机和顺序读出模式

•自定时编程周期

•自动地址递增

•增强的ESD/闩锁保护

非接触式接口

• ISO 15693和ISO18000-3模式1兼容

• 13.56MHz±7kHz载波频率

•传入标签时:10%或100%ASK调制,使用1/4(26kbits/s)或1/256(1.6 kbits/s)的脉冲位置编码

•从标签传出:负载调制采用曼彻斯特编码(Manchester coding),有 6.6kbits/s的低传输速率或26kbits/s的高传输速率两种模式,其副载波频率在423 kHz~484kHz之间。支持数据传输速率为53 kbits/s的快速命令。

•内部调谐电容:27.5pF

• 64位的唯一标识符(UID)

•读出块及书写(32位块)内存

• 64 kbits的EEPROM,分为:

- I2C模式下8192字节

- RF模式下的32位2048块

•写入时间

- I2C:5ms(最大值)

- 射频:5.75 ms包括内部验证时间

•超过100万的写周期

• RF模式时有多重密码保护

• I2C模式为单一密码保护

•超过40年的数据保持

•封装

- ECOPACK2(符合RoHS且无卤素)

M24LR64-R多组合参考设计

M24LR64-R多组参考设计描述和设置

M24LR64-R多组参考设计的推出可帮助用户提高其双接口EEPROM的存储器密度,将大限度地减少天线的尺寸与PCB上的I2C接口占位。

其基本原理是,在同一I2C总线(符合I2C规范的规定)上,并行连接几个M24LR64-R器件,且它们共享一个单个天线。

ANT5-M24LR的参考设计包括了四个并行的M24LR64-R器件,组成了256kbits的等效用户内存。等效调谐电容值是单个M24LR64-R器件的4倍。因此,无论天线是设计在PCB上或使用SMD电感,其天线比单一M24LR64-R器件的小4倍。

2011-12-12 20:20:43 上传

下载附件 (15.24 KB)图3 ANT5-M24LR-A参考设计框图

2011-12-12 20:20:43 上传

下载附件 (9.94 KB)图4 M24LR64-R双接口EEPROM开发套 件外形图

M24LR64-R双接口EEPROM开发套件:

DEVKIT M24LR-A是ST双接口EEPROM产品的开发工具包,可以使系统设计人员评估I2C和RF的性能和M24LR64-R的功能。

利用ISO15693 13.56 MHz RF读写器可以开发射频应用。

双接口EEPROM开发套件主要特性:

•具有USB总线接口的中等范围射频读写器(ISO 15693,RF 13.56 MHz)

•外部RF读写器天线

•具有USB总线接口的串行EEPROM USB读写器

• ANT1-M24LR-A天线参考板

•连接串行EEPROM USB读卡器和ANT1-M24LR-A的I2C电缆,

•外部电源供电

•安装CD-ROM,包括

-技术文档

- PC适应的安装软件

详情请见:

GEC

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

-

Maxim安全RFID方案,内置13.56MHz接口,支持全球范围的门禁控制2011-09-22 5057

-

如何通过ST NFC Tap iPhone应用程序来识别M24LR64E-R2019-07-18 2728

-

请问我可以将M24LR04E-R 64位UID用于EUI-64地址吗?2019-07-23 1302

-

启用M24LR16E-R能量收集器2019-08-05 2421

-

M24LR16E-R双EEPROM信息可能互相作用吗?2019-08-12 1724

-

请问M24LR64-R的器件地址是什么?2019-08-13 2256

-

M24LR-DISCOVERY SW怎么实现?2019-08-22 1964

-

基于M24LR64-R的数据记录和事件记录器STEVAL-IPR002V22020-05-21 1156

-

用于STM32 Nucleo基于M24LR04E的动态NFC标签IC扩展板2020-06-01 962

-

M24LR04E-R EEPROM如何在收发器和MatLab之间建立通信?2023-02-03 495

-

意法半导体推出双接口串行接口EEPROM存储器M24LR642010-03-20 1420

-

向您介绍 ST 双口 EERPOM M24LR 探索套件2018-06-22 4006

-

微雪电子M24LR-DISCOVERY开发板简介2019-12-30 2940

-

UM0925_使用M24LR64-R数据记录器参考设计的说明手册2022-11-22 397

-

M24LR64E-R:动态NFC/RFID标签IC的全面解析2025-12-17 102

全部0条评论

快来发表一下你的评论吧 !