对于选择同步化的异步复位的方案

FPGA/ASIC技术

211人已加入

描述

随着FPGA设计越来越复杂,芯片内部的时钟域也越来越多,使全局复位已不能够适应FPGA设计的需求,更多的设计趋向于使用局部的复位。本节将会从FPGA内部复位“树”的结构来分析复位的结构。

我们的复位线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束可能造成的时序问题,因为全局网络的延时较大,并且不可以直接连到寄存器的复位端。仍然需要局部走线,这对于时序要求紧张的场合,较难满足时序;二是会占用全局时钟资源,多个复位信号会占用更多的全局时钟资源。

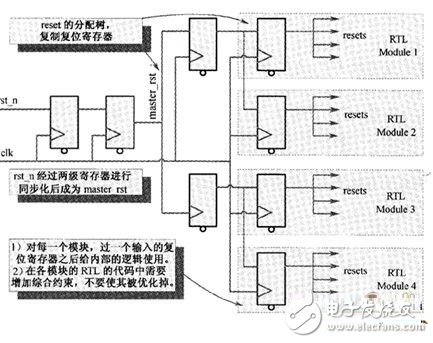

在这里提出一个区域化复位的方案,如图1所示。外部的异步复位信号被二级寄存器同步化之后,复制不同的复位寄存器连到不同的模块来作为复位控制。如果单个模块的复位扇出太大的话,还可以在模块内部复制复位寄存器。强烈建议那些在datapath上不需要复位的寄存器不要在代码中复位,因为这样会增加复位信号的扇出,并增加逻辑资源和降低逻辑速度。

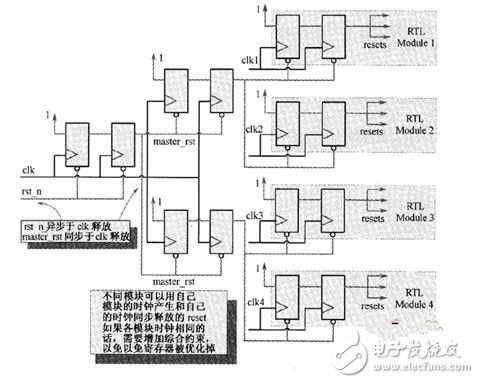

对于那些有多个时钟区域,需要多个时钟区域内独立复位的设计由多个同步化的寄存器的模块来完成同步,然后送到各模块进行复位。

当然,对于选择同步化的异步复位的方案,也可以如图2所示来安排复位。将复位信号转换成同步后送到不同的模块,在各模块中进行同步化处理,各模块完成自己的本地复位。

图1模块化复位

图2 同步化异步复位之模块化复位

综合本节说明的复位路径设计,推荐采用局部复位,即各模块或多个模块采用自己的独立复位信号。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA学习-异步复位,同步释放2023-09-09 2205

-

同步复位与异步复位的区别2023-08-14 8563

-

异步复位同步释放有多个时钟域时如何处理 异步复位同步释放的策略2023-07-20 2776

-

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?2023-06-21 2269

-

【FPGA】异步复位,同步释放的理解2022-01-17 657

-

详细讲解同步后的复位是同步复位还是异步复位?2021-04-27 5614

-

同步复位和异步复位电路简介2019-08-12 8224

-

FPGA全局复位及局部复位设计分享2019-05-17 3387

-

Xilinx FPGA的同步复位和异步复位2018-07-13 7574

-

同步复位和异步复位的比较2018-07-03 1883

-

FPGA设计中的异步复位同步释放问题2018-06-07 2559

-

如何区分同步复位和异步复位?2018-04-24 7921

-

同步复位和异步复位的比较(转载)2016-05-05 10288

-

同步复位sync和异步复位async2011-11-14 6908

全部0条评论

快来发表一下你的评论吧 !