试用手记:为国产FPGA正名(四,时序工具)

可编程逻辑

描述

关键词: FPGA , 国产 , 国产FPGA , 试用

作者在:特权同学

2011-5-25 11:42:12 上传

关于时序工具的一些FAE解答:

问:你们的工具是否只提供所有输入输出管脚完全一致的时序约束?如tsu,th,tco,tpd的约束?如果不同管脚可以有不 同约束值,如何设置?

FAE:我们的工具提供的是时序分析功能,尚未提供时序约束功能,也就是说可以根据您输入的值作为参考,计算出当前实现的各种时序信息与参考值的差距,但并不会根据输入的值去做优化,所以也就不存在对不同管脚分别设置约束的功能了。

问:tco是指reg2pin的延时约束,tpd是指pin2pin的约束。而输入管脚约束tsu和th值,具体含义我不是很 明白?比如说我希望输入管脚的pin2reg延时为0-10ns,那么tsu和th如何设置?

FAE:tsu就可以理解为pin2reg的延时,它是信号从pin到FPGA内部第一个reg相对于这个reg的clock的setup time,而th就是相对这个clock的hold time,th一般不会有问题,需要关注的是tsu。

问:我尝试用GUI做了一些时序约束,然后每次做时序分析都报错:Error: T2000: (ice_run_sta) Run sta failed. 这是什么问题?

FAE:您的这个错误一般是sta设置上有什么问题,得具体分析工程。

今天终于拿到了最新3.2版本的软件,安装后,进行编译,长达近10分钟的placement让我眉头紧皱。后来从FAE处得知我拿到的是还未 release出来的中间版本,有问题在所难免。不说这个,回到主题上来,其实总感觉有些遗憾。FAE在之前的回答其实已经预示着这个国产FPGA与特权同学缘分已到尽头。

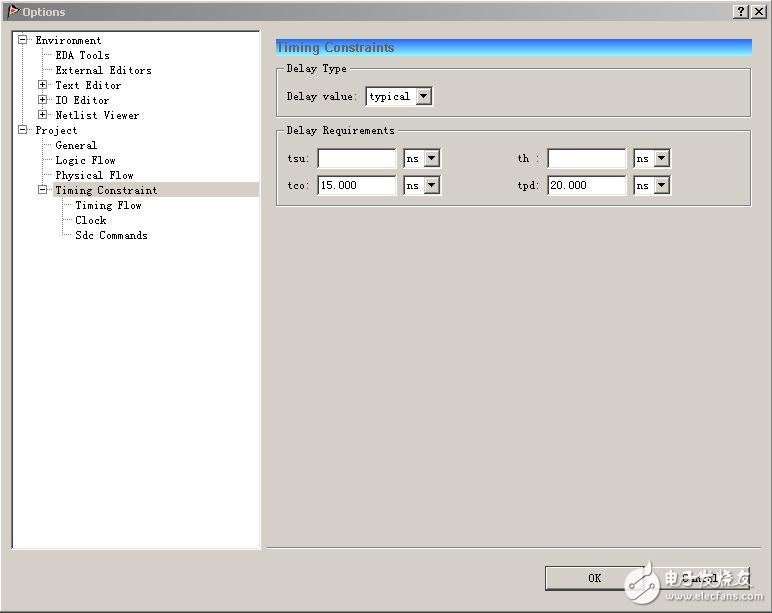

WHY?他们提供的时序分析工具根本算不上真正的时序分析工具,或者这么说,这个所谓的时序分析工具只能提供分析,而无法进行时序的约束和优化。即便他们的工程设置中也提供了如图1的恐怕可以称得上是最简单的“时序约束”,但这个所谓的“时序约束”其实并没有任何“约束”的作用。安装“官方”的说法,它不能够对综合乃至布局布线起到任何影响,而不过是给报告中的路径划了一条水平线,报告中确实能够体现出水平线上或下的状态。

图1

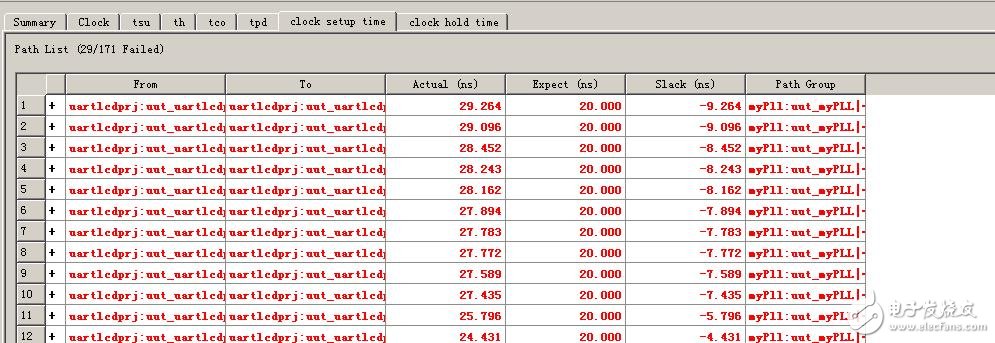

如图2所示,很无奈的只是移植了一个SDRAM控制器外加一些其它逻辑,占去了总共1000个LE中80%的资源,然后只是约束了一个50MHz的工作时钟,结果出来了20条false路径。即便尝试去试试用提供的仅有几个对mapping或palcement&routing设置的优化,结果换来了更多的false。FAE也坦言,目前只能做些简单的逻辑,跑个SDRAM等稍复杂的逻辑也就只能跑个二三十兆的样子。

2011-5-25 11:42:13 上传

下载附件 (96.26 KB)图2

几天的试用,虽然以国产FPGA的性能问题而告夭折。虽然还显稚嫩的开发工具、差强人意的器件性能多少让人有些失望,但至少从某种程度上让特权同学改变了对国产的一些偏见。其实,如果Agate Logic能够持续这种开发热情,不断的改进,假以时日,相信他们会成为“中国的Altera”、“中国的Xilinx”。

- 相关推荐

- 热点推荐

-

【国产FPGA入学必备】国产FPGA权威设计指南+配套FPGA图像视频教程2025-02-20 13803

-

FPGA设计之时序约束2022-03-18 2147

-

关于FPGA时序工具的一些FAE解答2021-10-12 3844

-

【EG4S20-MINI-DEV 试用体验】使用注意点+软件改进建议+时序分析工具试用2019-07-03 2562

-

为国产FPGA正名(六,完结篇)2019-02-25 385

-

基于FPGA时序优化设计2017-11-18 3826

-

在FPGA设计中,时序就是全部2017-02-09 508

-

80W纯四类功放制作手记2016-03-10 1244

-

FPGA设计:时序是关键2014-08-15 1472

-

工程师手记:FPGA学习的四大误区2012-08-17 12062

-

魅族Miniplayer SL版全功能使用手记2010-02-01 1880

全部0条评论

快来发表一下你的评论吧 !