试用手记:为国产FPGA正名(一)

可编程逻辑

描述

关键词: FPGA , 国产 , 国产FPGA , 试用

作者:特权同学

2011-5-25 11:30:58 上传

印象中FPGA市场基本是Altera和Xilinx一统天下,他们的明争暗斗决定着FPGA的未来,甚至他们各自的家族产品都是对着干的。Lattice、Actel、Atmel各有其小众市场,再有别的厂商,基本上特权同学是不太叫得上来了。

国产FPGA?是不是听错了,没有。记得第一次听说 FPGA前面加了个定冠词“国产”应该可以追溯到特权同学还和价格堪比年薪的军品纠结的岁月。不过那个“国产”二字总感觉和“盗版”谐音,真的不是损谁,只是实事求是的说。也许这种模式也叫“中国特色”吧,好歹比那天忘了在哪位大侠博客看到的“二次包装”的“中国制造”强上千百倍。Xilinx早期的 XC4打头的FPGA,也只有ISE4以前的版本支持,“低端”军品也就这几款了。所以国内的XX所也很牛,居然能够逆向设计将他们的“国产”FPGA做得和它完全兼容,不止是PIN2PIN,甚至连开发工具他们都不用徒手打造了,告诉我们完全替代现有的Xilinx器件。

有时候不得不感叹,中国人很牛。外国人可以做到的,基本上没有中国人做不到的。时光荏苒,特权同学已不再需要靠那些“可靠”换“性能”的片子干活了。而FPGA的成本却越来越成为产品开发中挥之不去的梦魇,于是乎,老板想尽办法要压榨FPGA的成本,这次找来了又一个“国产”准备在低端低成本的应用中大干一场。不过几番观察下来,特权同学开始对此“君”颇有好感,它也许算不上真正意义上的“国产”,但是多少让人感受到了它走的是一条“正规”有“前途”的路子。

其实也只是昨天才开始正式的和这家名为Agate Logic的FPGA厂商有了一些“亲密”接触。它的开发工具,它的开发流程,它的主打芯片结构、特点、性能都有所了解,但要真*实弹的用这个家伙干活,还得有更深入的尝试和验证。特权同学希望对这些尝试做些记录,也许,是一次蛮有意思的尝试。

今天先简单的没主题的随便扯谈吧。首先,这家公司是提供了两个系列的产品,其中一个系列工艺先进些,据说性能好一些,只不过年初刚量产,还不是主推产品,姑且不详谈,毕竟特权同学的DEMO板上的主角儿也不是它。另一个低端点的系列叫Astro,别小看它了,先罗列一下参数大家瞧瞧。

★ 硬核——可以跑到100MHz的8051硬核,标准外设IIC一个、SPI一个、USART两个、定时器数个。

★ 1Mbit一次性可编程存储(OTP)——加密的利器啊。

★ 1个PLL——3个可选输出,相位可调。

★ 可选的内部4Mbit FLASH。

★ 2个9Kbit可配置存储器——虽然对于片内存储要求很高的特权同学有点“巧妇难为无米之炊”了,不过低端应用牺牲一些“性能”还是可以接受的。

有这些东西还不算,最主要的还是它保持着传统“中国特色”的“便宜”,基本上3个美金可以拿到有1024个LUT的器件了。若是要和当前的Altera相关解决方案比比,那真得是蛮有竞争力的。MAX II系列CPLD除了逻辑真得没有别的用处了,而逻辑资源逊色不少的EPM570(EPM1270不说了)目前市场上估计是有缺货的因素,居然卖到30好几个RMB了。而如果选择Cyclone系列最便宜的EP1C3好像也只要30多RMB,但是要跑个最经济的NIOS也有点困难。而且有个很有意思的现象,正规代理商会很无奈的告诉你这样的老器件要30的数倍价格才能搞到,而外面的小商小贩卖的就是30的准“白菜价”(当然不排除买到“散新货”的可能)。而Astro却连配置器件和外挂MCU的成本都省了,虽然它也是基于SRAM的结构。(不行,越比发现这东西越好。先申明一下,这里不是推销,只是比较,特权同学是用芯片的,不是卖芯片的。嘿嘿)

今天花了一上午把它们的开发工具Primace的 Help过了一遍。再说个题外话,昨天到它们的上海办事处,感觉上这般人对版本的管理不是很好,动不动来一个版本,让我们当时一个版本装另一个版本卸的来回折腾好几次才看到Primace的本来面目。还有那个USB下载线,MCU要一个JTAG,FPGA也要一个JTAG,如果能二合一的干活多好啊,就像咱的NIOS2。

FPGA开发,确切的说硬件系统的开发都是有赖于 Primace的,软件是KEIL,它们提供了一套接口,用上去还算方便。这个Primace整个一ISE或者Quartus II的简化版,毕竟也是刚起步,勉强可以接受,怎么说咱当年在ISE10大行其道的年代也有过被迫无奈“玩转”ISE4的经历。

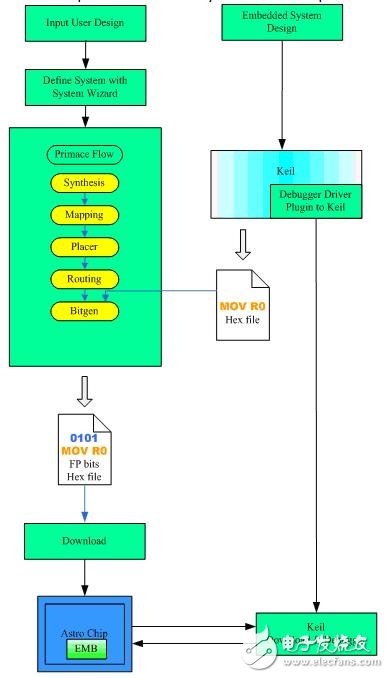

截个图,如图1,它们的开发流程也算是软硬兼施,FPGA的流程很简化,看上去很“清爽”。最终把FPGA配置文件bitgen和KeilC的Hex一起在软件里生成个新文件下载就行。

图1

开发工具真的很“简陋”。时序约束和分析特权同学还没摸懂怎么回事,就那么两三个GUI选项,只能说是比Classic timing analyzer还Classic,这一点是特权同学最担忧的;提供的板级调试手段也很有限,好像就一个称为Signal monitor的家伙,没有尝试,就不妄下定论,好在本来它的逻辑资源也不多,调试起来有没有在线手段也无关紧要。

- 相关推荐

- 热点推荐

-

国产FPGA的发展前景是什么?2024-07-29 7932

-

国产高端fpga芯片有哪些2024-03-15 4257

-

国产FPGA都有哪些厂商?2023-12-12 7238

-

【免费试用】紫光同创PGL50H开发平台,高性能国产FPGA,盘古50K开发板试用活动火热征集中!2023-08-21 1799

-

STM32开发手记,更新中2021-11-20 579

-

【MYMINIEYE Runber蜂鸟开发版免费试用连载】国产FPGA试用评测之MYMINIEYE Runber蜂鸟开发板2020-07-16 1831

-

【EG4S20-MINI-DEV 申请】国产FPGA开发环境评测2019-06-24 1774

-

为国产FPGA正名(六,完结篇)2019-02-25 384

-

工程师手记:FPGA学习的四大误区2012-08-17 12061

-

魅族Miniplayer SL版全功能使用手记2010-02-01 1876

-

为输变电工程电磁影响正名2008-11-20 921

全部0条评论

快来发表一下你的评论吧 !