SK Hynix详细介绍自家基于DDR5规范的同步DRAM芯片

电子说

描述

尽管 JEDEC 尚未完成 DDR5 最终标准的开发,但芯片大厂之间早就开始了暗自较劲。在旧金山举办的国际固态电路会议(ISSCC)上,SK Hynix 首次详细介绍了自家基于 DDR5 规范的同步 DRAM 芯片。作为同样来自韩国的竞争对手,三星在同一会议上描述了基于低功耗 LPDDR5 规范的 DSRAM 作为反击。

与当前已面世的 DDR4 标准对比,DDR5 能够提供双倍的带宽密度,以及更高的通道效率。原定于去年完成的 DDR5 标准,现仍在持续中,预计相关产品会在今年年底开始出现。

在周三的国际固态电路会议上,海力士芯片设计师 Dongkyun Kim 发表了自家首款 DDR5 芯片的报告。

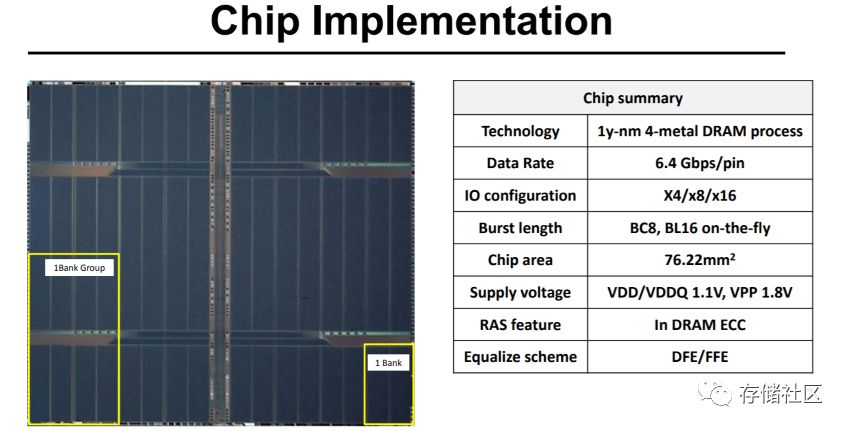

“这是一款 16Gb @ 每引脚 6.4Gbps 的 SDRAM,工作电压 1.1V 。制造节点为 1y 纳米,基于四金属 DRAM 工艺,封装面积 76.22 平方毫米。”

Kim 对延迟锁定回路的部分改动进行了深入讲解,表示 Hynix 借助了相位旋转器和注入锁定振荡器,实现了对延迟锁定环(DLL)的修改。以减少在较高时钟速度下,操作相关的时钟抖动和占空比失真。

“他还描述了海力士设计团队使用的其它技术,包括用于抵消与更高速度相关的时钟域问题的写入等级训练方法,以及改进的前向反馈均衡(FFE)电路。”

与此同时,三星公司描述了一款 10nm 级别的 LPDDR5 SDRAM 。在低至 1.05V 的电压下,它可以达到 7.5 Gb/s 的速率。

“JEDEC 在本周早些时候发布了 LPDDR5 标准,最终定下的标准 I/O 运行速率为 6400 MT/s,较 LPDDR4时代提升了 50% 。”

如此一来,业界有望大幅提升智能手机、平板电脑、以及超极本等应用场景下的内存速度和效率。此外,Objective Analysis 首席分析师 Jim Handy 披露了三星 LPDDR5 新品的更多技术细节。

-

Introspect DDR5/LPDDR5总线协议分析仪2024-08-06 4855

-

SK海力士研发完成基于1Ynm工艺的DDR4 DRAM芯片2018-11-13 8560

-

SK海力士发布标准DDR5 DRAM内存颗粒 并拥有最多32个Bank2018-11-17 5582

-

SK海力士详细介绍16Gb DDR5 新一代DRAM将重振内存市场2019-10-29 4609

-

SK Hynix展示DDR5存储器模组,支持DDR5的硬件预计明年推出2020-01-15 4111

-

大多DRAM厂商DDR5相应产品发售,DDR5能成为市场的主流吗2020-03-01 3721

-

SK海力士DDR5内存可到128GB2020-04-03 3665

-

SK海力士首推DDR5内存,容量可达256GB2020-10-08 8828

-

全球首款64GB DDR5 RAM:未来将成为个人电脑实际标准2020-10-20 4808

-

Meta、英伟达相继拜访SK海力士,要求额外供应DDR5/HBM2023-08-30 1580

-

三星电子和SK海力士计划四季度全面提高DDR5产量2023-10-24 1027

-

SK海力士DDR5芯片价格或将大幅上涨2024-08-14 1755

-

DRAM大厂第三季DDR5价格大幅上调2024-08-21 1419

-

DDR4涨价20%,DDR5上调5%!2025-05-13 7801

-

DDR5 设计指南(一):DDR5 VS LPDDR52025-10-27 11600

全部0条评论

快来发表一下你的评论吧 !